인터럽트

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

인터럽트는 하드웨어 또는 소프트웨어 이벤트에 대한 응답으로 발생하는 신호로, CPU의 작업 흐름을 중단시키고 특정 작업을 수행하도록 하는 기술이다. 하드웨어 인터럽트와 소프트웨어 인터럽트로 분류되며, 하드웨어 인터럽트는 외부 장치의 신호에 의해, 소프트웨어 인터럽트는 CPU 내부의 명령이나 조건에 의해 발생한다. 인터럽트 컨트롤러는 여러 장치의 인터럽트 요청을 관리하고 우선순위를 결정하여 CPU에 전달하는 역할을 한다. 인터럽트 처리에는 오버헤드가 발생하며, 과도한 인터럽트 처리는 시스템 성능 저하를 유발할 수 있다. 인터럽트는 타이머 서비스, 데이터 전송, 키보드 및 마우스 이벤트 처리 등 다양한 분야에 활용되며, 특히 실시간 서비스의 발전에 중요한 역할을 한다. 다중 프로세서 시스템에서는 IPI를 통해 프로세서 간 인터럽트 요청을 보낼 수 있으며, 멀티코어 프로세서 환경에서는 RSS, RPS, RFS 등의 기술을 통해 인터럽트 처리 성능을 향상시킬 수 있다.

더 읽어볼만한 페이지

- 인터럽트 - 프로그래머블 인터럽트 컨트롤러

프로그래머블 인터럽트 컨트롤러(PIC)는 컴퓨터 시스템에서 인터럽트 요청을 관리하며, 인터럽트 요청 레지스터 등을 사용하여 인터럽트를 처리하고 다양한 우선순위 체계를 지원하며, x86 아키텍처에서는 인텔 8259가 널리 사용되었다. - 인터럽트 - 도스 API

도스 API는 응용 프로그램이 MS-DOS 운영체제의 시스템 기능을 사용하도록 제공되는 인터페이스로, CP/M 호환성을 고려한 초기 설계 이후 유닉스 개념 도입, 네트워크 기능 추가 등으로 확장되었으며, 다양한 운영체제에서 에뮬레이터를 통해 지원된다. - 마이크로컨트롤러 - 마이크로프로세서

마이크로프로세서는 CPU 기능을 단일 IC에 통합한 것으로, 무어의 법칙에 따라 성능이 향상되어 왔으며 다양한 아키텍처와 기술 발전을 거쳐 현재 광범위한 분야에서 사용된다. - 마이크로컨트롤러 - ARM 아키텍처

ARM 아키텍처는 저전력 설계로 모바일 기기에서 널리 쓰이는 RISC 기반 프로세서 아키텍처로서, IP 코어 라이선스 모델과 ARM Flexible Access를 통해 다양한 분야로 확장되고 있다. - 컴퓨터 구조 - PA-RISC

PA-RISC는 휴렛 팩커드에서 개발한 RISC 기반 명령어 집합 아키텍처로, HP 서버 및 워크스테이션에 사용되었으며 대용량 L1 캐시와 SIMD 명령어 확장 등의 특징을 가졌으나 아이테니엄 아키텍처로의 전환으로 단종되었다. - 컴퓨터 구조 - 메모리 관리

메모리 관리는 운영체제의 핵심 기능으로, 여러 프로세스의 원활한 실행을 위해 메모리 공간을 할당하고 관리하며, 릴로케이션, 보호, 공유, 가상 메모리 관리, 자동/수동 메모리 관리 등의 기능을 수행한다.

| 인터럽트 | |

|---|---|

| 일반 정보 | |

| |

| 정의 | |

| 종류 | 하드웨어 인터럽트 소프트웨어 인터럽트 |

| 동작 방식 | |

| 발생 | 하드웨어 또는 소프트웨어에 의해 발생 |

| 처리 | 인터럽트 핸들러 또는 인터럽트 서비스 루틴으로 제어 전달 현재 실행 중인 프로세스 일시 중단 인터럽트 처리 후 중단된 프로세스 재개 또는 다른 프로세스 실행 |

| 하드웨어 인터럽트 | |

| 발생 원인 | 주변 장치의 상태 변화 (예: 데이터 준비 완료) 오류 발생 |

| 예시 | 키보드 입력 마우스 움직임 프린터 작업 완료 디스크 드라이브 데이터 전송 완료 네트워크 카드 패킷 수신 |

| 소프트웨어 인터럽트 (Trap) | |

| 발생 원인 | 프로그램 실행 중 예외 상황 발생 (예: 0으로 나누기) 시스템 호출 요청 |

| 사용 목적 | 커널 기능 호출 디버깅 에뮬레이션 |

| 인터럽트 처리 과정 | |

| 인터럽트 요청 (IRQ) | 하드웨어 장치가 CPU에 인터럽트를 요청 |

| 인터럽트 확인 | CPU가 현재 작업을 중단하고 인터럽트 요청을 확인 |

| 인터럽트 벡터 테이블 (IVT) | CPU는 IVT에서 해당 인터럽트에 대한 인터럽트 핸들러 주소를 찾음 |

| 인터럽트 핸들러 실행 | CPU는 해당 인터럽트 핸들러를 실행하여 인터럽트 처리 |

| 인터럽트 복귀 | 인터럽트 핸들러가 완료되면 CPU는 중단된 작업으로 복귀 |

| 인터럽트 컨트롤러 | |

| 역할 | 여러 장치의 인터럽트 요청을 관리 인터럽트 우선순위 결정 CPU에 인터럽트 신호 전달 |

| 종류 | APIC (Advanced Programmable Interrupt Controller) PIC (Programmable Interrupt Controller) |

| 장점 | |

| 효율성 | CPU는 I/O 장치가 준비될 때까지 대기하지 않고 다른 작업 수행 가능 |

| 실시간 처리 | 긴급한 이벤트에 즉각적으로 대응 가능 |

| 단점 | |

| 복잡성 | 인터럽트 핸들러 개발 및 디버깅의 어려움 |

| 오버헤드 | 인터럽트 처리 과정에서 발생하는 추가적인 시간 및 자원 소모 |

| 기타 | |

| 관련 용어 | 폴링 DMA (Direct Memory Access) 인터럽트 마스크 인터럽트 벡터 |

2. 역사

UNIVAC 1103A 컴퓨터는 1953년에 인터럽트를 가장 먼저 사용한 것으로 알려져 있다.[5][6] 그 이전 UNIVAC I (1951)에서는 "산술 오버플로가 주소 0에서 두 개의 명령어 수정 루틴 실행을 트리거하거나, 프로그래머의 선택에 따라 컴퓨터를 중지시켰다." IBM 650 (1954)은 인터럽트 마스킹을 처음으로 구현했다. 미국 국립표준국 DYSEAC (1954)는 I/O에 인터럽트를 사용한 최초의 시스템이었다. IBM 704는 분기 명령어가 감지될 때 특수 루틴을 호출할 수 있는 "전송 트랩"을 통해 디버깅에 인터럽트를 사용한 최초의 시스템이었다. MIT 링컨 연구소의 TX-2 시스템 (1957)은 여러 레벨의 우선순위 인터럽트를 제공한 최초의 시스템이었다.[6]

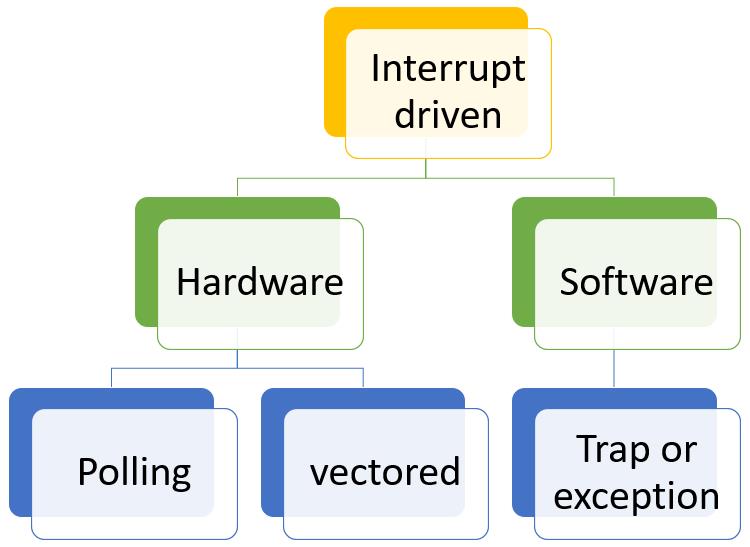

인터럽트는 크게 하드웨어 인터럽트와 소프트웨어 인터럽트로 나뉜다. 하드웨어 또는 소프트웨어 이벤트에 대한 응답으로 발생하며, 특정 프로세서의 경우 인터럽트 유형의 수는 아키텍처에 의해 제한된다.

하드웨어 인터럽트는 외부 이벤트 대기 중 폴링 루프의 비생산적인 대기 시간을 제거하여 최적화의 목적으로 도입되었다. 이 방식을 사용한 최초의 시스템은 1954년에 완성된 DYSEAC였다.[4]

3. 종류

인터럽트의 주요 목적은 다음과 같다.

CPU의 인터럽트는 크게 하드웨어 인터럽트(외부 인터럽트)와 소프트웨어 인터럽트(내부 인터럽트)로 분류할 수 있다. 흔히 "인터럽트"라고 말할 때는 전자를 가리키는 경우가 많기 때문에, 후자를 SWI(SoftWare Interrupt)라고 불러 구분하는 경우가 있다.

인터럽트에는 다음과 같은 종류가 있다.

하드웨어 인터럽트와 소프트웨어 인터럽트에 대한 자세한 내용은 각각의 하위 문서를 참고하라.

3. 1. 하드웨어 인터럽트

하드웨어 인터럽트는 키보드, 마우스와 같은 외부 장치가 CPU에 특정 신호를 보내 발생한다. 이러한 신호는 CPU 클럭과 비동기 통신 방식으로 전달되며, 언제든지 명령어 실행 중에 발생할 수 있다.[7]

많은 시스템에서 각 장치는 특정 인터럽트 요청(IRQ) 신호와 연결되어 있어, 어떤 장치가 서비스를 요청하는지 빠르게 파악하고 처리할 수 있다. 1964년 CDC 3600 같은 구형 시스템에서는 모든 인터럽트가 동일한 위치로 이동했지만,[8] 오늘날 시스템에서는 인터럽트 종류나 소스에 따라 서로 다른 인터럽트 루틴을 사용하며, 인터럽트 벡터 테이블로 구현하는 경우가 많다.

인터럽트를 '마스크'한다는 것은 해당 인터럽트를 비활성화하여 무시하거나 지연시키는 것을 의미하며,[9] '언마스크'는 활성화하는 것을 의미한다. 프로세서는 보통 내부 '인터럽트 마스크' 레지스터를 통해 하드웨어 인터럽트를 선택적으로 활성화 또는 비활성화할 수 있다.[2] 각 인터럽트 신호는 마스크 레지스터의 비트와 연결되며, 시스템에 따라 비트 설정/해제로 인터럽트 활성화/비활성화 여부가 결정된다. 마스크의 영향을 받는 인터럽트를 '마스크 가능 인터럽트'라고 한다.

비마스크 인터럽트 (NMI)는 인터럽트 마스크의 영향을 받지 않아 비활성화할 수 없는 인터럽트이다. 워치독 타이머의 타임아웃 신호처럼 무시할 수 없는 높은 우선순위 이벤트를 나타낸다. SPARC에서는 NMI도 인터럽트 마스크를 사용하여 발생을 방지할 수 있다.[10]

하드웨어 인터럽트의 주요 목적은 CPU 자원 효율을 높이고, 응답성을 향상시키며, 예외 처리를 효율화하고, 정확한 타이밍을 얻는 것이다. 또한, 인터럽트 처리는 인터럽트되는 측의 처리에서 명시적으로 호출할 필요가 없어 투명한 구현이 가능하다.

CPU 인터럽트는 하드웨어 인터럽트(외부 인터럽트)와 소프트웨어 인터럽트(내부 인터럽트)로 나뉜다. 하드웨어 인터럽트는 CPU 외부에서 요청되며, CPU의 인터럽트 요청 단자가 어서트(활성화)되었을 때 발생한다. CPU 인터럽트 요청 단자에는 마스크 불가능 인터럽트(NMI)와 마스크 가능 인터럽트(좁은 의미의 IRQ) 두 종류가 있다. 인터럽트 마스크 설정은 주로 플래그 레지스터에 저장되며, CPU 명령으로 인터럽트 허용/금지를 조작할 수 있다. NMI와 IRQ 단자가 동시에 어서트되면 NMI가 우선 처리된다. 주변기기는 주로 OS 제어를 위해 IRQ 단자에 연결되며, 디버그나 하드웨어 에러 등 특수한 용도에는 NMI가 사용된다.

CPU가 인터럽트를 인식하고 처리한 후, 인터럽트 처리 루틴에서 소프트웨어가 인터럽트를 허가하지 않는 한, 그 이상의 인터럽트가 네스팅되지 않도록 자동 금지하는 CPU 타입과, 인식된 레벨보다 우선순위가 높은 인터럽트에 한해 네스팅을 허용하는 타입(예: PDP-11)이 있다.

3. 1. 1. 인터럽트 요청 방식

레벨 트리거 인터럽트는 인터럽트 신호를 특정 (높음 또는 낮음) 활성 논리 레벨로 유지하여 요청된다. 장치는 신호를 활성 레벨로 구동하여 유지함으로써 레벨 트리거 인터럽트를 호출한다. 일반적으로 장치가 서비스를 받은 후 프로세서가 명령하면 신호를 무효화한다. 프로세서는 각 명령어 사이클 동안 인터럽트 입력 신호를 샘플링한다. 샘플링이 발생할 때 신호가 어설션되면 프로세서는 인터럽트 요청을 인식한다. 레벨 트리거 입력은 여러 장치가 와이어드-OR 연결을 통해 공통 인터럽트 신호를 공유할 수 있도록 한다.

에지 트리거 인터럽트는 인터럽트 라인의 레벨 전환, 즉 하강 에지(높음에서 낮음) 또는 상승 에지(낮음에서 높음)에 의해 신호가 발생되는 인터럽트이다. 인터럽트를 신호하려는 장치는 라인에 펄스를 가한 다음 라인을 비활성 상태로 릴리스한다. 에지 트리거의 중요한 부분은 신호가 인터럽트를 트리거하기 위해 전환되어야 한다는 것이다. 예를 들어, 신호가 높음-낮음-낮음인 경우 하나의 하강 에지 인터럽트만 트리거되며, 계속 낮은 레벨은 추가 인터럽트를 트리거하지 않는다. 추가 인터럽트를 트리거하려면 신호가 높은 레벨로 돌아간 다음 다시 떨어져야 한다. 이는 낮은 레벨이 신호가 높은 레벨로 돌아갈 때까지 인터럽트를 계속 생성하는 (활성화된 경우) 레벨 트리거와는 대조적이다.

하드웨어 인터럽트는 CPU 외부에서 요청되며, CPU의 인터럽트 요청 단자가 어서트(활성화)되었을 때 발생한다. PCI 버스에서는 레벨 트리거 방식의 인터럽트 신호선이 채용되고 있다.

'''IRQ 단자'''의 어서트 방법에는, 신호의 변화점을 검출하는 에지 트리거와, 신호의 레벨로 검출하는 레벨 트리거가 있다. 에지 트리거에는 상승 또는 하강과 같은 한쪽 방향의 변화만을 검출하는 「단일 에지 검출」과, 양쪽 모두를 검출하는 「양쪽 에지 검출」이 있다.

3. 2. 소프트웨어 인터럽트

소프트웨어 인터럽트는 CPU 내부에서 특정 명령을 실행하거나 예외 상황이 발생할 때 일어난다.

CPU 명령(INT, TRAP, RST 등)에 의해 발생하는 소프트웨어 인터럽트는 실행 가능한 처리 범위가 CPU 모드에 의해 제한되는 CPU에서 시스템 호출을 실현하기 위해 사용된다. 예를 들어, 일반적인 애플리케이션이 동작하는 사용자 모드에서는 실행할 수 없는 명령이라도 SWI 후에는 특권 모드로 이행하기 때문에 실행 가능해진다.

'''예외'''는 0으로 나누기, 산술 오버플로, 페이지 폴트 등에 의해 발생하는 예외 처리의 요구이다. 특히 페이지 폴트는 OS가 메모리 공간을 관리하는 데 중요한 역할을 한다.

CPU가 소프트웨어 인터럽트를 위한 명령을 직접 지원하지 않는 경우, 비어있는 하드웨어 인터럽트 요구 단자를 어서트하는 수단을 별도로 마련하여 소프트웨어 인터럽트를 에뮬레이트하는 경우가 있다. 아키텍처에 따라 이 방법을 정식 소프트웨어 인터럽트의 구현으로 하는 경우도 있다.

소프트웨어 인터럽트는 설계상 실행 시 인터럽트를 호출하는 특수 명령어를 실행하여 의도적으로 발생할 수 있다. 이러한 명령어는 서브루틴 호출과 유사하게 작동하며 운영 체제 서비스를 요청하고 장치 드라이버와 상호 작용하는 등 다양한 목적으로 사용된다(예: 저장 매체를 읽거나 쓰기 위해). 프로그램 실행 오류 또는 가상 메모리 시스템에 의해서도 트리거될 수 있다.

일반적으로 운영 체제 커널은 이러한 인터럽트를 포착하여 처리한다. 일부 인터럽트는 프로그램에 투명하게 처리된다. 예를 들어, 페이지 폴트의 정상적인 해결 방법은 필요한 페이지를 물리적 메모리에서 액세스할 수 있도록 만드는 것이다. 그러나 세그먼테이션 오류와 같은 다른 경우에는 운영 체제가 프로세스 콜백을 실행한다. 유닉스 계열 운영 체제에서는 SIGSEGV, SIGBUS, SIGILL 또는 SIGFPE와 같은 신호를 보내는 것이 포함되며, 이는 신호 처리기를 호출하거나 기본 동작을 실행한다(프로그램 종료). Windows에서는 STATUS_ACCESS_VIOLATION 또는 STATUS_INTEGER_DIVIDE_BY_ZERO와 같은 예외 코드를 사용하여 구조적 예외 처리를 사용하여 콜백이 수행된다.[12]

4. 인터럽트 처리 절차

인터럽트가 발생하면 CPU는 현재 실행 중인 작업을 중단하고, 인터럽트 처리를 시작한다. 이때, 실제 처리 코드를 담고 있는 함수를 '''인터럽트 핸들러'''라고 부른다.[46] 인터럽트 핸들러는 마이크로컨트롤러와 같은 간단한 시스템에서는 RETI와 같은 명령어를 통해 빠르게 복귀할 수 있도록 설계된다. 인터럽트 발생 시, 레지스터와 프로그램 카운터를 보관하여 CPU의 상태를 보존하고, 인터럽트 처리가 완료되면 이전 상태로 복귀한다.

인터럽트 종류별로 처리해야 할 인터럽트 핸들러(ISR)의 주소는 '''인터럽트 벡터 테이블'''에 저장되어 있다. CPU는 인터럽트 벡터를 통해 어떤 인터럽트가 발생했는지 확인하고, 인터럽트 벡터 테이블에서 해당 인터럽트 핸들러의 주소를 찾아 실행한다.

인터럽트 처리 절차는 다음과 같다.

1. 하드웨어나 소프트웨어에서 인터럽트 발생.

2. 현재 실행 중인 기계어 코드 중단.

3. CPU의 특수 레지스터 확인 (인터럽트 마스크 비트 확인).

4. 인터럽트 벡터를 읽음.

5. ISR 주소값을 얻음.

6. ISR로 점프 (PC 값은 자동 저장).

7. 현재 프로그램의 레지스터 저장.

8. 인터럽트 핸들러 코드 실행.

9. 인터럽트 처리 완료 후, 저장했던 레지스터 복원.

10. IRET 명령어 실행으로 인터럽트 해제 및 이전 실행 위치로 복귀.

8051 시리얼 어셈블리 언어를 사용한 인터럽트 핸들러 예시는 다음과 같다.[46]

```asm

Serial_ISR:

PUSH PSW ; 스택에 상태 레지스터 대피

PUSH ACC ; 스택에 A(Accumulator) 레지스터 대피

JNB RI,output ; RI 레지스터를 확인하여 수신 여부 확인, 없으면 수신 루틴 점프

MOV A, SBUF ; 데이터 버퍼를 A레지스터로 가져오고

MOV inchar, A ; 문자를 변수 inchar에 저장.

CLR RI ; 수신 플래그를 지우고

output: ; 출력 루틴 시작

JNB TI, done ; 데이터 전송 중인지 확인, 전송 중이면 출력 루틴 점프

MOV A, outchar ; 데이터 변수 outchar 내용을 A레지스터로 옮기고

MOV SBUF, A ; 시리얼 전송 버퍼에 써서 하드웨어가 보내기 시작

CLR TI ; 전송 인터럽트 플래그 지우고

done: ; 종료 루틴

POP ACC ; A 레지스터 복귀

POP PSW ; 상태(플래그) 레지스터 복귀

RETI ; 인터럽트 핸들러 종료

```

위 예시에서 PUSH/POP 명령어는 마이크로프로세서의 레지스터를 대피시켜 기존 루틴에 영향을 주지 않도록 한다. 인터럽트 핸들러는 C언어 함수와 다르므로, 개발 도구에서 제공하는 방법을 숙지하여 코딩해야 한다.

5. 인터럽트 컨트롤러

인터럽트 컨트롤러는 여러 장치에서 발생하는 인터럽트 요청(IRQ)을 관리하고 우선순위를 결정하여 CPU에 전달하는 하드웨어이다. 이 기능을 통해 CPU는 어떤 장치가 인터럽트를 요청했는지 쉽게 파악하고, 해당 장치에 맞는 인터럽트 핸들러를 실행할 수 있다. 인터럽트 컨트롤러는 CPU의 IRQ 단자를 외부에서 확장하여 제어하는 역할을 한다. 마이크로컨트롤러에서는 CPU와 여러 주변 장치가 동일 칩 내에 내장되어 있으며, 인터럽트 컨트롤러도 함께 내장되는 경우가 많다.

대표적인 인터럽트 컨트롤러는 다음과 같다.

- 인텔 8259 (Programable Interrupt Controller, PIC): 인텔 8086 계열의 인터럽트 컨트롤러이다. IRQ 0-7의 8개 인터럽트 단자를 가지며, CPU에 인터럽트 번호를 전달한다. 각 인터럽트마다 마스크와 우선순위를 설정할 수 있다. PC/AT 호환기종에서는 이 기능을 2개 탑재하고 있다.

- Z80 계열: 집중적으로 관리하는 인터럽트 컨트롤러는 존재하지 않으며, 각 주변 장치(Z80 SIO, Z80 PIO, Z80 CTC 등)가 CPU에 인터럽트 벡터를 출력하는 기능을 가지고 있었다. 인터럽트 신호선의 데이지 체인 구성으로 우선 순위를 정한다.

- ARM 프로세서: IRQ와, 더 높은 우선 순위를 가진 "고속 인터럽트"(FIQ)가 있다. FIQ에서는 IRQ에 비해 일부 레지스터를 스택에 넣지 않고 전용 레지스터에 보존하기 때문에 동작이 빠르다.[34]

6. 인터럽트 처리의 오버헤드

인터럽트 처리에는 CPU의 레지스터 저장/복원 및 프로세서의 특권 레벨 전환 처리 등, 적지 않은 처리 오버헤드가 발생한다.[35] 이러한 오버헤드 때문에 인터럽트 발생 빈도가 높은 시스템에서는 시스템 자원이 점유되어 원래 처리의 응답성이나 처리 속도에 영향을 미칠 수 있다.

상황에 따라서는 인터럽트를 사용하지 않고 폴링으로 플래그를 정기적으로 확인하는 등, 원래의 처리와 균형을 맞추는 것이 전체적인 성능을 향상시키는 경우가 있다. 일부 장치 드라이버는 일반적으로 인터럽트 동작을 하고 고부하 시에는 폴링으로 동작하는 구조를 가지기도 한다.[35]

RISC 프로세서에서는 인터럽트 발생 시 실행 중인 파이프라인이 붕괴되어 처리 성능이 저하되므로, 기존의 8비트 CISC 프로세서 등에 비해 인터럽트에 의한 상대적인 성능 저하 영향이 더 크다. 또한 투기적 실행의 페널티 등 복잡해진 프로세서 기능도 인터럽트 시 오버헤드를 증대시키는 요인이 된다.

7. 인터럽트 활용

인터럽트는 다음과 같은 다양한 용도로 활용된다.

- CPU 자원 유효 이용: 주변 장치의 처리 속도는 CPU의 처리 속도보다 훨씬 느리다. 따라서 주변 장치가 작업을 완료할 때까지 CPU가 다른 작업을 처리하도록 하여 효율성을 높인다. 주변 장치 처리 종료를 CPU가 주기적으로 확인하는 폴링 방식은 다른 처리 효율을 저하시키므로, 주변 장치에서 인터럽트를 통해 처리 종료를 알리는 방식이 사용된다.

- 응답성 향상: 키보드, 마우스와 같은 사용자 인터페이스는 입력 지연이나 누락이 발생하면 안 되므로, 인터럽트를 사용하여 사용자 입력을 확실하게 처리한다.

- 예외 처리의 효율화: 주변 장치에 장애가 발생한 경우, 인터럽트를 통해 프로그램에 빠르게 알릴 수 있다. 또한 프로그램에서 예외 처리를 분리하여 작성하는 것을 용이하게 한다.

- 정확한 타이밍 획득: 이미지 표시, 음악 연주, 시계 등 정확한 타이밍 처리가 필요한 기기를 제어할 때, 정확한 타이머를 사용하여 타이머 인터럽트를 발생시켜 CPU에 처리 타이밍을 알린다.

- 투명한 구현: 인터럽트 처리는 인터럽트되는 측의 처리에서 명시적으로 호출할 필요가 없으므로, 일반적으로 인터럽트되는 측의 처리에서 개별 인터럽트 처리를 고려할 필요 없이 투명한 구현이 가능하다.

인터럽트는 하드웨어 타이머 서비스, 스토리지(예: 디스크 I/O) 및 통신 인터페이스(예: UART, 이더넷)에서 데이터를 전송하고, 키보드 및 마우스 이벤트를 처리하며, 애플리케이션 시스템에서 필요로 하는 기타 시간 민감적인 이벤트에 응답하는 데 사용된다. 비마스크 인터럽트는 일반적으로 워치독 타이머 타임아웃, 전원 차단 신호 및 예외 처리와 같은 우선순위가 높은 요청에 응답하는 데 사용된다.

디스크 인터럽트는 디스크 주변 장치로부터 또는 디스크 주변 장치로의 데이터 전송 완료를 알린다. 전원 차단 인터럽트는 전력 손실이 임박했음을 예측하여, 컴퓨터가 순조로운 종료를 수행할 수 있도록 한다. 키보드 인터럽트는 키 입력을 버퍼링하여 미리 보기를 구현한다.

인터럽트는 제품군 내 일부 컴퓨터에서 구현되지 않은 명령을 에뮬레이션하는 데 사용되기도 한다.[29][30] 예를 들어 부동 소수점 명령은 일부 시스템에서는 하드웨어로 구현되고, 저가 시스템에서는 에뮬레이션될 수 있다. 후자의 경우, 구현되지 않은 부동 소수점 명령을 실행하면 "불법 명령" 예외 인터럽트가 발생한다. 인터럽트 핸들러는 소프트웨어로 부동 소수점 기능을 구현한 다음, 하드웨어로 구현된 명령이 실행된 것처럼 인터럽트된 프로그램으로 돌아간다.[31]

인터럽트는 신호와 유사하지만, 신호는 커널에 의해 중재되고 프로세스에 의해 처리되는 프로세스 간 통신(IPC)에 사용되는 반면, 인터럽트는 프로세서에 의해 중재되고 커널에 의해 처리된다는 차이점이 있다. 커널은 인터럽트를 이를 발생시킨 프로세스에 신호로 전달할 수 있다(일반적인 예는 SIGSEGV, SIGBUS, SIGILL 및 SIGFPE이다).

한국에서는 온라인 게임, 실시간 스트리밍, 금융 거래 시스템 등 다양한 분야에서 인터럽트 기술이 활용되고 있으며, 특히 실시간성과 안정성이 중요한 시스템에서 핵심적인 역할을 수행한다.

8. 다중 처리

멀티코어 프로세서와 멀티 큐 NIC를 함께 사용하면 수신측 확장(RSS)을 통해 인터럽트 처리를 여러 코어에 분산시켜 성능을 향상시킬 수 있다. 멀티 큐 NIC는 별도의 인터럽트와 연결된 여러 수신 큐를 제공하며, 각 인터럽트를 다른 코어로 라우팅하여 단일 NIC가 수신한 네트워크 트래픽으로 인한 인터럽트 요청 처리를 분산한다. 인터럽트 분산은 운영 체제에 의해 자동으로 수행되거나, 인터럽트 라우팅(일반적으로 ''IRQ 선호도''라고 함)을 수동으로 구성할 수 있다.[25][26]

''수신 패킷 스티어링''(RPS)은 순수 소프트웨어 기반으로 구현되어 인터럽트 핸들러 기능의 일부로 수신 트래픽을 코어 간에 분산시킨다. RPS는 특정 하드웨어가 필요 없고, 더 진보된 트래픽 분산 필터를 가지며, NIC의 인터럽트 발생률을 감소시킨다는 장점이 있지만, 프로세서 간 인터럽트(IPI) 발생률을 증가시킨다는 단점이 있다. ''수신 흐름 스티어링''(RFS)은 응용 프로그램 지역성을 고려하여 소프트웨어 기반 방식을 더욱 발전시킨 기술로, 특정 네트워크 패킷이 대상 응용 프로그램에 의해 소비될 동일한 코어에서 인터럽트 요청을 처리하여 성능을 향상시킨다.[25][27][28]

참조

[1]

웹사이트

The Jargon File, version 4.4.7

http://catb.org/esr/[...]

2003-10-27

[2]

웹사이트

"Linux Device Drivers, Third Edition, Chapter 10. Interrupt Handling"

https://lwn.net/imag[...]

O'Reilly Media

2014-12-25

[3]

웹사이트

Basics of Interrupts

http://www.sltf.com/[...]

1995-05

[4]

간행물

Multiprogramming

[5]

서적

Computer structures: readings and examples

https://books.google[...]

McGraw-Hill

2019-02-18

[6]

웹사이트

Interrupts

https://people.cs.cl[...]

2021-12-22

[7]

웹사이트

Hardware interrupts

https://access.redha[...]

2014-02-09

[8]

서적

Control Data 3600 Computer System Reference Manual

http://bitsavers.org[...]

Control Data Corporation

1964-07

[9]

서적

Microcontroller Engineering with MSP432: Fundamentals and Applications

https://books.google[...]

CRC Press

[10]

웹사이트

Interrupt Levels

https://docs.rtems.o[...]

2023-11-17

[11]

서적

Real-Time Concepts for Embedded Systems

CRC Press

2003

[12]

웹사이트

Hardware exceptions

https://docs.microso[...]

2021-08-03

[13]

서적

The Art Of Assembly Language Programming

2021-12-22

[14]

서적

Computer systems: a programmer's perspective

Pearson

2016

[15]

웹사이트

"Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture"

https://www.intel.co[...]

2021-12-22

[16]

웹사이트

"Intel® 64 and IA-32 architectures software developer's manual volume 3A: System programming guide, part 1"

https://www.intel.co[...]

2021-12-22

[17]

웹사이트

Exception Handling

https://developer.ar[...]

ARM Cortex-A Series Programmer's Guide for ARMv7-A

2022-01-21

[18]

웹사이트

Types of exception

https://developer.ar[...]

ARM Cortex-A Series Programmer's Guide for ARMv7-A

2021-12-22

[19]

서적

Control Data 6400/6500/6600 Computer Systems Reference Manual

http://bitsavers.org[...]

Control Data Corporation

2023-05-17

[20]

서적

IBM System/360 Principles of Operation

http://bitsavers.org[...]

IBM

1968-09

[21]

서적

PDP-11 Processor Handbook PDP11/04//34a/44/60/70

http://bitsavers.org[...]

Digital Equipment Corporation

1979

[22]

서적

PDP-11 Peripherals and Interfacing Handbook

http://bitsavers.org[...]

Digital Equipment Corporation

[23]

Citation

CHAPTER 2 - Overview of the Cortex-M3

https://www.scienced[...]

Newnes

2023-10-11

[24]

간행물

Eliminating receive livelock in an interrupt-driven kernel

http://portal.acm.or[...]

2010-11-11

[25]

웹사이트

Documentation/networking/scaling.txt

https://www.kernel.o[...]

kernel.org

2014-11-16

[26]

웹사이트

Intel 82574 Gigabit Ethernet Controller Family Datasheet

http://www.intel.com[...]

Intel

2014-11-16

[27]

웹사이트

Receive packet steering

https://lwn.net/Arti[...]

LWN.net

2014-11-16

[28]

웹사이트

Receive flow steering

https://lwn.net/Arti[...]

LWN.net

2014-11-16

[29]

서적

IBM System/360 Operating System - Guide to Model 91 Support

http://bitsavers.org[...]

2024-09-02

[30]

웹사이트

Patent US 5632028 A

https://patents.goog[...]

2017-08-13

[31]

서적

Nios II Processor Reference

https://www.altera.c[...]

2017-08-13

[32]

서적

bit 単語帳

共立出版

1990-08-15

[33]

웹사이트

Interrupt Levels

https://docs.rtems.o[...]

2023-11-18

[34]

문서

[35]

문서

Linux kernel 2.6 network interface driver

http://wiki.bit-hive[...]

[36]

서적

コンピューターへの道

文藝春秋

[37]

서적

電子計算機の誕生

[38]

트윗

https://x.com/eiitiw[...]

2012-09-20

[39]

웹인용

M68000PRM 사용 설명서, Interrupt

http://www.freescale[...]

2015-06-20

[40]

웹인용

ATmega Interrupt

http://www.atmel.com[...]

2015-06-26

[41]

웹인용

8051 Interrupt

http://web.mit.edu/6[...]

2015-06-26

[42]

웹인용

입출력 처리 방식 인터럽트와 폴링

http://www.electroni[...]

2015-06-20

[43]

웹인용

인터럽트와 폴링 특징

http://www.calvin.ed[...]

2015-06-20

[44]

웹인용

컴퓨터 인터럽트

http://www2.stevenso[...]

2015-06-20

[45]

웹인용

8051 타이머 0, 모드 1 예

http://www.keil.com/[...]

2015-06-19

[46]

웹인용

8051 인터럽트,6 시리얼 인터럽트

http://www.ee.iitb.a[...]

2015-06-25

[47]

웹인용

SDCC 개발환경

http://sdcc.sourcefo[...]

2015-06-25

[48]

웹인용

SDCC 사용 설명서

http://sdcc.sourcefo[...]

2015-06-25

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com