ARM 아키텍처

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

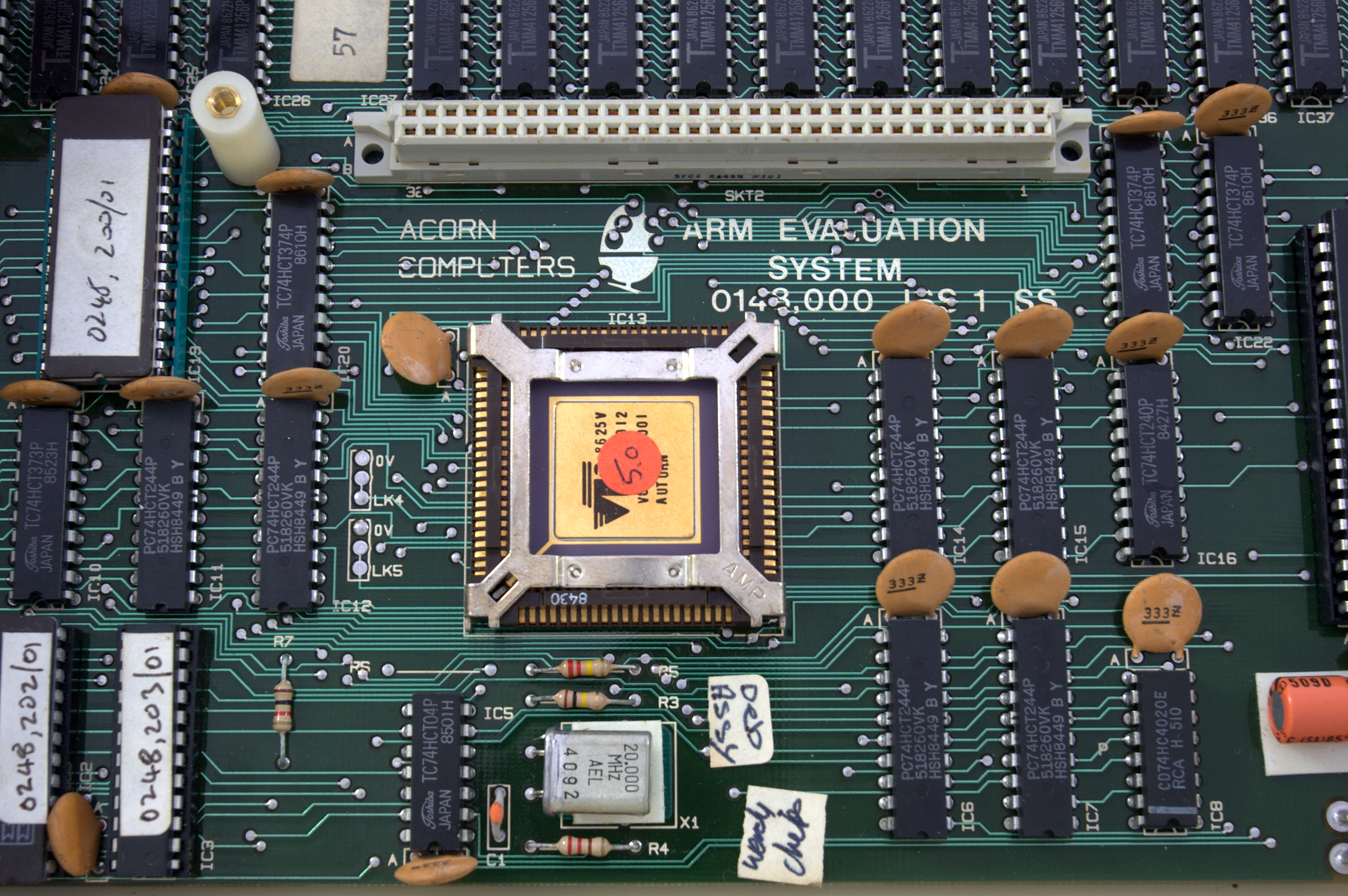

ARM 아키텍처는 영국의 Acorn Computers가 1983년에 시작한 프로젝트로, 저전력, 고성능을 목표로 하는 RISC(축소 명령어 집합 컴퓨팅) 기반의 프로세서 아키텍처이다. 1985년 최초의 ARM1 칩 출시 이후, ARM2, ARM3 등을 거쳐 ARM6, ARM7, StrongARM, ARM9, ARM10, ARM11, Cortex 시리즈, ARMv8-A, ARMv9-A 등 다양한 코어들이 개발되었다. ARM 아키텍처는 명령어 집합, Thumb 명령어 집합, Jazelle, DSP 및 SIMD 확장, VFP(Vector Floating Point), 보안 확장(TrustZone) 등 다양한 특징을 갖추고 있으며, 32비트 및 64비트 아키텍처를 모두 지원한다. ARM은 라이선싱을 통해 다양한 기업에 IP 코어를 제공하며, 삼성전자, 애플, 퀄컴 등 많은 회사에서 ARM 아키텍처 기반의 프로세서를 개발하고 있다. ARM 아키텍처는 안드로이드, iOS, 윈도우, macOS 등 다양한 운영 체제를 지원하며, 모바일 기기, 임베디드 시스템, 서버, 자동차 등 다양한 분야에서 널리 사용되고 있다.

더 읽어볼만한 페이지

- ARM 아키텍처 - XScale

XScale은 인텔이 개발한 32비트 ARM 아키텍처 기반의 프로세서 제품군으로, 스마트폰, PDA, 라우터 등 다양한 기기에 사용되었다. - ARM 아키텍처 - 스펙터 (버그)

스펙터는 2017년에 발견된 CPU 보안 취약점으로, 추측 실행의 부작용을 악용하여 다른 프로그램의 메모리 영역에 접근하게 하며, 인텔, AMD, ARM 등 다양한 제조사의 프로세서에 영향을 미친다. - 임베디드 마이크로프로세서 - 삼성 엑시노스

삼성 엑시노스는 삼성전자 시스템LSI 사업부에서 설계 및 생산하는 모바일 AP로, 갤럭시 S에 처음 탑재된 이후 다양한 기기에 사용되었으며, ARM 코어와 자체 개발 코어를 거쳐 AMD와 협력하여 RDNA 아키텍처 기반 GPU를 탑재한 제품을 출시하고 있다. - 임베디드 마이크로프로세서 - 슈퍼H

슈퍼H는 히타치에서 개발한 RISC 기반 CPU 코어 제품군으로, 상위 호환성을 갖는 명령어 집합과 높은 코드 밀도를 특징으로 하며, 다양한 모델이 개발되어 여러 기기에 탑재되었으나, ARM 아키텍처의 부상으로 개발이 중단된 후 르네사스 일렉트로닉스를 통해 라이선스가 제공되고 SH-2 특허 만료 후에는 오픈 소스 구현 프로젝트가 진행되었다. - 마이크로컨트롤러 - 마이크로프로세서

마이크로프로세서는 CPU 기능을 단일 IC에 통합한 것으로, 무어의 법칙에 따라 성능이 향상되어 왔으며 다양한 아키텍처와 기술 발전을 거쳐 현재 광범위한 분야에서 사용된다. - 마이크로컨트롤러 - 아두이노

아두이노는 Atmel AVR 마이크로컨트롤러 기반의 오픈 소스 하드웨어 플랫폼으로, C 언어와 유사한 스케치를 통해 프로그래밍이 가능하며, 다양한 플러그인 쉴드를 이용해 기능을 확장할 수 있어 교육, 시제품 제작, IoT 개발 등에 활용된다.

| ARM 아키텍처 | |

|---|---|

| 일반 정보 | |

| 이름 | ARM |

| 설계자 | 소피 윌슨 스티브 퍼버 에이콘 컴퓨터/Arm Holdings |

| 비트 | 32비트, 64비트 |

| 발표 | 1985년 |

| 설계 방식 | RISC |

| 유형 | 로드-스토어 |

| 분기 | 조건 코드, 비교 및 분기 |

| 개방 여부 | 독점 |

| ARM 64/32비트 | |

| 발표 | 2011년 |

| 버전 | ARMv8-R, ARMv8-A, ARMv8.1-A, ARMv8.2-A, ARMv8.3-A, ARMv8.4-A, ARMv8.5-A, ARMv8.6-A, ARMv8.7-A, ARMv8.8-A, ARMv8.9-A, ARMv9.0-A, ARMv9.1-A, ARMv9.2-A, ARMv9.3-A, ARMv9.4-A, ARMv9.5-A, ARMv9.6-A |

| 인코딩 | AArch64/A64 및 AArch32/A32는 32비트 명령어를 사용, AArch32/T32 (Thumb-2)는 혼합된 16비트 및 32비트 명령어를 사용함. |

| 엔디언 | 양방향성 (기본 리틀 엔디언) |

| 확장 | SVE, SVE2, SME, AES, SM3, SM4, SHA, CRC32, RNDR, TME; 모두 필수: Thumb-2, Neon, VFPv4-D16, VFPv4; 구식: Jazelle |

| GPR | 31 × 64비트 정수 레지스터 |

| FPR | 32 × 128비트 레지스터 (스칼라 32비트 및 64비트 FP 또는 SIMD FP 또는 정수용); 또는 암호화 |

| ARM 32비트 | |

| 버전 | ARMv9-R, ARMv9-M, ARMv8-R, ARMv8-M, ARMv7-A, ARMv7-R, ARMv7E-M, ARMv7-M, ARMv6-M |

| 인코딩 | 32비트, Thumb-2 확장은 혼합된 16비트 및 32비트 명령어를 사용 |

| 엔디언 | 양방향성 (기본 리틀 엔디언) |

| 확장 | Thumb-2, Neon, Jazelle, AES, SM3, SM4, SHA, CRC32, RNDR, DSP, Saturated, FPv4-SP, FPv5, Helium |

| GPR | 15 × 32비트 정수 레지스터 (R14 (링크 레지스터) 포함, R15 (PC) 제외) |

| FPR | 최대 32 × 64비트 레지스터, SIMD/부동 소수점 (선택 사항) |

| ARM 32비트 (레거시) | |

| 버전 | ARMv6, ARMv5, ARMv4T, ARMv3, ARMv2 |

| 인코딩 | 32비트, Thumb 확장은 혼합된 16비트 및 32비트 명령어를 사용 |

| 엔디언 | 양방향성 (기본 리틀 엔디언) (ARMv3 이상) |

| 확장 | Thumb, Jazelle |

| GPR | 15 × 32비트 정수 레지스터 (R14 (링크 레지스터) 포함, R15 (PC, 구형은 26비트 주소 지정) 제외) |

| FPR | 해당 없음 |

| 추가 정보 | |

| 다른 이름 | 아키텍처 |

2. 역사

애콘이 1980년대 초 BBC 마이크로의 성공을 바탕으로 차세대 머신 개발을 추진하는 과정에서 ARM 아키텍처 개발이 시작되었다. 당시 애콘은 기존 6502 프로세서의 성능 한계에 직면했고, 더욱 효율적이고 저전력의 32비트 프로세서 개발이 시급했다.[216]

소피 윌슨(Sophie Wilson)과 스티브 퍼버(Steve Furber)가 프로젝트를 이끌었다. 윌슨은 명령어 집합 아키텍처 설계를, 퍼버는 하드웨어 설계를 주도했다. 이들은 버클리 RISC와 스탠퍼드 대학교 연구의 영향을 받아 RISC(축소 명령어 집합 컴퓨팅) 아키텍처를 채택했다.[216]

개발팀은 VLSI Technology영어를 "실리콘 파트너"로 선택하여, 애콘이 설계를 제공하고 VLSI가 레이아웃과 제조를 담당했다. 1985년 4월 26일, 최초의 ARM 실리콘 칩인 '''ARM1'''이 정상 작동했다. ARM1은 6MHz로 작동했으며, BBC 마이크로용 세컨드 프로세서로 처음 실용화되었다.[217]

1986년 말 '''ARM2'''가 8MHz로 등장했고, 이듬해에는 10~12MHz로 작동하는 버전이 출시되었다. ARM2는 부스의 곱셈 알고리즘을 통해 곱셈을 하드웨어로 구현하고, "FIQ(Fast Interrupt reQuest) 모드"를 추가하여 인터럽트 처리 속도를 높였다.[216]

ARM2는 1987년 애콘 아키메데스(Acorn Archimedes) 시리즈에 처음 사용되었다. Dhrystone 벤치마크에서 ARM2는 7MHz MC68000 기반 시스템보다 약 7배, 16MHz 인텔 80386과 거의 동등한 성능을 보였다.[216]

ARM2는 32비트 데이터 버스, 26비트 주소 공간, 16개의 32비트 레지스터(프로그램 카운터 포함)를 갖추었다. 트랜지스터 수는 30,000개로, 마이크로코드와 캐시가 없어 저전력, 간편한 열처리가 가능했다. 그럼에도 인텔 80286, 인텔 386보다 뛰어난 성능을 제공했다. 후속 기종인 '''ARM3'''는 4KB 캐시를 탑재하여 성능을 더욱 향상시켰다.

1980년대 후반, 애플은 애콘과 공동으로 새로운 ARM 코어 개발에 착수했다. 1990년 애콘은 개발팀을 분사하여 Advanced RISC Machines를 설립했다. 이 때문에 ARM은 '''Advanced RISC Machine'''의 약자로 알려져 있다. Advanced RISC Machines는 1998년 런던 증권거래소와 나스닥에 상장될 때 ARM Limited가 되었다.

'''ARM6'''는 1991년에 최초 모델이 출시되었고, 애플은 ARM6 기반 ARM610을 애플 뉴턴에 채용했다. ARM2는 30,000개, ARM6는 35,000개의 트랜지스터를 사용했다.

ARM6의 개량판 '''ARM7'''은 휴대 전화에 널리 채용되며 ARM의 초석이 되었다. ARMv4 아키텍처 기반 '''ARM7TDMI'''는 Thumb 명령어(후술)를 구현하여 저전력과 높은 코드 효율을 제공, 휴대 전화나 게임보이 어드밴스 등에 채용되었다.

DEC는 ARMv4 아키텍처 라이선스를 얻어 스트롱ARM을 제조했다. 이는 인텔로 이관되었고, 인텔은 XScale을 개발했다. 이후 '''ARM9''', '''ARM10'''을 거쳐, NEC와의 제휴 등으로 휴대 전화용 프로세서 지위를 확고히 한 '''ARM11'''이 출시된다.

2005년 제품 라인업을 개편, 애플리케이션 프로세서용 '''Cortex-A''', 실시간 제어용 '''Cortex-R''', 임베디드 시스템용 '''Cortex-M'''으로 시리즈를 분류했다.[218] 2012년 11월, ARM 최초 64비트 아키텍처 프로세서 코어 '''Cortex-A50''' 시리즈를 발표했다.[219]

ARM 칩은 세계에서 가장 많이 사용되는 CPU 설계 중 하나이며, 2004년 세계 시장 점유율은 61%였다.[220]

'''ARM 아키텍처 버전 역사'''

| 버전 | 연도 | 설명 |

|---|---|---|

| ARMv4 | 32비트 주소 영역, 32비트 ISA(Instruction Set Architecture) 동작 | |

| ARMv4T | 16비트 Thumb 명령어 셋 탑재. 메모리 공간 35% 이상 절약 | |

| ARMv5TE | 1999 | 개선된 thumb 아키텍처와 ‘Enhanced’ DSP 명령어 셋을 ARM ISA에 추가 |

| ARMv5TEJ | 2000 | Jazelle(자바 하드웨어 가속기) 확장 명령어 추가 |

| ARMv6 | 2001 | 메모리 시스템, 예외 처리 개선, 멀티프로세싱 지원, SIMD(Single Instruction Multiple Data) 미디어 명령어 포함 |

2. 1. 초기 개발

애크론 컴퓨터(Acorn Computers)는 1981년 12월 BBC 마이크로(BBC Micro)를 출시하여 첫 성공을 거두었다. MOS 테크놀로지 6502(MOS Technology 6502) CPU를 기반으로 했지만, 더 빠른 동적 램(DRAM)을 사용하여 애플 II(Apple II) 등 경쟁 기종보다 약 두 배의 성능을 보였다.[14]1981년 IBM PC 출시로 데스크톱 컴퓨터 시장은 큰 변화를 겪었다. 인텔 8088 CPU를 사용한 PC는 이전 8비트 기종보다 향상된 성능을 제공했고, 취미와 게임 시장은 필수적인 비즈니스 도구 시장으로 변하기 시작했다. 모토로라 68000[16], 내셔널 세미컨덕터 NS32016[17]과 같은 새로운 32비트 설계도 시장에 진출했다.

에이콘은 이 시장에서 경쟁하기 위해 에이콘 비즈니스 컴퓨터(Acorn Business Computer)라는 새로운 설계를 제시했다. BBC 마이크로의 10배 성능을 동일한 가격에 구현하는 것을 목표로 했다. 그러나 기존 16비트 설계는 비싸면서도 성능이 충분하지 않았고, 새로운 32비트 설계도 지원 칩 문제로 비용이 많이 들었다.[18] 소피 윌슨(Sophie Wilson)에 따르면, 당시 테스트된 모든 프로세서는 약 4 Mbit/s 대역폭으로 거의 동일한 성능을 보였다.[19]

캘리포니아 대학교 버클리의 RISC 보고서[20]와 웨스턴 디자인 센터(Western Design Center) 방문[21]은 에이콘이 자체 CPU 설계를 시작하는 계기가 되었다. 1983년 말, 에이콘은 Acorn RISC Machine (ARM) 프로젝트를 시작했다.[21]

초기 버클리 RISC 설계는 교육용 시스템에 가까웠지만, ARM은 6502의 장점인 빠른 인터럽트 처리 기능을 추가했다. 이를 위해 ARM 설계는 물리적인 주소 공간을 64MB로 제한하고 26비트 주소를 사용했다. 명령어는 4바이트(32비트) 길이로 4바이트 경계에 맞춰야 했으므로, 명령어 주소의 하위 2비트는 항상 0이었다. 이는 프로그램 카운터(PC)가 24비트만 필요하고, 8비트 프로세서 플래그와 함께 단일 32비트 레지스터에 저장할 수 있음을 의미했다. 이 결정으로 인터럽트 오버헤드가 절반으로 줄었다.[21]

또한 ARM은 페이지 모드 DRAM을 활용하여 메모리 성능을 향상시키는 "S-사이클" 명령어를 추가했다. 이를 통해 사용 가능할 경우 메모리 성능이 두 배로 향상되었으며, 특히 그래픽 성능에 중요했다.[21]

윌슨은 BBC BASIC으로 프로세서 시뮬레이션을 작성했고, 이는 두 번째 6502 프로세서를 갖춘 BBC 마이크로에서 실행되었다.[22][23] 윌슨은 Acorn의 CEO인 허먼 하우저에게 더 많은 자원을 요청했고, 하우저는 승인하여 윌슨의 ISA를 기반으로 실제 프로세서를 설계할 소규모 팀을 구성했다.[24]

Acorn은 VLSI 테크놀로지를 실리콘 파트너로 선택했다. 1985년 4월 26일, ARM 실리콘의 첫 번째 샘플인 ARM1이 개발되었다.[2] 이 버전은 6MHz로 작동했다.[2]

첫 번째 ARM 애플리케이션은 BBC 마이크로의 두 번째 프로세서로, 지원 칩 개발 및 CAD 소프트웨어 속도 향상에 사용되었다. 윌슨은 ARM 어셈블리어로 BBC 베이직을 다시 작성하여 코드를 매우 압축적으로 만들었고, 이는 ARM 에뮬레이터 테스트에 유용하게 사용되었다.

1980년대 초, 영국의 애콘은 Acorn RISC Machine (ARM) 프로젝트를 시작했다. 이는 BBC 마이크로의 성공을 바탕으로 차세대 머신 개발을 추진하는 과정에서 6502 프로세서의 성능 한계를 극복하고, 효율적이고 저전력의 32비트 프로세서 개발을 목표로 했다.[216]

소피 윌슨(Sophie Wilson)과 스티브 퍼버(Steve Furber)를 중심으로 한 소규모 팀은 버클리 RISC와 스탠퍼드 대학교 연구의 영향을 받아 RISC(축소 명령어 집합 컴퓨팅) 아키텍처를 채택했다.[216]

개발팀은 VLSI 테크놀로지를 실리콘 파트너로 선택하여 1985년 4월 26일에 최초의 ARM 실리콘 칩인 '''ARM1'''을 개발했다. ARM1은 6MHz로 작동했으며, BBC 마이크로용 세컨드 프로세서로 활용되었다.[217] BBC 베이직은 어셈블리어로 다시 작성되어 ARM 에뮬레이터 테스트에 사용되었다.[216]

1986년 말, 곱셈 연산 하드웨어 구현과 인터럽트 처리 속도 향상 등 개선을 거친 '''ARM2'''가 8MHz로 출시되었고, 이듬해에는 10~12MHz 버전이 출시되었다. ARM2는 1987년에 출시된 애콘 아키메데스(Acorn Archimedes) 시리즈에 탑재되어 상업적인 성공을 거두었다.[216] Dhrystone 벤치마크에 따르면, ARM2는 7MHz로 작동하는 MC68000 기반 시스템보다 약 7배의 성능을 보였고, 16MHz의 인텔 80386과 거의 동등한 속도를 가졌다. ARM2는 고속 I/O에 대응하도록 설계되었고, DMA 컨트롤러와 같은 지원 칩을 생략하여 설계를 간소화했다.[216]

ARM2는 32비트 데이터 버스, 26비트 주소 공간, 16개의 32비트 레지스터(프로그램 카운터 포함)를 갖추고 있었다. 트랜지스터 수는 30,000개로, 모토로라 68000의 68,000개보다 적었다. 이는 ARM2가 마이크로코드와 캐시를 탑재하지 않아 저전력과 간편한 열처리가 가능했기 때문이다. ARM2는 인텔 80286이나 인텔 386에 비해 뛰어난 성능을 제공했다.

후속 기종인 '''ARM3'''는 4KB의 캐시를 탑재하여 성능을 더욱 향상시켰다.

2. 2. Advanced RISC Machines Ltd. 설립 및 발전

1980년대 후반, 애플은 에이콘과 협력하여 새로운 ARM 코어 개발을 시작했다. 이 협력은 매우 중요하게 여겨져, 에이콘은 1990년에 개발팀을 분사하여 Advanced RISC Machines Ltd. (ARM Ltd.)를 설립했다.[216] 이로 인해 ARM은 Acorn RISC Machine이 아닌 Advanced RISC Machine의 약자로 알려지게 되었다. Advanced RISC Machines는 1998년 런던 증권거래소와 나스닥에 상장되면서 ARM Limited가 되었다.이러한 과정을 거쳐 개발된 '''ARM6'''는 1991년에 최초 모델이 출시되었고, 애플은 ARM6 기반의 ARM610을 애플 뉴턴에 채택했다.[216] ARM6는 이전 모델인 ARM2에 비해 트랜지스터 수가 30,000개에서 35,000개로 약간 증가했지만, 코어 크기는 대체로 동일하게 유지되었다. 이는 최종 사용자가 ARM 코어와 다양한 옵션 부품을 조합하여 완전한 CPU를 만들 수 있도록 하여, 저렴한 비용으로 고성능을 얻을 수 있게 하는 설계 철학을 반영한 것이다.

ARM6의 개량판인 '''ARM7'''은 휴대 전화 시장에서 큰 성공을 거두었다. 특히, ARM7을 재설계한 '''ARM7TDMI'''는 Thumb 명령어(후술)를 도입하여 코드 밀도를 높이고 저전력 소비를 실현했다. 이 덕분에 ARM7TDMI는 게임보이 어드밴스와 같은 휴대용 게임기를 비롯한 다양한 민생 기기에 널리 채택되었다. TDMI는 Thumb 명령어, 디버깅(Debug) 회로, 곱셈기(Multiplier), ICE 기능을 탑재하고 있음을 의미하지만, 이후 코어에는 이러한 기능이 표준으로 탑재되면서 이 명칭은 생략되었다.[216]

DEC는 ARMv4 아키텍처 설계 라이선스를 획득하여 스트롱ARM을 제조했다. 233MHz에서 StrongARM은 단 1W의 전력만 소비했으며, 이는 나중에 소송 해결의 일환으로 인텔에 이관되었다. 인텔은 이를 기반으로 XScale을 개발했다.[216]

이후에도 StrongARM 기술의 피드백을 받은 '''ARM9'''와 '''ARM10'''을 거쳐, NEC와의 제휴 등을 통해 휴대 전화용 프로세서로서의 지위를 확고히 한 '''ARM11'''이 출시되었다.[216]

2. 3. 지속적인 발전과 64비트 아키텍처 도입

ARM은 StrongARM, ARM9, ARM10, ARM11 등 지속적인 기술 개발을 통해 성능을 향상시키고, 다양한 분야로 적용 범위를 확대했다. 2005년, Cortex 시리즈를 발표하며, 고성능 애플리케이션 프로세서 (Cortex-A), 실시간 제어 (Cortex-R), 임베디드 시스템 (Cortex-M) 등 목적에 따라 특화된 프로세서를 제공하기 시작했다.2001년에 발표된 ARMv6 아키텍처는 메모리 시스템, 예외 처리, 멀티프로세싱 환경 지원 등이 개선되었다. SIMD (Single Instruction Multiple Data) 소프트웨어 실행을 지원하는 미디어 명령어가 포함되어 오디오 및 비디오 코덱을 포함하는 응용 프로그램들의 사용 확대를 위해 최적화되었다.

2011년, 64비트 아키텍처인 ARMv8-A를 발표하며, AArch64 (ARM64)를 도입하여 서버 시장 등 고성능 컴퓨팅 분야로 진출했다. 2021년에는 Armv9-A 아키텍처를 발표하여 보안 및 인공지능 기능을 강화하였다.

3. 주요 특징

ARM 아키텍처는 RISC 기반으로 설계되어 명령어 집합이 간결하고 효율적이며, 대부분의 명령어는 1사이클로 실행된다.[215]

다른 RISC 아키텍처와 달리 ARM 아키텍처는 PC 상대 주소 지정, 프리/포스트-인크리먼트 주소 지정 모드 등 다양한 주소 지정 모드를 지원한다.[215]

ARM 명령어의 특징은 명령어 최상위 4비트를 조건 코드로 사용하여 조건부 실행이 가능하다는 것이다. 이를 통해 분기 명령어 없이 조건에 따라 실행 여부를 결정할 수 있다.[215]

또한, 쉬프트 연산을 "데이터 처리" 명령어(산술, 논리, 레지스터 간 대입)와 통합할 수 있다. 이러한 특징으로 ARM 프로그램은 일반적인 RISC 프로세서보다 높은 코드 밀도를 가진다.[215]

코드 효율을 높이기 위해 ARM 프로세서는 Thumb이라는 16비트 명령어 모드를 제공한다. Thumb 명령어는 메모리 포트나 버스가 32비트보다 좁은 환경에서 더 나은 성능을 낼 수 있다.

ARM은 자바 바이트코드를 하드웨어에서 직접 실행하는 '''Jazelle DBX'''(Direct Bytecode eXecution) 기술을 구현했다.

'''ARMv5TE''' 및 '''ARMv5TEJ''' 아키텍처는 디지털 신호 처리(DSP) 및 멀티미디어 애플리케이션을 위해 부호 있는 곱셈-누산 연산, 포화 가산 및 감산, 선행 0 개수(leading zero count) 등의 명령어를 추가했다.

'''고급 SIMD''' 확장은 '''NEON'''이라고도 불리며, 미디어 및 디지털 신호 처리에 적합한 64비트 및 128비트 SIMD 명령어 집합이다.

'''VFP''' (Vector Floating Point)는 ARM 아키텍처의 부동 소수점 연산 코프로세서 확장 기능으로, 반정밀도(v3 이상), 단정밀도, 배정밀도 부동소수점 연산을 지원한다.[221]

'''트러스트존(TrustZone)''' 기술은 ARMv6KZ 이상 아키텍처에 포함된 보안 확장 기능이다.

3. 1. 명령어 집합 아키텍처 (ISA)

ARM 아키텍처는 RISC 기반으로 설계되어, 명령어 집합이 간결하고 효율적이다. 기본적으로 32비트 고정 길이 명령어를 사용하며, 로드/스토어 아키텍처, 3 오퍼랜드 레지스터 간 연산 방식을 채택하고 있다. 대부분의 명령어는 1사이클로 실행 가능하다.[215]다른 RISC 아키텍처에 비해 ARM 아키텍처는 PC 상대 주소 지정, 프리/포스트-인크리먼트 주소 지정 모드 등 다양한 주소 지정 모드를 지원한다.[215]

시간이 지나면서 ARM 명령어 집합은 점차 확장되었다. 예를 들어, 초기 ARM 프로세서(ARM7TDMI 이전)에는 2바이트 값을 로드하는 명령어가 없었다.[215]

ARM 명령어 집합의 독특한 점 중 하나는 명령어의 최상위 4비트를 조건 코드로 사용하여 조건부 실행이 가능하다는 것이다. 이를 통해 대부분의 명령어는 분기 명령어 없이 조건에 따라 실행 여부를 결정할 수 있다.[215]

조건부 실행은 코드 내에서 작은 if문에 해당하는 부분을 분기 명령어 없이 처리할 수 있게 해준다. 예를 들어, 유클리드 호제법을 C언어로 작성하면 다음과 같다.

```c

int gcd(int i, int j)

{

while (i != j) {

if (i > j)

i -= j;

else

j -= i;

}

return i;

}

```

이 코드를 ARM 어셈블리어로 작성하면 다음과 같이 while 루프 부분을 구현할 수 있다.

```assembly

loop

CMP Ri, Rj ; i와 j를 비교

SUBGT Ri, Ri, Rj ; "GT" (i > j)이면 i = i - j;

SUBLT Rj, Rj, Ri ; "LT" (i < j)이면 j = j - i;

BNE loop ; "NE" (i != j)이면 loop로 돌아감

```

위 코드에서는 조건 코드(GT, LT, NE)를 사용하여 분기 명령어 없이 조건부 실행을 구현함으로써 코드 밀도를 높였다.[215]

또 다른 특징은 쉬프트 연산을 "데이터 처리" 명령어(산술, 논리, 레지스터 간 대입)와 통합할 수 있다는 점이다. 예를 들어, C언어의 `a += (j << 2);` 문장은 ARM 명령어 하나로 표현 가능하다.

```assembly

ADD Ra, Ra, Rj, LSL #2

```

이러한 특징들 덕분에 ARM 프로그램은 일반적인 RISC 프로세서보다 높은 코드 밀도를 가진다. 명령어 페치 횟수가 줄어들고, 분기로 인한 지연을 피하기 쉬워 파이프라인 처리를 효율적으로 사용할 수 있다. 이는 ARM이 복잡한 CPU 설계와 경쟁할 수 있게 해준 중요한 요인 중 하나이다.[215]

3. 2. Thumb 명령어 집합

ARM 프로세서는 코드 효율을 높이기 위해 Thumb이라는 16비트 명령어 모드를 가지고 있다. 이는 SuperH의 16비트 명령어/32비트 데이터 구조를 본떠 추가되었다. Thumb 명령어는 조건 실행을 위한 4비트 프리디케이트(predicate)가 제거되어, 메모리 포트나 버스가 32비트보다 좁은 환경에서 32비트 코드보다 더 나은 성능을 제공한다.임베디드 애플리케이션에서는 32비트 데이터 경로가 일부 주소 범위에만 해당하고(예: 게임보이 어드밴스), 나머지는 16비트 또는 그보다 좁은 경우가 많다. 이러한 상황에서는 Thumb 코드로 컴파일하고, CPU 부하가 큰 부분만 32비트 명령어 집합을 사용하여 수작업으로 최적화하는 것이 일반적이다.

Thumb 명령어와 ARM 명령어는 단일 실행 파일 내에서 함께 사용할 수 있지만, Thumb 명령어 실행 모드와 ARM 명령어 실행 모드는 독립적이다. 따라서 둘을 모두 사용하려면 프로세서 상태를 전환해야 한다. 상태 전환은 분기 명령어(BX, BLX)를 통해 수행되며, 일반적으로 함수 단위로 Thumb 명령어와 ARM 명령어를 구분하여 함수 호출 시 전환한다.

Thumb 기술이 처음 탑재된 프로세서는 ARM7TDMI이다. ARM9 및 이후 제품군(XScale 포함)은 모두 Thumb 기술을 탑재하고 있다.

ThumbEE(Thumb 실행 환경)는 Jazelle RCT(런타임 컴파일 대상)라고도 불리는 네 번째 명령어 모드이다. 2005년에 발표되었으며, Cortex-A8 프로세서에 처음 구현되었다. ThumbEE는 Thumb-2 명령어 집합을 약간 변경하여 JIT 컴파일러처럼 실행 시 코드를 생성하는 환경에 적합하다. 주요 대상은 자바, .NET MSIL(C# 등), 파이썬, 펄 등의 언어이다.

3. 3. Jazelle

ARM은 자바 바이트코드를 하드웨어에서 직접 실행할 수 있게 해주는 기술을 구현했다. 이 기술은 ARM 및 Thumb 모드와 함께 또 다른 실행 모드로, ARM/Thumb 모드 전환과 마찬가지로 접근할 수 있다. 이 기술은 '''Jazelle DBX'''(Direct Bytecode eXecution)라고도 불리며, 나중에 나올 Jazelle RCT와는 구별된다.Jazelle 기술이 탑재된 최초의 프로세서는 '''ARM926EJ-S'''이다. CPU 명칭에서 'J'는 Jazelle을 의미한다.

3. 4. DSP 및 SIMD 확장

ARM 아키텍처는 디지털 신호 처리(DSP) 및 멀티미디어 애플리케이션을 위해 확장되면서 여러 명령어들이 추가되었다. '''ARMv5TE''' 및 '''ARMv5TEJ''' 아키텍처의 "E"는 이러한 확장을 나타낸다.추가된 명령어는 디지털 신호 프로세서 아키텍처에서 일반적인 것으로, 부호 있는 곱셈-누산 연산, 포화 가산 및 감산, 선행 0 개수(leading zero count)의 변형 등이 있다.

'''고급 SIMD''' 확장은 '''NEON'''이라고도 불리며, 미디어 및 디지털 신호 처리에 적합한 64비트 및 128비트 SIMD 명령어 집합이다. 8/16/32/64비트 정수 연산과 32비트(단정밀도) 부동 소수점 연산을 위한 SIMD 명령어가 정의되어 있으며, ARMv7부터 사용 가능하다. 32비트 CPU에서는 배정밀도 부동 소수점수는 사용 불가능하며, 배정밀도에는 VFP를 사용한다.

대부분의 ARMv7 SoC는 NEON을 지원하지만, 엔비디아 테그라(NVIDIA Tegra) 2 시리즈 등은 지원하지 않는다.

레지스터는 VFP 레지스터로 준비된 32개의 64비트 레지스터를 사용하여 32개의 64비트 SIMD 레지스터(D0-D31) 또는 16개의 128비트 SIMD 레지스터(Q0-Q15)로 접근할 수 있다. 예를 들어 128비트 레지스터 Q0은 D0과 D1의 두 개의 64비트 레지스터 영역에 매핑되어 있다.

Cortex-A15 등에서는 NEONv2(version 2)가 탑재되어 Fused Multiply-Add가 가능하다. 이를 통해 단정밀도 부동 소수점수에서 8 FLOPS/cycle이 되었다.

'''무선 MMX'''(WMMX)는 인텔이 XScale 프로세서를 위해 개발한 SIMD 명령어 집합이다. 64비트 너비의 레지스터가 16개 제공되며, 8/16/32/64비트 SIMD 정수 연산이 가능하다. XScale 및 그 매각처인 마벨 테크놀로지 그룹(Marvell Technology Group) 제 ARM SoC에 채택되었다. 명령어 집합 자체는 x86 프로세서의 MMX와는 완전히 다르지만, GCC나 Visual C++ 등의 컴파일러에서 사용할 수 있는 내장 함수는 MMX와의 호환성이 어느 정도 확보되어 있으며, 이를 이용하면 MMX용으로 작성된 코드를 비교적 쉽게 이식할 수 있다.

3. 5. 부동 소수점 연산 (VFP)

VFP (Vector Floating Point)는 ARM 아키텍처의 부동 소수점 연산 코프로세서 확장 기능이다. 반정밀도(v3 이상), 단정밀도, 배정밀도 부동소수점 연산 기능을 제공한다.[221]- VFPv1: 폐기됨

- VFPv2: ARMv5TE, ARMv5TEJ, ARMv6에서 사용 가능

- VFPv3: ARMv7에서 사용 가능. 일반적으로 레지스터 수는 32개이지만, 엔비디아 테그라(NVIDIA Tegra) 2 시리즈 등은 레지스터 수가 절반인 VFPv3-D16을 채용. Cortex-A8의 구현은 파이프라이닝되지 않아 매우 느림 (VFP Lite).

- VFPv4: Cortex-A5, A7, A15, 애플 A6(Apple A6), 퀄컴 스냅드래곤(Snapdragon) Krait 등에서 사용 가능. IEEE754 준수의 (곱셈 결과의 반올림을 수행하지 않는) Fused multiply add 지원. VFPv4-D16도 있음.

"Vector"라는 이름에서 알 수 있듯이, 일부 명령어에서는 벡터 모드라고 불리는 한 명령어로 여러 레지스터에 대해 연산을 수행하는 모드가 제공된다. 이 모드를 사용하면 SIMD 연산이 가능하지만, 프로그래밍 모델이 다소 복잡했다. 당시 ARM11 프로세서의 구현은 스칼라 명령어를 요소 수만큼 순차적으로 실행하는 SIMD 연산의 장점을 누릴 수 없었기 때문에, 적극적으로 사용되지 않았다. VFPv3을 구현하는 ARMv7 세대 이후에는 Advanced SIMD 확장 명령어 (NEON)가 도입되었기 때문에, 현재는 벡터 모드의 사용이 권장되지 않는다. Cortex-A9 및 A15는 벡터 모드를 지원하지 않으므로, 현재 ARM 아키텍처에서 VFP의 위치는 스칼라 전용 부동소수점 연산 코프로세서이며, SIMD 연산 용도는 NEON에 자리를 내주었다.

단정밀도 부동소수점 연산은 NEON에서도 실행 가능하지만, 배정밀도 부동소수점 연산이나 IEEE754 준수의 4가지 반올림 모드, 비정규화 수 지원 등은 NEON에는 없으므로, 이들을 사용하려면 VFP 명령어를 사용해야 한다.

3. 6. 보안 확장 (TrustZone)

트러스트존(TrustZone) 기술은 ARMv6KZ 이상의 애플리케이션 프로파일 아키텍처에 포함된 보안 확장 기능으로, "TrustZone Technology"라는 이름으로 마케팅되었다. 이는 하드웨어 기반 접근 제어를 통해 두 개의 가상 프로세서를 제공함으로써, 별도의 보안 코어를 추가하지 않고도 비용을 절감할 수 있게 해준다.[25]ARMv8-M 아키텍처에는 "TrustZone for ARMv8-M Technology"로 마케팅되는 보안 확장 기능이 도입되었다. 이처럼 TrustZone은 Cortex-A 시리즈와 Cortex-M 시리즈에 각각 적용되어, 다양한 환경에서 보안 기능을 제공한다.

4. ARM 코어 종류

0.33 DMIPS/MHz

0.50 DMIPS/MHz

0.65 DMIPS/MHz

0.68 DMIPS/MHz

0.73 DMIPS/MHz

63DMIPS @ 70 MHz

1.0 DMIPS/MHz

1.16 DMIPS/MHz