I²C

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

I²C(Inter-Integrated Circuit)는 1980년대 초 필립스(현 NXP 반도체)에서 개발된 전자 제품 내부 버스 시스템으로, 직렬 데이터(SDA)와 직렬 클럭(SCL) 두 개의 양방향 라인을 사용하여 여러 장치 간의 통신을 가능하게 한다. 1992년 최초 표준 버전이 발표된 이후 여러 차례 업데이트를 거쳐왔으며, 2004년 특허 소멸 후 로열티 없이 사용 가능하다. I²C는 다양한 모드를 지원하며, 7비트 또는 10비트 주소 지정을 사용한다. 이 기술은 마이크로컨트롤러에서 주변 장치 제어, 프로토타입 시스템, 다양한 커넥터를 통한 연결 등 광범위하게 활용되며, 윈도우, 리눅스, macOS 등 다양한 운영 체제에서 지원된다. I²C는 핫 스왑 기능, 소형화, 저전력 소비 등의 장점이 있지만, 주소 충돌, 자동 버스 구성의 어려움, 속도 제한, 오류 발생 가능성 등의 한계를 지닌다.

1980년대 초, 필립스(현 NXP 반도체)에서 다양한 칩들을 이용한 전자 제품 구성을 위한 간단한 내부 버스 시스템으로 개발되었다. 1992년에 최초 표준 버전(버전 1.0)이 발표되었는데, '패스트 모드'(400 kbit/s) 및 10비트 주소 지정 기능이 추가되었다. 1998년에는 버전 2.0이 발표되어 '고속 모드'(3.4 Mbit/s), 저전압 동작, 전원 관리 요구 사항이 추가되었다. 2001년에 발표된 버전 2.1은 버전 2.0에서 약간 수정된 것이다.

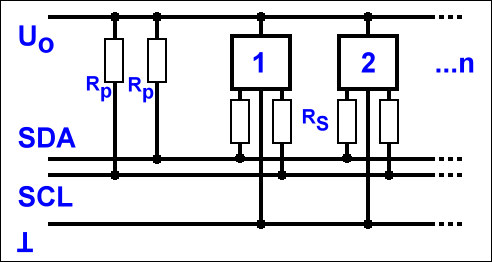

I²C는 풀업 저항이 연결된 직렬 데이터(SDA)와 직렬 클럭(SCL)이라는 두 개의 양방향 오픈 컬렉터 라인을 사용한다. 일반적으로 +3.3V 또는 +5V 전압이 사용된다.

2. 역사

2007년에는 버전 3이 발표되어 1 Mbit/s '고속 모드 플러스(Fm+)' 및 장치 ID 메커니즘이 추가되었다. 2012년에는 버전 4와 5가 발표되었는데, 5 Mbit/s '초고속 모드(UFm)'가 추가되고 제조업체 ID 테이블이 할당되었으며, 오류가 수정되었다. 2014년에 발표된 버전 6에서는 오류가 수정되었다. 2021년에는 버전 7이 발표되어 용어가 변경되었고(마스터/슬레이브를 컨트롤러/타겟으로 변경), MIPI I3C 개요 절이 추가되었다.

2004년에 특허가 소멸되어 현재는 로열티 프리이다.연도 버전 비고 1981 특허 필립스에 의해 1981년 11월 2일에 출원된 미국 특허 4,689,740.[43][44] 1982 오리지널 100 kbit/s I²C 시스템은 다양한 필립스 칩으로 제어 전자 장치를 구축하기 위한 간단한 내부 버스 시스템으로 만들어졌다. 1992 1 400 kbit/s 고속 모드(Fm)와 10비트 어드레싱 모드를 추가하여 용량을 1008 노드로 증가시켰다. 이는 최초의 표준화된 버전이었다. 1998 2 전기 전압 및 전류에 대한 전력 절감 요구 사항과 함께 3.4 Mbit/s 고속 모드(Hs)를 추가했다.[45] 2000 2.1 중요한 기능 변경 없이 버전 2를 명확히 했다.[46] 2007 3 1 Mbit/s 고속 모드 플러스(Fm+) (20 mA 드라이버 사용) 및 장치 ID 메커니즘을 추가했다.[47] 2012 4 풀업 저항 없이 푸시-풀 출력 로직을 사용하는 새로운 USDA(데이터) 및 USCL(클럭) 라인에 대한 5 Mbit/s 초고속 모드(UFm)를 추가하고 할당된 제조업체 ID 테이블을 추가했다.

이는 단방향 통신 버스이다.[48]2012 5 오류를 수정했다.[49] 2014 6 두 개의 그래프를 수정했다.[50] 2021 7 마스터/슬레이브라는 용어를 I3C 버스 규격에 맞춰 "컨트롤러/타겟"으로 변경했다.

할당된 제조업체 ID 테이블 5를 업데이트했다. I3C 버스 개요 섹션 9를 추가했다. 현재 표준이다(로그인 필요).[51]

3. 설계

I²C 레퍼런스 디자인은 7비트 주소 공간을 가지며, 이 중 16개는 예약되어 있어 동일한 버스에 최대 112개의 노드를 연결할 수 있다. 10비트 주소 지정을 통해 최대 1008개의 노드를 연결할 수 있다.[4]

I²C는 다음과 같은 다양한 통신 속도를 지원한다.모드[51] 최대

속도최대

정전 용량드라이브 방향 표준 모드(Sm) 100 kbit/s 400 pF 오픈 드레인 양방향 고속 모드(Fm) 400 kbit/s 400 pF 오픈 드레인 양방향 고속 모드 플러스(Fm+) 1 Mbit/s 550 pF 오픈 드레인 양방향 고속 모드(Hs) 1.7 Mbit/s 400 pF 오픈 드레인 양방향 고속 모드(Hs) 3.4 Mbit/s 100 pF 오픈 드레인 양방향 초고속 모드(UFm) 5 Mbit/s ? 푸시-풀 단방향

I²C 버스는 컨트롤러(마스터)와 타겟(슬레이브) 역할을 하는 노드로 구성된다. 컨트롤러 노드는 클럭을 생성하고 타겟과의 통신을 시작하며, 타겟 노드는 클럭을 수신하고 컨트롤러의 주소 지정에 응답한다. 이 버스는 다중 컨트롤러를 지원하며, 컨트롤러와 타겟 역할은 메시지 간에 변경될 수 있다.

I²C 통신에는 여러 가지 작동 모드가 있다. 모든 모드는 100 kbit/s의 "표준 모드"를 항상 사용할 수 있다는 점에서 호환되지만, 동일한 버스에서 서로 다른 기능을 가진 장치를 결합하면 문제가 발생할 수 있다.

3. 1. 물리 계층

물리 계층에서 SCL과 SDA 라인은 모두 오픈 드레인(MOSFET) 또는 오픈 컬렉터(BJT) 버스 설계를 사용하므로 각 라인에 풀업 저항이 필요하다. 로직 "0"은 라인을 접지로 당겨 출력하며, 로직 "1"은 라인이 떠 있게(출력 하이 임피던스) 하여 풀업 저항이 높게 당겨 출력한다. 라인은 절대 능동적으로 높게 구동되지 않는다. 이 배선 방식은 여러 노드가 신호 경합으로 인한 단락 없이 버스에 연결될 수 있도록 한다. 고속 시스템(및 일부 다른 시스템)은 더 높은 버스 커패시턴스를 수용하고 더 빠른 상승 시간을 가능하게 하기 위해 저항 대신 전류원을 사용하여 SCL 또는 SCL과 SDA 모두를 풀업할 수 있다.

이러한 설계의 중요한 결과는 여러 노드가 동시에 라인을 구동할 수 있다는 것이다. 만약 ''어떤'' 노드라도 라인을 낮게 구동하면, 라인은 낮아진다. 논리 1을 전송하려는 노드(예: 라인이 높게 떠 있게 함)는 이를 감지하고 다른 노드가 동시에 활성화되어 있음을 결론지을 수 있다.

SCL에서 사용될 때, 이것은 ''클럭 스트레칭''이라고 불리며, 대상에 대한 흐름 제어 메커니즘이다. SDA에서 사용될 때, 이것은 중재라고 불리며 한 번에 하나의 송신자만 존재하도록 보장한다.

유휴 상태일 때, 두 라인은 모두 높다. 트랜잭션을 시작하기 위해, SCL이 높은 상태를 유지하는 동안 SDA가 낮게 당겨진다. SDA를 다시 높게 뜨도록 하여 정지 신호를 전송하는 것은 불법이지만, 일반적으로 무해하다. 다음 단계는 SCL을 낮게 당기는 것이다.

시작 및 정지 신호를 제외하고, SDA 라인은 클럭이 낮은 동안에만 변경된다. 데이터 비트를 전송하는 것은 원하는 레벨에서 데이터 라인을 안정적으로 유지하면서 클럭 라인을 높게 펄싱하는 것으로 구성된다.

SCL이 낮은 동안, 송신기(초기에는 컨트롤러)는 원하는 값으로 SDA를 설정하고(값을 전파할 작은 지연 후) SCL을 높게 뜨게 한다. 그런 다음 컨트롤러는 SCL이 실제로 높아질 때까지 기다린다. 이것은 SCL 신호의 유한한 상승 시간(RC 시정수)과 버스의 기생 커패시턴스에 의해 지연되며 대상의 클럭 스트레칭에 의해 추가로 지연될 수 있다.

SCL이 높아지면, 컨트롤러는 수신기가 비트를 확인했는지 확인하기 위해 최소 시간(표준 속도 I2C의 경우 4 μs)을 기다린 다음 다시 낮게 당긴다. 이것으로 한 비트의 전송이 완료된다.

한 방향으로 8개의 데이터 비트마다, "응답" 비트가 다른 방향으로 전송된다. 송신자와 수신자는 한 비트 동안 역할을 바꾸고, 원래의 수신기는 단일 "0" 비트(ACK)를 다시 전송한다. 송신기가 "1" 비트(NACK)를 대신 감지하면 다음을 알게 된다.

응답 비트 동안 SDA 라인만 방향이 변경된다. SCL은 항상 컨트롤러에 의해 제어된다.

응답 비트 후에, 클럭 라인은 낮고 컨트롤러는 세 가지 중 하나를 수행할 수 있다.

I²C 프로토콜의 중요한 기능 중 하나는 클럭 스트레칭이다. 주소가 지정된 대상 장치는 바이트를 수신(또는 전송)한 후 클럭 라인(SCL)을 로우 상태로 유지하여 더 많은 데이터를 처리할 준비가 아직 되지 않았음을 나타낼 수 있다. 대상과 통신하는 컨트롤러는 현재 비트의 전송을 완료하지 못할 수 있지만, 클럭 라인이 실제로 하이 상태가 될 때까지 기다려야 한다. 대상이 클럭 스트레칭을 하는 경우, 클럭 라인은 여전히 로우 상태로 유지된다(연결이 오픈 드레인이기 때문). 두 번째로 느린 컨트롤러가 동시에 클럭을 구동하려는 경우에도 마찬가지이다. (컨트롤러가 둘 이상인 경우, 일반적으로 그 중 하나를 제외한 모든 컨트롤러가 중재를 잃게 된다.)

컨트롤러는 클럭 라인이 하이 상태가 되는 것을 관찰할 때까지, 그리고 클럭을 다시 로우로 당기기 전에 추가적인 최소 시간(표준 100 kbit/s I²C의 경우 4 μs)을 기다려야 한다.

컨트롤러 또한 원하는 만큼 SCL 라인을 로우 상태로 유지할 수 있지만(프로토콜 개정판 6부터는 허용되지 않음), "클럭 스트레칭"이라는 용어는 일반적으로 대상이 이를 수행할 때만 사용된다. 이론적으로는 모든 클럭 펄스를 스트레칭할 수 있지만, 일반적으로 어큐뮬레이션 비트 전후의 간격이 사용된다. 예를 들어, 대상이 마이크로컨트롤러인 경우, 해당 I²C 인터페이스는 소프트웨어가 긍정적인 어큐뮬레이션 또는 NACK을 보낼지 결정할 때까지 각 바이트 후 클럭을 스트레칭할 수 있다.

클럭 스트레칭은 I²C에서 대상이 SCL을 구동하는 유일한 경우이다. 많은 대상은 클럭 스트레칭을 할 필요가 없으므로 SCL을 구동하는 회로 없이 엄격하게 입력으로 취급한다. 맞춤형 ASIC 내부에 있는 것과 같은 일부 컨트롤러는 클럭 스트레칭을 지원하지 않을 수 있으며, 종종 이러한 장치는 "2선 인터페이스"로 표시되며 I²C가 아니다.

최소 버스 처리량을 보장하기 위해, SMBus는 클럭을 스트레칭할 수 있는 거리에 제한을 둔다. 이러한 제한을 준수하는 호스트와 대상은 짧은 시간 이상 버스에 대한 접근을 차단할 수 없으며, 이는 순수한 I²C 시스템에서 보장되지 않는다.

모든 컨트롤러는 버스를 모니터링하여 시작 비트와 정지 비트를 확인하고, 다른 컨트롤러가 버스를 사용 중일 때는 메시지를 시작하지 않는다. 그러나 두 개의 컨트롤러가 거의 동시에 전송을 시작할 수 있으며, 이 경우 중재가 발생한다. 대상 전송 모드도 중재될 수 있으며, 컨트롤러가 여러 대상을 주소 지정할 때 발생하지만, 이는 덜 일반적이다. 재시도 전에 무작위 백오프 지연을 사용하는 이더넷과 같은 프로토콜과 달리, I2C는 결정적 중재 정책을 가지고 있다. 각 송신기는 데이터 라인(SDA)의 레벨을 확인하고 예상하는 레벨과 비교한다. 일치하지 않으면 해당 송신기는 중재에서 지고 이 프로토콜 상호 작용에서 탈락한다.

하나의 송신기가 SDA를 1로 설정하고(신호를 구동하지 않음) 두 번째 송신기가 0으로 설정하면(접지로 풀) 라인이 로우가 된다. 그런 다음 첫 번째 송신기는 라인 레벨이 예상과 다르다는 것을 관찰하고 다른 노드가 전송 중이라고 결론을 내린다. 이러한 차이를 가장 먼저 알아차린 노드가 중재에서 지는 노드이다. 즉, SDA 구동을 중단한다. 컨트롤러인 경우 SCL 구동도 중단하고 STOP을 기다린다. 그런 다음 전체 메시지를 다시 발행하려고 시도할 수 있다. 그동안 다른 노드는 SDA에서 예상 수준과 실제 수준 간의 차이를 알아차리지 못하므로 전송을 계속한다. 지금까지 신호가 예상대로 정확했기 때문에 아무런 문제 없이 전송을 할 수 있다. 다른 송신기가 메시지를 방해한 적이 없다.

두 컨트롤러가 서로 다른 두 대상에게 메시지를 보내는 경우, 낮은 대상 주소를 보내는 컨트롤러가 주소 단계에서 항상 중재에서 "승리"한다. 두 컨트롤러가 동일한 대상 주소로 메시지를 보낼 수 있고, 주소가 때때로 여러 대상을 참조하므로 중재는 때때로 데이터 단계까지 계속되어야 한다.

중재는 매우 드물게 발생하지만, 적절한 다중 컨트롤러 지원에 필요하다. 클럭 스트레칭과 마찬가지로, 모든 장치가 중재를 지원하는 것은 아니다. 중재를 지원하는 장치는 일반적으로 "다중 컨트롤러" 통신을 지원한다고 표시한다.

다중 컨트롤러 I2C 구현에서 주의해서 처리해야 하는 한 가지 경우는 컨트롤러가 서로 통신하는 경우이다. 한 컨트롤러가 들어오는 메시지에 대한 중재에서 질 수 있으며, 자신의 주소를 승인하기 위해 컨트롤러에서 대상으로 역할을 변경해야 한다.

극히 드문 경우지만, 두 컨트롤러가 동시에 동일한 메시지를 보내면 둘 다 통신이 성공적이라고 간주하지만 대상은 하나의 메시지만 보게 된다. 이러한 이유로 여러 컨트롤러에서 대상에 액세스할 수 있는 경우, 대상에서 인식하는 모든 명령은 멱등성이 있거나 두 컨트롤러에서 동시에 발행되지 않도록 보장해야 한다. (예를 들어, 하나의 컨트롤러에서만 발행되는 명령은 멱등일 필요가 없으며, 특정 명령이 어떤 상호 배타적 메커니즘이 한 번에 하나의 컨트롤러만 해당 명령을 발행하도록 보장할 때 멱등일 필요도 없다.)

다음은 I²C 메시지 중에 발생할 수 있는 다양한 원자 상태와 비트 연산을 보여주는 표이다.유형 비활성 버스 (N) 시작 (S) 유휴 (i) 정지 (P) 클럭 스트레칭 (CS) 비고 중재 주장 가능 버스 주장 (컨트롤러) 버스 점유 (컨트롤러) 버스 해제 (컨트롤러) 대상에 의해 일시 중지됨 SDA 수동 풀업 하강 에지 (컨트롤러) 낮게 유지 (컨트롤러) 상승 에지 (컨트롤러) 무관 SCL 수동 풀업 수동 풀업 수동 풀업 수동 풀업 낮게 유지 (대상) 유형 하나의 데이터 비트 (1) (0) 전송 수신자 ACK 비트 응답 수신자 NACK 비트 응답 비트 설정 (Bs) 샘플링 준비 (Bx) 비트 설정 (Bs) ACK (A) 비트 설정 (Bs) NACK (A') 비고 송신자 비트 설정 (컨트롤러/대상) 수신자 비트 샘플링 (컨트롤러/대상) 송신자 hi-Z 송신자는 SDA가 낮음을 확인 송신자 hi-Z 송신자는 SDA가 높음을 확인 SDA 비트 설정 (SCL 하강 후) 비트 캡처 (SCL 상승 후) 수신자에 의해 낮게 유지 (SCL 하강 후) 수신자에 의해 높게 구동됨 (또는 수동 하이) (SCL 하강 후) SCL 하강 에지 (컨트롤러) 상승 에지 (컨트롤러) 하강 에지 (컨트롤러) 상승 에지 (컨트롤러) 하강 에지 (컨트롤러) 상승 에지 (컨트롤러) 유형 ACK/NACK 이후 (Sr) 신호 설정 반복 시작 (Sr) 비고 ACK에서 시작 정지 (P) 상태 방지 NACK에서 시작 시작 (S) 신호와 동일 SDA ACK에 대해 낮게 유지됨 상승 에지 수동 하이 수동 하이 하강 에지 (컨트롤러) SCL 하강 에지 (컨트롤러) 낮게 유지 상승 에지 (컨트롤러) 수동 하이 수동 풀업

데이터 전송 순서는 다음과 같다.

1. 데이터 전송은 SCL이 하이 상태를 유지하는 동안 SDA가 로우로 풀링되어 신호되는 ''시작'' 조건(S)으로 시작된다.

2. SCL이 로우로 풀링되고 SDA는 SCL을 로우 상태로 유지하면서 첫 번째 데이터 비트 레벨을 설정한다(파란색 막대 시간 동안).

3. 데이터는 SCL이 첫 번째 비트(B1)에 대해 상승할 때 샘플링(수신)된다. 비트가 유효하려면 SDA는 SCL의 상승 에지에서 다음 하강 에지 사이(전체 녹색 막대 시간)에 변경되어서는 안 된다.

4. 이 프로세스가 반복된다. SCL이 로우인 동안 SDA가 전환되고 SCL이 하이인 동안 데이터가 읽힙니다(B2에서 Bn까지).

5. 마지막 비트 다음에는 클럭 펄스가 이어지며, 이 동안 SDA는 ''정지'' 비트를 준비하기 위해 로우로 풀링된다.

6. ''정지'' 조건(P)은 SCL이 상승하고 SDA가 상승할 때 신호된다.

잘못된 마커 감지를 방지하기 위해 SCL 하강 에지와 SDA 변경 사이, 그리고 SDA 변경과 SCL 상승 에지 사이에 최소 지연이 있다. 최소 지연 시간은 사용 중인 데이터 전송 속도에 따라 달라진다. 데이터 비트(응답 포함)를 포함하는 I2C 메시지는 클럭 펄스를 포함한다.

3. 2. 메시지 프로토콜

I²C 버스는 메시지 구분을 위해 데이터 비트와 구별되는 특수한 START 및 STOP 신호를 사용한다. 각 I²C 트랜잭션은 여러 메시지로 구성될 수 있으며, 각 트랜잭션은 START로 시작하고 STOP으로 종료된다.[4]

I²C 트랜잭션의 유형은 다음과 같다.

결합된 트랜잭션에서 각 읽기 또는 쓰기는 START와 타겟 주소로 시작한다. 첫 번째 이후의 START 조건은 ''반복된 START'' 비트라고도 하며, STOP 조건 없이 이어져 타겟이 다음 메시지가 동일한 트랜잭션의 일부임을 알 수 있다.

순수 I²C 시스템은 임의의 메시지 구조를 지원하지만, SMBus는 단일 타겟을 포함하는 몇 가지 구조로 제한된다. PMBus는 SMBus를 확장하여 여러 SMBus 트랜잭션을 하나의 결합된 메시지로 보낼 수 있게 한다.

대부분의 타겟(슬레이브)은 요청-응답 제어 모델을 채택하며, 쓰기 명령 다음에 오는 하나 이상의 바이트는 명령 또는 주소로 처리된다. 예를 들어, ST마이크로일렉트로닉스의 M24C08-BN6[4]과 같은 24C32형 EEPROM은 어드레스 하이(Address High)와 어드레스 로우(Address Low)라는 두 개의 요청 바이트를 사용한다. 이 바이트들은 EEPROM 주소 공간 내의 바이트를 어드레싱하는 데 사용된다.

EEPROM에 데이터를 쓰고 읽는 프로토콜은 다음과 같다.

I²C ''트랜잭션''은 하나 이상의 ''메시지''로 구성된다. 각 메시지는 시작 신호로 시작하며, 트랜잭션은 정지 신호로 끝난다. 첫 번째 이후의 시작 신호는 ''반복 시작'' 신호라고 불린다. 단일 메시지로 구성된 트랜잭션은 읽기 또는 쓰기 트랜잭션, 여러 메시지로 구성된 트랜잭션은 결합된 트랜잭션이다. 많은 I²C 장치는 결합된 트랜잭션과 동일한 메시지를 별도의 트랜잭션으로 보낸 것을 구별하지 않지만, 장치 ID 프로토콜과 같이 단일 트랜잭션을 필요로 하는 경우도 있다.

3. 3. 주소 지정 구조

I²C 레퍼런스 디자인은 7비트 주소 공간을 가지며, 이 중 16개는 예약되어 있어 동일한 버스에 최대 112개의 노드를 연결할 수 있다. 10비트 주소 지정을 통해 최대 1008 노드까지 연결 가능하다.[4]

7비트 주소 지정 방식에서는 7비트 주소와 1비트 읽기/쓰기(R/W') 지시자를 사용한다. 10비트 주소 지정은 10비트 주소 공간 확장을 제공한다.

I²C 주소는 특수 기능을 위해 예약된 주소들이 존재한다.

| 예약된 주소 색인 | 7비트 주소 (MSB) | 7비트 주소 (LSB) | R/W 값 | 설명 |

|---|---|---|---|---|

| 1 | 0000 | 000 | 0 | 일반 호출 |

| 2 | 0000 | 000 | 1 | 시작 바이트 |

| 3 | 0000 | 001 | X | CBUS 주소 |

| 4 | 0000 | 010 | X | 다른 버스 형식을 위해 예약됨 |

| 5 | 0000 | 011 | X | 미래를 위해 예약됨 |

| 6 | 0000 | 1XX | X | HS 모드 컨트롤러 코드 |

| 7 | 1111 | 1XX | 1 | 장치 ID |

| 8 | 1111 | 0XX | X | 10비트 대상(슬레이브) 주소 지정 |

나머지 112개의 주소는 특정 클래스의 장치용으로 지정되어 있으며, 그 중 일부는 관련 표준 또는 일반적인 사용에 따라 추가로 예약된다.[18][19][20][21][22]

SMBus는 몇 가지 추가 주소를 예약한다. 특히 `0001 000`은 SMBus 호스트용으로 예약되어 컨트롤러 지원 장치에서 사용될 수 있으며, `0001 100`은 대역 외 인터럽트 후 호스트에서 폴링되는 "SMBus 경고 응답 주소"이며, `1100 001`은 동적 주소 할당이 가능한 장치에서 처음에 사용되는 기본 주소이다.

MSB `1111`은 장치 ID 및 10비트 대상(슬레이브) 주소 지정을 위해 예약되어 있지만, 포인팅 장치와 같은 VESA DDC 디스플레이 종속 장치에서도 사용된다.[21]

4. 운영 체제 지원

리눅스에서는 I²C를 특정 장치에 대한 커널 모듈로 처리한다. I²C 클라이언트 작성 방법은 커널 관련 문서와 `/usr/include/linux/i2c.h` 헤더 파일에서 찾아볼 수 있다.

OpenBSD, FreeBSD, NetBSD는 I²C 프레임워크를 제공하며, 일반적인 마스터 컨트롤러 및 센서를 지원한다.

AmigaOS는 ''i2c.library'' 공유 라이브러리를 통해 I²C를 지원한다.

eCos, ChibiOS/RT, Zephyr OS, Unison OS는 여러 하드웨어 아키텍처에서 I²C를 지원한다.

아두이노 개발자는 "Wire" 라이브러리를 사용할 수 있다.

CircuitPython 및 MicroPython 개발자는 각각 busio.I2C 또는 machine.I2C 클래스를 사용할 수 있다.

윈도우, 윈도우 CE, macOS에서 I²C는 각 장치 드라이버에 의해 구현된다.

Sinclair QDOS, Minerva, RISC OS 등 다양한 운영 체제에서도 지원된다.

5. 개발 도구

I²C를 사용하여 시스템을 개발하거나 문제를 해결할 때, 하드웨어 신호 수준을 파악하는 것이 중요할 수 있다.

- 호스트 어댑터: 리눅스, Mac 또는 Windows를 실행하는 호스트 컴퓨터에 I²C 컨트롤러 또는 대상 장치를 연결하기 위한 여러 I²C 호스트 어댑터 하드웨어 솔루션이 있다. 대부분 USB-to-I²C 어댑터 형태이며, 일부는 독점 드라이버나 API 없이 사용할 수 있다.

- 프로토콜 분석기: I²C 버스를 샘플링하고 전기 신호를 디코딩하여 버스에서 전송되는 데이터에 대한 상위 수준 보기를 제공하는 도구이다.

- 로직 분석기: 신호를 수집, 분석, 디코딩 및 저장하는 도구로, 사용자는 고속 파형을 자세히 볼 수 있다. 각 신호 레벨 변경의 타임 스탬프를 표시하여 프로토콜 문제를 찾는 데 도움을 준다. 대부분의 로직 분석기는 버스 신호를 상위 레벨 프로토콜 데이터로 디코딩하고 ASCII 데이터를 표시하는 기능을 갖추고 있다.

6. 파생 기술

ACCESS.bus, VESA의 디스플레이 데이터 채널 (DDC), 시스템 관리 버스(SMBus), 지능형 플랫폼 관리 인터페이스(IPMI)는 I²C를 기반으로 하는 기술이다. 이러한 기술들은 전압, 클럭 주파수, 인터럽트 신호 등에서 차이를 보인다.[39]

Atmel 등에서 사용하는 TWI (Two-Wire Interface) 또는 TWSI (Two-Wire Serial Interface)도 기본적으로 I²C와 동일한 버스이다.[39]

7. 응용

I²C는 빠른 속도를 필요로 하지 않는 간단하고 저렴한 주변 장치들에 적합하다. I²C 버스가 사용되는 주된 응용 분야는 다음과 같다.

- 사용자 설정값을 저장하기 위해 NVRAM에 접근하는 경우

- 저속의 디지털-아날로그 변환회로에 접근하는 경우

- 저속의 아날로그-디지털 변환회로에 접근하는 경우

- 모니터의 명암, 대비, 색상 등을 변경하는 경우

- 지능형 스피커의 볼륨값을 변경하는 경우

- 휴대전화같은 장치에 포함된 발광 다이오드를 제어하는 경우

- 중앙 처리 장치 온도나 팬 속도와 같은 하드웨어 모니터링 정보나 진단 센서 정보를 읽는 경우

- 실시간 클럭 값을 읽는 경우

- 시스템 요소의 전원을 제어하는 경우

- DRAM의 버스 타이밍 설정 저장 (Serial Presence Detect|SPD영어)

- 2차 전지의 충전/방전 상태 컨트롤러의 통신 인터페이스 (스마트 배터리 시스템)

I²C의 장점은 특히 마이크로컨트롤러에서 단지 2개의 일반 목적 입출력 핀과 소프트웨어만을 이용하여 여러 장치들을 제어할 수 있다는 점이다. 주변 장치들은 시스템이 동작 중일 때도 I²C 버스에 추가/제거될 수 있으며, 이것은 핫 스왑이 필요한 요소들을 이용하는 응용에 적합하다.

8. 장점

마이크로컨트롤러에서 단 2개의 일반 목적 입출력(GPIO) 핀과 소프트웨어만으로 여러 장치를 제어할 수 있다는 점이 I²C의 큰 장점이다.

시스템이 동작 중일 때도 I²C 버스에 주변 장치를 추가/제거할 수 있는데, 이는 핫 스왑이 필요한 경우에 적합하다.

컴퓨터 엔지니어들은 칩의 패키지 크기와 핀 수가 생산 비용과 IC 설계에 영향을 준다는 것을 인식한 후부터 I²C와 같은 버스를 널리 사용하였다. 또한 작은 패키지는 일반적으로 더 적은 전력을 소모하므로, 휴대전화나 이동형 장치에 사용하기에 편리하다.[53]

9. 한계

I²C는 몇 가지 한계점을 가지고 있어, 실제 사용 시 주의가 필요하다.

- 주소 충돌 가능성: I²C는 기본적으로 7비트 주소를 사용하는데, 이는 수천 개의 다양한 장치가 사용될 경우 주소가 충돌될 가능성이 있다. 이러한 문제를 해결하기 위해 제조업체들은 장치마다 몇 개의 주소 옵션을 제공하여 주소 설정을 가능하게 하지만, 여전히 제한적이다.[35][36][37]

- 10비트 주소 미지원: 10비트 I²C 주소는 아직 널리 사용되지 않고, 많은 호스트 운영 체제에서 지원되지 않는다.[38]

- 버스 구성 문제: 런타임에 장치 유형을 감지하는 것이 어렵기 때문에, 시스템 펌웨어에서 제공하는 테이블과 같은 대역 외 메커니즘이 필요하다.

- 제한적인 속도 지원: 멀티 메가비트 속도를 지원하는 호스트는 드물며, 많은 장치들이 400 kbit/s 속도를 지원하지 않는다.

- 버스 커패시턴스: 버스 커패시턴스는 전송 속도를 제한하며, 특히 전류원을 사용하여 신호 상승 시간을 줄이지 않을 경우 더욱 그렇다.

- 공유 버스 특성: I²C는 공유 버스이므로, 한 장치에서 오류가 발생하면 전체 버스가 정지될 수 있다.

이러한 주소 관리, 버스 구성, 잠재적 오류, 속도 등의 문제로 인해, 실제로는 I²C 버스 세그먼트 당 연결되는 장치 수가 제한적이다.

참조

[1]

웹사이트

Financial Press Releases-NXP

http://investors.nxp[...]

2018-04-29

[2]

웹사이트

MCP23008

https://www.microchi[...]

2021-05-26

[3]

웹사이트

7-bit, 8-bit, and 10-bit I2C Slave Addressing

https://www.totalpha[...]

2018-04-29

[4]

웹사이트

8-Kbit serial I2C bus EEPROM (PDF)

https://www.st.com/r[...]

2019-11-19

[5]

간행물

Using The ZONE_READ And ZONE_WRITE Protocols

http://pmbus.org/Ass[...]

System Management Interface Forum

2016-01-07

[6]

웹사이트

Is there any definitive I2C pin-out guidance out there? Not looking for a "STANDARD"

http://electronics.s[...]

StackExchange

[7]

Citation

NXP Application note AN11075: Driving I2C-bus signals over twisted pair cables with PCA9605

http://www.nxp.com/d[...]

2017-08-16

[8]

Citation

Taking the leap off board: An introduction to I2C over long wires

http://hackaday.com/[...]

2017-08-16

[9]

Citation

iPack Stackable Board Format

http://www.mcc-us.co[...]

2017-08-19

[10]

서적

Building Robots with LEGO Mindstorms NXT

https://books.google[...]

Syngress

2018-04-29

[11]

Citation

Chapter 13: I2C Bus Communication

https://books.google[...]

2010

[12]

webarchive

NXT connector plug

http://www.philohome[...]

2017-08-20

[13]

webarchive

I2C Interfacing Part 1: Adding Digital I/O Ports

http://www.tau.ac.il[...]

2017-08-12

[14]

webarchive

Sending I2C reliabily over Cat5 cables

https://electronics.[...]

2017-08-18

[15]

webarchive

I2C Bus Connectors & Cables

https://www.i2cchip.[...]

2017-08-18

[16]

웹사이트

Multiple I2C buses · Testato/SoftwareWire Wiki

https://github.com/T[...]

[17]

웹사이트

Sharing I2C bus | Microchip

https://www.microchi[...]

[18]

웹사이트

I2C Address Allocation Table

https://web.archive.[...]

Philips Semiconductors

1999-08-24

[19]

문서

Data Handbook IC12: I2C Peripherals

Philips

[20]

웹사이트

System Management Bus (SMBus) Specification

http://www.smbus.org[...]

System Management Interface Forum

2014-12-20

[21]

웹사이트

VESA Display Data Channel Command Interface (DDC/CI) Standard

http://www.chrisbot.[...]

VESA

2004-10-29

[22]

웹사이트

Intelligent Platform Management Interface Specification Second Generation V2.0

https://www.intel.co[...]

Intel, NEC, Hewlett-Packard & Dell

2013-10-01

[23]

webarchive

TWI Master Bit Band Driver

http://www.atmel.com[...]

2017-03-29

[24]

webarchive

i2c.resource component

http://www.os4depot.[...]

2011-07-24

[25]

웹사이트

/sys/dev/i2c/i2c_scan.c#probe_val

http://bxr.su/o/sys/[...]

OpenBSD

2015-05-29

[26]

논문

OpenBSD Hardware Sensors — Environmental Monitoring and Fan Control.

http://cnst.su/MMath[...]

UWSpace

2010-05-21

[27]

문서

Introduction to HID over I2C

https://docs.microso[...]

[28]

문서

https://docs.zephyrp[...]

[29]

문서

https://hackaday.com[...]

[30]

문서

https://www.sparkfun[...]

[31]

웹사이트

Qwiic Connect System — Frequently Asked Questions

https://www.sparkfun[...]

SparkFun Electronics

2024-12-20

[32]

문서

https://learn.adafru[...]

[33]

문서

https://www.cable-te[...]

[34]

문서

https://www.cable-te[...]

[35]

webarchive

Linear Technology's LTC4151

http://cds.linear.co[...]

2017-08-09

[36]

PDF

Maxim's MAX7314

https://datasheets.m[...]

[37]

PDF

TI's UCD9224

http://www.ti.com/li[...]

[38]

메일링 리스트

Re: [PATCH 4/5] add i2c_probe_device and i2c_remove_device

https://lkml.org/lkm[...]

2005-08-16

[39]

웹사이트

avr-libc: Example using the two-wire interface (TWI)

http://www.nongnu.or[...]

[40]

웹사이트

TESS -- Error

2018-04-29

[41]

웹사이트

What is TWI? How to Configure the TWI for I2C Communication

http://ww1.microchip[...]

Microchip Technology

[42]

웹사이트

The improved inter-integrated circuit (I3C)

https://www.microcon[...]

2017-11-29

[43]

특허

Two-Wire Bus-System Comprising A Clock Wire And A Data Wire For Interconnecting A Number Of Stations

https://patents.goog[...]

[44]

웹사이트

Philips sues eight more companies for infringement of I2C bus patent

https://www.eetimes.[...]

EE Times

2001-10-17

[45]

웹사이트

I2C-bus specification Rev 2.0; Philips Semiconductors; December 1998; Archived.

https://web.archive.[...]

[46]

웹사이트

I2C-bus specification Rev 2.1; Philips Semiconductors; January 2000; Archived.

https://web.archive.[...]

[47]

웹사이트

I2C-bus specification Rev 3; NXP Semiconductors; June 19, 2007; Archived.

https://web.archive.[...]

[48]

웹사이트

I2C-bus specification Rev 4; NXP Semiconductors; February 13, 2012; Archived.

https://web.archive.[...]

[49]

웹사이트

I2C-bus specification Rev 5; NXP Semiconductors; October 9, 2012; Archived.

https://web.archive.[...]

[50]

웹사이트

I2C-bus specification Rev 6

https://www.nxp.com/[...]

NXP Semiconductors

2014-04-04

[51]

웹사이트

I2C-bus specification Rev 7

https://www.nxp.com/[...]

NXP Semiconductors

2021-10-01

[52]

학술지

2線シリアル・インターフェースI2C詳解

CQ出版

2014-10-01

[53]

웹사이트

かふぇルネ I2Cの伝送可能距離

http://japan.renesas[...]

2016-09-12

[54]

웹사이트

I2C-bus specification and user manual

http://www.nxp.com/d[...]

NXPセミコンダクターズ

2021-10-01

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com