MOSFET

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

MOSFET(금속 산화막 반도체 전계 효과 트랜지스터)는 1925년 최초로 특허를 받았으며, 1960년에 벨 연구소에서 작동하는 MOS 장치가 시연되었다. MOSFET은 게이트 전압에 의해 제어되는 저항처럼 동작하며, 소형화, 저전력 소모, 높은 집적도 등의 장점으로 인해 디지털 및 아날로그 집적 회로에 널리 사용된다. MOSFET은 소스, 드레인, 게이트, 바디의 4개 단자로 구성되며, 단자 전압에 따라 차단, 선형 영역, 포화 영역의 세 가지 동작 영역으로 구분된다. MOSFET의 종류로는 이중 게이트 MOSFET, 공핍형 MOSFET, 전력 MOSFET 등이 있다.

더 읽어볼만한 페이지

- 트랜지스터 - CMOS

CMOS는 상보적 금속 산화막 반도체의 약자로, 저전력 소비를 특징으로 하며, P형과 N형 MOSFET을 결합하여 논리 게이트를 구현하는 디지털 회로 설계 방식 및 공정 계열이다. - 트랜지스터 - 트랜지스터 라디오

트랜지스터 라디오는 트랜지스터를 사용하여 소형화, 저전력화를 통해 휴대성을 높인 라디오로, 1950년대 상업화 이후 대중적인 전자 통신 장치로 자리매김하며 라디오 방송과 청취 방식에 큰 영향을 미쳤으나, 휴대용 오디오 플레이어 등장 이후 인기가 감소하였다. - MOSFET - CMOS

CMOS는 상보적 금속 산화막 반도체의 약자로, 저전력 소비를 특징으로 하며, P형과 N형 MOSFET을 결합하여 논리 게이트를 구현하는 디지털 회로 설계 방식 및 공정 계열이다. - MOSFET - 전자 이동도

전자 이동도는 전기장 내에서 전자의 평균 이동 속도를 나타내는 물리량으로, 재료의 불순물 농도와 온도에 의존하며, 다양한 산란 메커니즘과 측정 방법을 통해 연구되고 반도체 소자 성능에 중요한 영향을 미친다.

| MOSFET | |

|---|---|

| MOSFET 정보 | |

| 기본 정보 | |

| 종류 | 전계 효과 트랜지스터 |

| 같이 보기 | |

| 관련 항목 | 전계 효과 트랜지스터 MOSFET 증폭기 |

2. 역사

전계 효과 트랜지스터의 기본 원리는 1925년 줄리어스 에드가 릴리엔펠트가 최초로 특허를 받았다.[2] 1934년에는 발명가 오스카어 하일이 유럽에서 독자적으로 유사한 장치에 대한 특허를 받았다.[3]

1940년대, 벨 연구소 과학자 윌리엄 쇼클리, 존 바딘, 월터 하우저 브래튼은 전계 효과 장치를 만들려고 시도했으나, 표면 상태 문제, 즉 전자를 정지 상태로 유지하는 반도체 표면의 트랩 때문에 예상했던 효과를 보이지 못했다. 이로 인해 BJT와 싸이리스터 트랜지스터만 제작할 수 있었다.

1955년, 칼 프로슈와 링컨 데릭은 실리콘 웨이퍼 위에 실리콘 이산화물 층을 우연히 성장시켰다.[4][5] 1957년까지 프로슈와 데릭은 마스크와 전침착을 사용하여 드레인과 소스가 같은 표면에 인접한 평면 트랜지스터를 제작할 수 있었다.[6] 그들은 실리콘 이산화물이 실리콘 웨이퍼를 절연하고 보호하며 도펀트가 웨이퍼로 확산되는 것을 방지한다는 것을 보여주었다.[4][7] 그들의 연구 결과는 1957년에 발표되기 전에 BTL 메모 형태로 벨 연구소에 배포되었다. 쇼클리 반도체에서 쇼클리는 1956년 12월에 자신의 고위 직원들에게 그들의 논문 사전 인쇄본을 배포했다.[8][9][10][11] J.R. 리겐자와 W.G. 스피처는 1960년에 열적으로 성장한 산화물의 메커니즘을 연구하고 고품질 Si/SiO2 스택을 제작했다.[12][13][14]

이 연구에 이어 모하메드 아탈라와 강대원은 1959년에 실리콘 MOS 트랜지스터를 제안했고,[15] 1960년에 벨 연구소 팀과 함께 작동하는 MOS 장치를 성공적으로 시연했다.[16][17] 이 연구는 릴리엔펠트로 시작된 수십 년간의 전계 효과 연구의 정점이었다.

1960년에 벨 연구소의 강대원과 마틴 아탈라는 금속 산화막 반도체 장효과 트랜지스터 (MOSFET)를 발명했다. 모스펫은 반도체 표면 위에 절연층을 얻은 다음 그 위에 금속 게이트 전극을 설치한다는 점에서 쇼클리의 트랜지스터와 이론상으로 달랐다. 모스펫은 반도체로는 결정 실리콘을 사용하였고 절연층으로는 열로 산화된 이산화규소를 사용하였다. 실리콘 모스펫은 저렴한 생산비와 집적하기 쉬운 기술적 이점을 지녔으며, 실리콘과 산화층 사이의 경계영역에 국부적인 전자 트랩 (경계 상태)을 생성하지 않아 이전 트랜지스터의 성능을 떨어뜨리던 특성을 제거하였다. 이러한 장점을 바탕으로 모스펫은 전자공학에서 주도적인 역할을 차지하게 되었으며, 오늘날 정보 사회의 뿌리인 대규모 집적회로를 떠받치는 중요한 발견이었다.

모스펫은 모든 실리콘 집적 회로의 기본요소가 되었다. 1920년대에 릴리언필드에 의하여 기본 소자가 창안됐지만,[83] 그는 소자를 만들기 위한 어떠한 기반도 없었다. 1950년대 후반에 맥칼딘과 호어니에 의하여 창안된 실리콘 평판 공정[84]과 킬비와 노이스[85]에 의하여 창안된 집적회로는 릴리언필드의 소자가 현대에 구현될 수 있도록 하는 기반을 제공하였다. 아탈라와 강[86]은 1950년대 후반에 현대의 모스펫을 설명하였고 홉스테인과 헤이만은 1963년[87]에 실리콘 평판 공정 플랫폼에서 모스펫의 구조에 대하여 설명하였다. 그러나 이 평판 모스펫은 쇼클리, 바딘, 브래튼에 의하여 개발된 접합형 트랜지스터 (BJT)에 비교해서 큰 의미를 가지지 못했다.[88]

3. 구조 및 특징

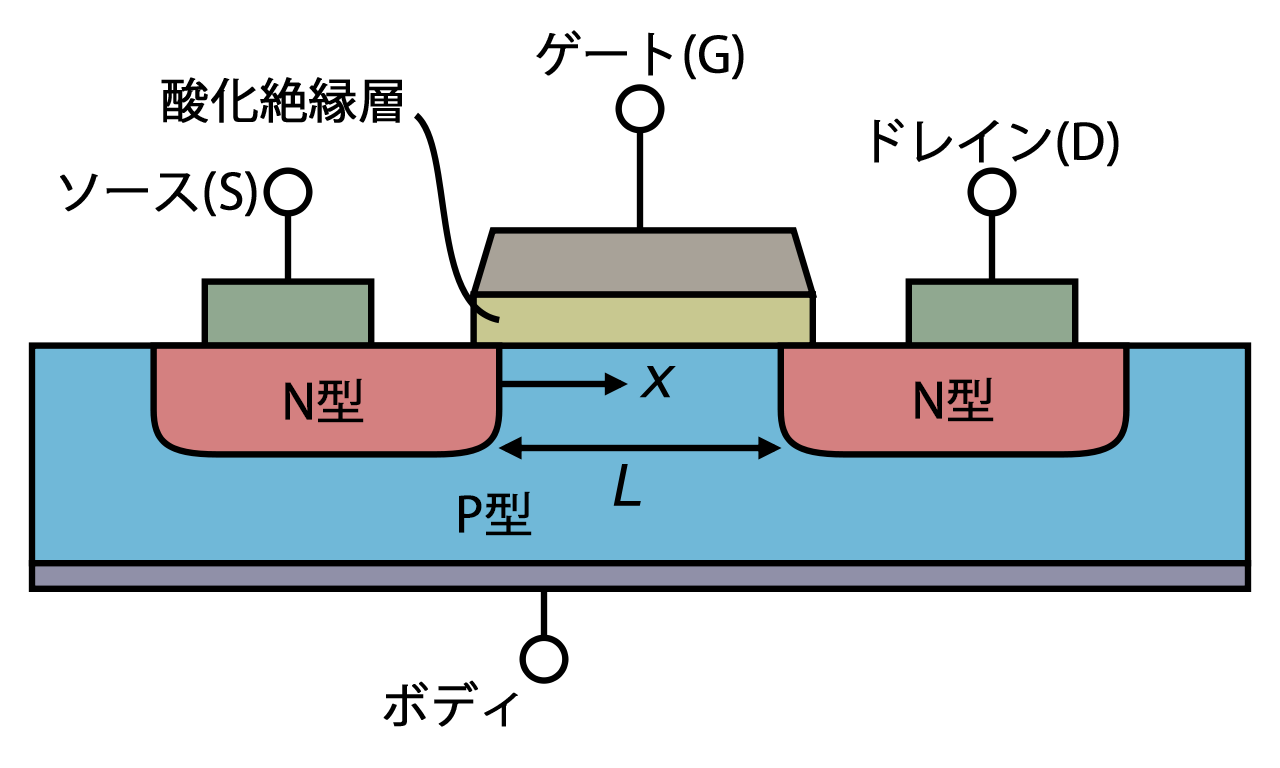

MOSFET(금속 산화막 반도체 장효과 트랜지스터)는 모스 축전기의 전하 농도 변화를 이용한다. 소스와 드레인 단자는 각각 고농도로 도핑된 영역에 연결되며, P형이나 N형이 될 수 있지만 둘 다 동일한 형태여야 한다. 고농도 도핑 영역은 도핑 형태에 따라 '+'로 표시된다. 이 두 영역은 반대 형(type)으로 도핑된 몸체(바디) 영역으로 분리되며, 몸체 영역은 고농도 도핑이 아니므로 '+' 기호가 없다. 게이트는 몸체 위에 위치하며 산화층으로 절연되어 모스 축전기를 구성하는 활성 영역이 된다.[22]

N채널 MOSFET(엔모스펫)의 경우, 소스와 드레인은 'N+' 영역이고 몸체는 'P' 영역이다. 양의 게이트-소스 전압(게이트에 양 전압, 소스에 음 전압)이 걸리면 P형 반도체 몸체와 N+ 도핑 접합부의 공핍층이 좁아지고, 산화층 아래 P 영역 표면에 전자가 축적되어 반전층(N채널)을 형성한다. 이 채널은 소스와 드레인 사이에 있지만, 게이트 전압이 소스에서 채널로 전자를 끌어당기기에 충분히 클 때만 전류가 흐른다. 게이트와 소스 사이에 0 또는 음의 전압이 걸리면 채널이 사라지고 소스와 드레인 사이에 전류가 흐르지 않는다.[22]

P채널 MOSFET(피모스펫)의 경우, 소스와 드레인은 'P+' 영역이고 몸체는 'N' 영역이다. 음의 게이트-소스 전압(게이트에 음 전압, 소스에 양 전압)이 걸리면 N형 반도체 내 P+ 도핑 접합부의 공핍층이 좁아져 산화층 아래 N 영역 표면에 정공이 축적되어 반전층(P채널)을 형성한다. 이 채널은 소스와 드레인 사이에 있지만, 게이트 전압이 소스에서 채널로 정공을 끌어당기기에 충분히 작을 때만 전류가 흐른다. 게이트와 몸체 사이에 0 근처 또는 양의 전압이 걸리면 채널이 사라지고 소스와 드레인 사이에 전류가 흐르지 않는다.[22]

소스는 채널을 통해 흐를 전하 운반자(N채널에서는 전자, P채널에서는 정공)가 샘솟는(source영어) 곳이라는 의미이다. 드레인(drain영어)은 전하 운반자가 채널을 빠져 나가는 곳이다.[22]

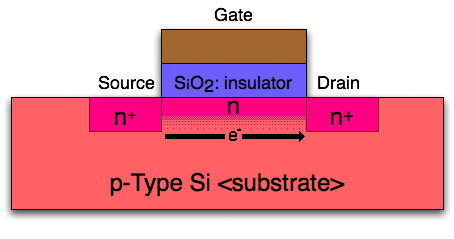

MOSFET은 일반적으로 p형 실리콘 기판 위에 제작된다. n형 MOS(NMOS)의 경우, p형 실리콘 기판 위의 게이트 영역에 실리콘 산화막과 그 위에 게이트 금속을 형성하고, 드레인·소스 영역에는 고농도의 불순물을 이온 주입하여 n형(n+형) 반도체로 만든다.[77]

p형 MOS(PMOS)의 경우에는, p형 실리콘 기판에 이온 주입으로 n층 영역을 생성하고, n형 주입 영역 중의 게이트 영역에 실리콘 산화막과 그 위에 게이트 금속을 형성하고, 드레인·소스 영역에는 고농도의 불순물을 다시 이온 주입하여 p형(p+형) 반도체로 만든다.[77]

과거에는 게이트 아래에 절연층을 가지는 구조적인 특징 때문에 동작 속도가 느리고 트랜스컨덕턴스(gm)가 낮은 문제가 있었다. 그러나 게이트 전류가 거의 흐르지 않고 공정이 비교적 간단하여 디지털 및 아날로그 회로에 널리 사용된다. 최근에는 게이트 길이 및 절연체 두께 감소, SOI 기술 등을 통해 동작 속도 및 gm 문제가 해결되고 있다. 인텔과 같은 기업에서는 고유전율(High-κ) 절연막과 메탈 게이트를 조합한 새로운 공정 기술을 개발하여 고성능, 저전력 IC 제작에 활용하고 있다.매개변수 nMOSFET pMOSFET 소스/드레인 유형 n형 p형 채널 유형 n형 p형 게이트 유형 폴리실리콘 n+ p+ 금속 φm ~ Si 전도띠 φm ~ Si 원자가띠 웰 유형 p형 n형 임계 전압, Vth 양수(증강형) 또는 음수(고갈형) 음수(증강형) 또는 양수(고갈형) 띠 굽힘 아래쪽 위쪽 반전층 캐리어 전자 정공 기판 유형 p형 n형

3. 1. 금속 산화막 반도체 구조

금속-산화막-반도체(MOS) 구조는 실리콘 기판 위에 이산화 규소(SiO₂) 층을 성장시키고, 그 위에 금속(주로 폴리실리콘이 사용됨) 층을 증착하여 만든다. 이산화 규소는 유전체 물질이기 때문에, 이 구조는 평행판 축전기에서 한쪽 전극을 반도체로 바꾼 것과 같다.

MOS 구조에 전압을 가하면 반도체 내 전하 분포가 바뀐다. P형 반도체(정공 밀도가 인)를 예로 들면, 게이트에 양의 전압()을 가하면 (그림 참조) 양공 농도는 줄어들고 전자 농도는 증가한다. 가 충분히 크면 게이트 근처에서 음전하 운반자(전자)의 농도가 양전하 운반자(정공)의 농도보다 높아지는데, 이 영역을 반전층이라고 한다.

이러한 P형 기판을 바탕으로 N형 MOSFET을 만들 수 있으며, 여기에 N형 소스와 드레인 영역을 추가하면 된다.

3. 2. MOS 커패시터 및 밴드 다이어그램

금속 산화막 반도체(MOS) 구조는 반도체 기판 위에 이산화 규소(Si)로 된 공핍층과 금속층(실제로 금속 대신에 폴리실리콘이 사용됨)을 쌓아서 만들어진다. 이산화 규소는 유전체 물질이므로, 평행판 축전기의 두 금속 전극 중 하나를 반도체로 대체한 것과 같은 구조이다.

MOS 구조에 전압을 가하면 반도체 내 전하 분포가 변한다. P형 반도체( 양공 밀도를 갖는)를 예로 들면, 양의 (그림 참조)를 가하면 양공 농도는 감소하고 전자 농도는 증가한다. 가 충분히 크면 게이트 근처에서 음전하 운반자(전자) 농도가 양전하 운반자(양공) 농도보다 높아지는데, 이를 반전층(inversion layer)이라고 한다. P형 몸체를 갖는 이 구조는 N형 MOSFET의 기본이 되며, 여기에 N형 소스와 드레인 영역을 추가해야 한다.

MOS 커패시터는 MOSFET의 핵심 구조이다. p형 실리콘 기판을 가진 MOS 커패시터를 예로 들어보자. 게이트에 양의 전압을 가하면, p형 기판 표면의 정공은 인가된 전압에 의해 생성된 전기장에 의해 밀려난다. 처음에는 정공이 밀려나고, 표면에는 고정된 음전하 수용체 원자가 남아 공핍 영역을 형성한다. 정공은 수용체 원자(예: 붕소)에 의해 생성되는데, 이 원자는 실리콘 원자보다 전자가 하나 적다. 정공은 실제로 밀려나는 것이 아니라, 전자가 양의 전기장에 끌려 정공을 채우면서 전자가 원자에 고정되어 움직이지 않기 때문에 전하 캐리어가 없는 공핍 영역이 생성된다.

게이트 전압을 계속 증가시키면, 공핍 영역 위의 표면이 p형에서 n형으로 바뀌는 지점이 생긴다. 이는 벌크 영역의 전자가 더 큰 전기장에 끌리기 시작하기 때문이다. 이것을 '반전'이라고 하며, 이 변환이 일어나는 임계 전압은 MOSFET에서 가장 중요한 매개변수 중 하나이다.

p형 MOSFET의 경우, 표면의 고유 에너지 준위가 표면의 페르미 준위보다 작아질 때 벌크 반전이 일어난다. 밴드 다이어그램에서 페르미 준위는 반도체의 유형을 정의한다. 페르미 준위가 고유 준위와 같으면 반도체는 고유형 또는 순수형이다. 페르미 준위가 전도대(가전자대)에 더 가까이 있으면 반도체 유형은 n형(p형)이 된다.

게이트 전압이 양의 방향으로 증가하면 고유 에너지 준위 밴드가 가전자대 쪽으로 아래쪽으로 휘어진다. 페르미 준위가 가전자대에 더 가까이 있으면(p형의 경우), 고유 준위가 페르미 준위를 교차하기 시작하는 지점이 있고, 전압이 임계 전압에 도달하면 고유 준위가 페르미 준위를 교차하는데, 이를 반전이라고 한다. 그 시점에서 반도체 표면은 p형에서 n형으로 반전된다. 페르미 준위가 고유 준위보다 높으면 반도체는 n형이므로, 반전 시 고유 준위가 페르미 준위(가전자대에 더 가까이 있음)에 도달하고 교차하면 페르미 에너지 준위와 고유 에너지 준위의 상대적 위치에 따라 표면에서 반도체 유형이 변한다.

3. 3. MOSFET 구조

금속 산화막 반도체 장효과 트랜지스터(MOSFET)는 모스 축전기의 전하 농도 변화를 이용한다. 소스와 드레인 단자는 각각 고농도로 도핑된 영역에 연결되며, P형이나 N형이 될 수 있지만 둘 다 동일한 형태여야 한다. 고농도 도핑 영역은 도핑 형태에 따라 '+'로 표시된다. 이 두 영역은 반대 형(type)으로 도핑된 몸체(바디) 영역으로 분리되며, 몸체 영역은 고농도 도핑이 아니므로 '+' 기호가 없다. 게이트는 몸체 위에 위치하며 산화층으로 절연되어 모스 축전기를 구성하는 활성 영역이 된다.

N채널 MOSFET(엔모스펫)의 경우, 소스와 드레인은 'N+' 영역이고 몸체는 'P' 영역이다. 양의 게이트-소스 전압(게이트에 양 전압, 소스에 음 전압)이 걸리면 P형 반도체 몸체와 N+ 도핑 접합부의 공핍층이 좁아지고, 산화층 아래 P 영역 표면에 전자가 축적되어 반전층(N채널)을 형성한다. 이 채널은 소스와 드레인 사이에 있지만, 게이트 전압이 소스에서 채널로 전자를 끌어당기기에 충분히 클 때만 전류가 흐른다. 게이트와 소스 사이에 0 또는 음의 전압이 걸리면 채널이 사라지고 소스와 드레인 사이에 전류가 흐르지 않는다.[22]

P채널 MOSFET(피모스펫)의 경우, 소스와 드레인은 'P+' 영역이고 몸체는 'N' 영역이다. 음의 게이트-소스 전압(게이트에 음 전압, 소스에 양 전압)이 걸리면 N형 반도체 내 P+ 도핑 접합부의 공핍층이 좁아져 산화층 아래 N 영역 표면에 정공이 축적되어 반전층(P채널)을 형성한다. 이 채널은 소스와 드레인 사이에 있지만, 게이트 전압이 소스에서 채널로 정공을 끌어당기기에 충분히 작을 때만 전류가 흐른다. 게이트와 몸체 사이에 0 근처 또는 양의 전압이 걸리면 채널이 사라지고 소스와 드레인 사이에 전류가 흐르지 않는다.[22]

소스는 채널을 통해 흐를 전하 운반자(N채널에서는 전자, P채널에서는 정공)가 샘솟는(source영어) 곳이라는 의미이다. 드레인(drain영어)은 전하 운반자가 채널을 빠져 나가는 곳이다.[22]

MOSFET은 본체 전극과 본체 위에 위치하고 게이트 유전체 층에 의해 다른 모든 소자 영역으로부터 절연된 게이트 전극 사이의 MOS 커패시턴스에 의한 전하 농도의 변조를 기반으로 한다. 산화물 이외의 유전체가 사용되는 경우, 이 소자는 금속-절연체-반도체 FET(MISFET)라고 할 수 있다. MOS 커패시터와 비교하여 MOSFET에는 본체 영역으로 분리된 두 개의 추가 단자(소스와 드레인)가 포함되어 있으며, 각각 개별적으로 고농도 도핑된 영역에 연결된다. 이러한 영역은 p형 또는 n형일 수 있지만, 모두 같은 형태여야 하며 본체 영역과는 반대 형태여야 한다. 소스와 드레인(본체와는 달리)은 도핑 유형 뒤에 "+" 기호가 붙어 있듯이 고농도로 도핑된다.[22]

반도체의 에너지 띠 점유는 페르미 준위의 위치가 반도체 에너지 띠 가장자리에 대한 상대적 위치에 의해 결정된다.[22]

충분한 게이트 전압을 사용하면 원자가띠 가장자리가 페르미 준위에서 멀리 떨어지고, 본체의 정공이 게이트에서 멀어진다.[22]

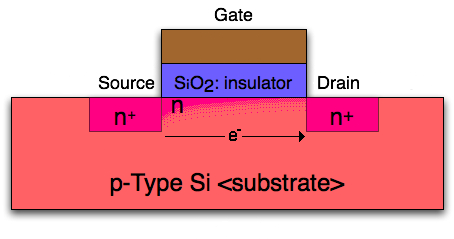

더 큰 게이트 바이어스에서, 반도체 표면 근처의 전도띠 가장자리는 페르미 준위에 가까워지고, p 영역과 산화물 사이의 계면에 ''반전층'' 또는 ''n채널''에 전자를 채운다. 이 전도 채널은 소스와 드레인 사이로 확장되며, 두 전극 사이에 전압이 인가되면 전류가 이 채널을 통해 전도된다. 게이트의 전압을 높이면 반전층의 전자 밀도가 높아지고, 따라서 소스와 드레인 사이의 전류 흐름이 증가한다. 임계값보다 낮은 게이트 전압의 경우, 채널은 약하게 채워지며, 소스와 드레인 사이에는 매우 작은 서브쓰레숄드 누설 전류만 흐를 수 있다.[22]

음의 게이트-소스 전압(양의 소스-게이트)을 인가하면 n채널의 경우와 유사하게 표면에 ''p채널''이 생성되지만, 전하와 전압의 극성은 반대이다. 임계값보다 덜 음의 전압(p채널의 경우 음의 전압)을 게이트와 소스 사이에 인가하면 채널이 사라지고 소스와 드레인 사이에는 매우 작은 서브쓰레숄드 전류만 흐를 수 있다. 이 소자는 매립 산화물이 얇은 반도체 층 아래에 형성된 절연체 위 실리콘 소자를 포함할 수 있다. 게이트 유전체와 매립 산화물 영역 사이의 채널 영역이 매우 얇으면, 이 채널은 얇은 반도체 층의 양쪽에 소스와 드레인 영역이 형성된 초박막 채널 영역이라고 한다. 다른 반도체 재료도 사용할 수 있다. 소스와 드레인 영역이 전부 또는 일부 채널 위에 형성되는 경우, 이를 상승 소스/드레인 영역이라고 한다.[22]

| 매개변수 | nMOSFET | pMOSFET | |

|---|---|---|---|

| 소스/드레인 유형 | n형 | p형 | |

| 채널 유형 | n형 | p형 | |

| 게이트 유형 | 폴리실리콘 | n+ | p+ |

| 금속 | φm ~ Si 전도띠 | φm ~ Si 원자가띠 | |

| 웰 유형 | p형 | n형 | |

| 임계 전압, Vth | 양수(증강형) 또는 음수(고갈형) | 음수(증강형) 또는 양수(고갈형) | |

| 띠 굽힘 | 아래쪽 | 위쪽 | |

| 반전층 캐리어 | 전자 | 정공 | |

| 기판 유형 | p형 | n형 | |

MOSFET은 일반적으로 p형 실리콘 기판 위에 제작된다. n형 MOS(NMOS)의 경우, p형 실리콘 기판 위의 게이트 영역에 실리콘 산화막과 그 위에 게이트 금속을 형성하고, 드레인·소스 영역에는 고농도의 불순물을 이온 주입하여 n형(n+형) 반도체로 만든다.[77]

p형 MOS(PMOS)의 경우에는, p형 실리콘 기판에 이온 주입으로 n층 영역을 생성하고, n형 주입 영역 중의 게이트 영역에 실리콘 산화막과 그 위에 게이트 금속을 형성하고, 드레인·소스 영역에는 고농도의 불순물을 다시 이온 주입하여 p형(p+형) 반도체로 만든다.[77]

4. 동작

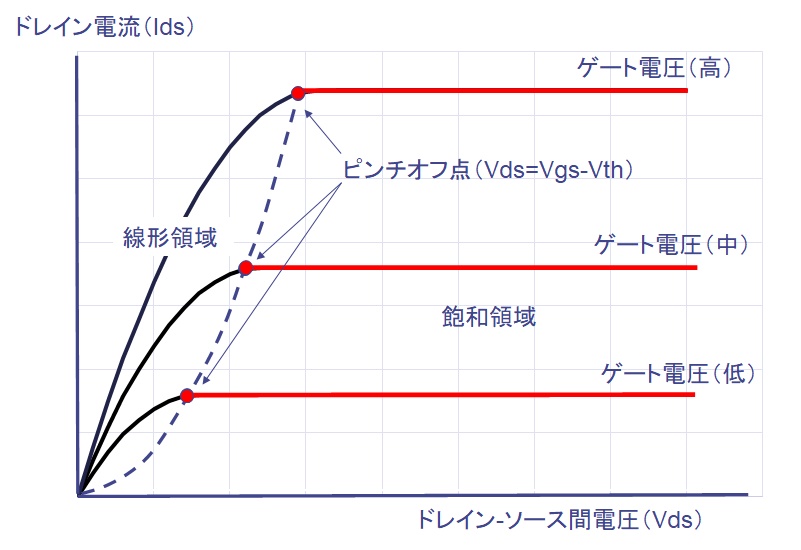

MOSFET의 동작은 게이트-소스 전압() 및 드레인-소스 전압()에 따라 크게 세 가지 영역으로 나뉜다.

- 차단 영역 (Cut-off): 가 문턱 전압 ()보다 낮을 때는 트랜지스터가 꺼져 있어 전류가 거의 흐르지 않는다. 하지만 실제로는 약간의 누설 전류가 존재할 수 있다.

- 선형 영역 (Linear): 가 보다 크고, 가 보다 작을 때는 트랜지스터가 켜져 전류가 흐른다. 이 영역에서 MOSFET은 저항처럼 동작하며, 드레인 전류()는 다음과 같이 표현된다.

::

::(: 전하 운반자 유효이동도, : 게이트 폭, : 게이트 길이, : 단위면적당 게이트 산화층 정전용량)

- 포화 영역 (Saturation): 가 보다 크고, 가 보다 클 때는 드레인 전류가 에 거의 영향을 받지 않고, 에 의해 주로 결정된다. 이 영역에서 MOSFET은 정전류원처럼 동작하며, 드레인 전류는 다음과 같이 표현된다.

::

::채널 길이 변조를 고려하면 위 식에 을 곱할 수 있다.

채널 길이 변조 효과는 채널의 길이가 짧아질수록 두드러지게 나타난다.

4. 1. 차단, 역문턱 및 약반전 모드

MOSFET영어의 동작은 단자에 걸리는 전압에 따라 세 가지 영역으로 나눌 수 있는데, 그 중 VGS가 문턱 전압(Vth)보다 낮은 '차단, 역문턱 및 약반전 모드'에서는 트랜지스터가 차단되어 드레인과 소스 사이에 전류가 거의 흐르지 않는다.기본적인 문턱 모델에 따르면 트랜지스터는 차단되고 드레인과 소스 사이에는 전류가 흐르지 않지만, 실제로는 소스에 있는 높은 에너지를 가진 일부 전자가 채널로 들어가 드레인으로 흐를 수 있다. 이로 인해 게이트-소스 전압의 지수 함수인 문턱아래 누설(subthreshold leakage영어)이라고 부르는 약한 반전 전류가 발생한다.[26][27]

소스가 벌크에 연결된 약한 반전 영역에서 전류는 VGS에 따라 지수적으로 변하며, 다음 식으로 나타낼 수 있다.

:

여기서 ID0는 VGS = Vth일 때의 전류, VT = kT/q는 열 전압, ''n''은 기울기 계수이다.

:

Cdep는 공핍층의 정전용량, Cox는 산화층의 정전용량이다.

소스가 벌크에 연결되지 않은 경우, 포화 상태의 드레인 전류에 대한 서브스레숄드 방정식은 다음과 같다.[28][29]

:

긴 채널 소자의 경우, VDS ≫ VT이면 전류에 대한 드레인 전압 의존성은 없지만, 채널 길이가 감소함에 따라 드레인 유기 장벽 저하로 인해 소자 구조에 복잡하게 의존하는 드레인 전압 의존성이 나타난다.

I-V 곡선은 문턱 전압에 따라 지수적으로 변하므로, 제조 변동에 민감하여 누설 전류와 성능 최적화가 복잡해진다.[34][35]

4. 2. 선형 영역 (옴 영역)

''V''GS > ''V''th이고 ''V''DS < ''V''GS - ''V''th인 경우, 트랜지스터가 켜지고 채널이 형성되어 드레인과 소스 사이에 전류가 흐른다. MOSFET은 게이트 전압에 의해 제어되는 저항처럼 동작하며, 드레인 전류는 게이트-소스 전압 및 드레인-소스 전압에 따라 결정된다. 드레인에서 소스로의 전류는 다음과 같이 표현된다.[36][37]:

여기서 는 전하 운반자의 유효이동도, 는 게이트 폭, 은 게이트 길이이고 는 단위면적당 게이트 산화층의 정전용량이다.

MOSFET에서는 게이트와 기판 사이에 구성된 캐패시터에 의해, 게이트에 양전압이 인가되면 p형 기판과 절연층의 계면에 전자를 끌어당겨 드레인-소스 간에 반전층(n형)을 만들어 소스-드레인 간의 높은 컨덕턴스를 확보한다. 드레인-소스 간 전압(''V''ds)이 비교적 낮고, 게이트-소스 간 전압(''V''gs)에서 문턱 전압(''V''th)을 뺀 값(''V''gs-''V''th)이 그것을 초과하는 영역을 선형 영역이라고 한다. 선형 영역에서는 게이트 전압에 비례하여 반전층의 두께가 증가하므로, 컨덕턴스가 게이트 전압에 비례하여 증가한다.[78]

4. 3. 포화 영역 (능동 모드)

MOSFET영어의 동작 영역 중 하나로, `VGS` > `Vth`이고 `VDS` ≥ (`VGS` - `Vth`)인 조건을 만족하는 영역이다.스위치가 켜지고 채널이 형성되어 드레인과 소스 사이에 전류가 흐른다. 드레인 전압이 소스 전압보다 높기 때문에 전자는 퍼지고, 전도는 좁은 채널을 통하는 것이 아니라 계면에서 멀어지고 기판 안쪽으로 더 깊이 확장되는 더 넓은 2차원 또는 3차원 전류 분포를 통해 이루어진다. 이 영역의 시작은 드레인 근처의 채널 영역 부족을 나타내는 핀치오프라고도 한다. 채널이 소자의 전체 길이로 확장되지는 않지만, 드레인과 채널 사이의 전기장은 매우 높고 전도는 계속된다.

드레인 전류는 이제 드레인 전압에 약하게 의존하고 주로 게이트-소스 전압에 의해 제어되며, 다음 수식으로 표현할 수 있다.

:

:채널 길이 변조를 고려하기 위해 위 식에 을 곱할 수 있다. 여기서,

::*는 전하 운반자의 유효이동도

::*는 게이트 폭

::*은 게이트 길이

::*는 단위면적당 게이트 산화층의 정전용량

::*λ는 채널 길이 변조 매개변수

이때문에 MOSFET은 정전류원으로 동작한다.

MOSFET에서는 게이트와 기판 사이에 구성된 캐패시터에 의해, 게이트에 양전압이 인가되면 p형 기판과 절연층의 계면에 전자를 끌어당겨 드레인-소스 간에 반전층(n형)을 만들어 소스-드레인 간의 높은 컨덕턴스를 확보한다. 드레인-소스 간 전압(`VDS`)이 게이트-소스 간 전압(`VGS`)에서 문턱 전압(`Vth`)을 뺀 값(`VGS`-`Vth`)을 상회하면 드레인 영역 근처에는 반전층이 형성되지 않는다. 이 상태를 핀치오프되었다고 한다. 이 상태(핀치오프)보다 드레인 전압이 높은 영역을 포화 영역이라고 하며, MOS의 컨덕턴스는 반전층의 길이에 따라 일정하게 결정된다. 이 상태에서는 정전류원으로 취급된다.

여기서 말하는 "포화 영역"이란 핀치오프된 후, 드레인 전압을 높여도 드레인 전류가 증가하지 않는 상태, 즉 전류값이 포화된 상태이며, 전자 속도가 포화되는 소위 전자의 속도 포화 현상과는 다르다.

채널 길이가 아주 짧아지면, 전하 운반자의 이동은 유사-탄도성 전달을 한다. 짧은 채널 효과가 크면, I-V 특성을 위의 방정식으로 근사시킬 수 없다. 차라리 포화 드레인 전류는 `VGS`의 이차 함수가 아니라 거의 일차 함수에 가깝다.[78]

미세 가공이 진행되어 채널 길이가 짧아지면, 드레인 전압을 높임에 따라 핀치오프 조건이 성립하는 장소가 드레인 단에서 소스 방향으로 이동함으로써, 실효적인 채널 길이가 짧아지고, 드레인 전류가 증가하는 효과가 나타난다. 이것을 채널 길이 변조 효과라고 하며, 바이폴라 트랜지스터의 얼리 효과에 상당한다. 채널 길이 변조 효과를 줄이려면, 가능한 한 채널 길이를 크게 설계할 필요가 있다.[79]

4. 4. 몸체 효과

몸체 효과는 소스와 벌크(기판) 사이의 전압(VSB) 변화로 인해 MOSFET의 문턱 전압(VTN)이 변하는 현상을 말한다. 몸체는 또 다른 게이트처럼 동작할 수 있어 "뒷문(back gate)"이라고도 불리며, 몸체 효과는 "뒷문 효과"라고도 부른다.[42]반도체 내 에너지띠의 점유는 페르미 준위에 의해 결정된다. 소스-기판 pn 접합에 역방향 바이어스를 가하면, 전자와 정공에 대한 페르미 준위가 분리되어 채널의 페르미 준위가 띠 가장자리에서 멀어진다. 이는 채널 형성에 필요한 게이트 전압을 증가시킨다. 즉, 역방향 바이어스가 커질수록 문턱 전압이 높아져 채널 형성이 어려워진다.

몸체 효과에 의한 문턱 전압(VTB)의 변화는 다음 수식으로 근사할 수 있다.[41]

:

여기서,

- VT0는 기판 바이어스가 없을 때 (VSB = 0)의 문턱 전압이다.

- γ는 몸체 효과 매개변수이다.

- 2φB는 VSB = 0이고 게이트 바이어스가 채널 형성을 보장할 만큼 충분할 때 공핍층 전체의 표면과 벌크 사이의 근사적인 전위 강하이다.

이 수식에서 볼 수 있듯이, 역방향 바이어스 (VSB > 0)는 문턱 전압 VTB를 증가시켜 채널이 형성되기 전에 더 큰 게이트 전압이 필요하게 된다.[41]

5. 회로 기호

MOSFET은 다양한 기호로 표현된다. 기본적인 형태는 채널을 나타내는 선과, 그 선에 직각으로 연결되어 꺾이는 소스와 드레인을 나타내는 선으로 구성된다. 게이트는 채널과 평행한 또 다른 선으로 표현된다.

강화형 MOSFET은 끊어진 선으로, 공핍형 MOSFET은 실선으로 채널을 나타낸다.

벌크(bulk) 또는 바디(body) 연결은 화살표로 표시되며, 이 화살표는 항상 P에서 N으로 향한다. 따라서 NMOS (P-웰 또는 P-기판의 N채널)의 경우 화살표는 안쪽(벌크에서 채널)을 가리킨다. 벌크가 소스에 연결된 경우(개별 소자의 경우 일반적)에는 트랜지스터를 떠나는 소스와 만나도록 기울어진다. 벌크가 표시되지 않는 경우(집적 회로 설계의 경우처럼)에는 PMOS를 나타내기 위해 반전 기호를 사용하기도 한다.

다음은 강화형 및 고갈형 MOSFET 기호와 JFET 기호를 비교한 표이다.

| P채널 | -- | -- | -- | -- | -- |

|---|---|---|---|---|---|

| N채널 | -- | -- | -- | -- | -- |

| JFET | MOSFET 강화형 | MOSFET 강화형 (벌크 없음) | MOSFET 공핍형 | ||

6. 응용

MOSFET은 디지털 집적 회로(마이크로프로세서, 메모리 장치 등), 전력 전자 장치, 무선 주파수 증폭기, 오디오 주파수 전력 증폭기 등 다양한 분야에 활용된다.

마이크로프로세서와 메모리 장치 같은 디지털 집적 회로는 각 장치에 수천 개에서 수십억 개의 MOSFET 트랜지스터를 집적하여 논리 게이트와 데이터 저장에 필요한 기본적인 스위칭 기능을 제공한다. 개별 소자는 스위칭 모드 전원 공급 장치, 가변 주파수 드라이브 및 각 소자가 수천 와트를 스위칭할 수 있는 기타 전력 전자 장치 응용 분야에서 널리 사용된다. 초고주파 스펙트럼까지의 무선 주파수 증폭기는 MOSFET 트랜지스터를 아날로그 신호 및 전력 증폭기로 사용하며, 무선 시스템에서는 발진기 또는 주파수 변환 믹서로도 활용된다. 또한 MOSFET 소자는 공공 주소 시스템, 음향 증폭, 가정용 및 자동차 사운드 시스템의 오디오 주파수 전력 증폭기에도 적용된다.

바이폴라 트랜지스터가 입력 전류로 제어되는 반면, MOSFET은 입력 전압에 의한 전계로 제어된다. MOSFET의 게이트에는 원리적으로 직류에서[81] 미세한 누설 전류를 제외하고는 전류가 흐르지 않아 저소비전력 특성을 가진다. 또한, 바이폴라 트랜지스터는 정공과 전자, 두 종류의 캐리어로 동작하는 반면, MOSFET은 한 종류의 캐리어로 동작하여 "유니폴라 트랜지스터"라고도 불린다.

MOSFET은 평면적이고 고집적화에 적합한 구조를 가지므로, IC(집적 회로)화에 유리하다. 바이폴라 트랜지스터의 입출력은 "에미터", "베이스", "컬렉터"인 반면, MOSFET은 "소스", "게이트", "드레인"이다.[81]

6. 1. MOS 집적 회로

초고순도 클린룸[46]의 개발과 회로 제작 단계를 크게 줄여준 포토리소그래피[46] 및 플래너 공정[46]의 발전에 따라, Si–SiO2 시스템은 (단위 회로당) 낮은 생산 비용과 용이한 집적이라는 기술적 장점을 가지게 되었다. 이 두 가지 요인 덕분에, MOSFET은 IET에서 가장 널리 사용되는 트랜지스터 유형이 되었다.제너럴 마이크로일렉트로닉스(General Microelectronics)는 1964년 최초의 상용 MOS 집적회로를 선보였다.[47] CMOS 방식은 상보형 MOSFET(P채널 및 N채널) 두 개를 하나의 고/저 스위치로 결합하여, 실제로 스위칭될 때를 제외하고는 디지털 회로의 전력 소모가 매우 적다.

1970년대 초반의 최초의 마이크로프로세서들은 모두 MOS 마이크로프로세서였다. 즉, 전적으로 PMOS 논리 또는 전적으로 NMOS 논리로 제작되었다. 1970년대에는 MOS 마이크로프로세서가 CMOS 마이크로프로세서 및 바이폴라 비트 슬라이스 프로세서와 자주 비교되었다.[48]

6. 2. CMOS 회로

CMOS 논리는 p형 및 n형 MOSFET을 기본 구성 요소로 사용하여 전력 소모를 줄인다. CMOS는 모든 nMOSFET에 pMOSFET을 보완하고 두 게이트와 두 드레인을 함께 연결하여 전류 감소를 달성한다. 게이트에 높은 전압이 인가되면 nMOSFET은 통전되고 pMOSFET은 통전되지 않으며, 게이트에 낮은 전압이 인가되면 그 반대가 된다. 이러한 구성은 전력 소모와 발열을 크게 줄인다.[49]6. 2. 1. 디지털

마이크로프로세서와 같은 디지털 기술의 발전은 MOSFET 기술이 다른 실리콘 기반 트랜지스터보다 빠르게 발전하는 동기가 되었다.[50] MOSFET의 큰 장점은 게이트와 채널 사이의 산화물 층이 게이트를 통해 직류 전류가 흐르는 것을 방지하여 전력 소모를 줄이고 매우 큰 입력 임피던스를 제공한다는 것이다. 게이트와 채널 사이의 절연 산화막은 논리 단계에서 하나의 MOSFET을 이전 및 이후 단계로부터 효과적으로 분리하여 단일 MOSFET 출력이 상당한 수의 MOSFET 입력을 구동할 수 있게 한다. TTL과 같은 바이폴라 트랜지스터 기반 논리는 그러한 높은 팬아웃 용량을 가지고 있지 않다. 이러한 분리는 또한 설계자가 논리 단계 간의 부하 효과를 어느 정도 독립적으로 무시하기 쉽게 만든다. 그 정도는 동작 주파수에 의해 정의된다. 주파수가 증가함에 따라 MOSFET의 입력 임피던스는 감소한다.6. 2. 2. 아날로그

접합형 트랜지스터는 높은 트랜스컨덕턴스와 독특한 특징들 때문에 아날로그 설계에서 선호되었지만, MOSFET도 널리 사용된다. 아날로그 회로의 특징과 성능은 MOSFET의 크기(길이와 넓이)를 조절하여 설계할 수 있다. MOSFET는 양의 온도계수를 가지므로 열폭주 문제가 적다. 선형 영역에서는 정밀 저항처럼 사용하는 것이 가능하며, 축전기를 형성할 수 있고, 특별한 회로에서는 인덕터처럼 보이게 할 수도 있어서, 다이오드를 제외한 모든 일반 아날로그 소자를 MOSFET으로 구현할 수 있다. 이는 더 좁은 공간에 완전한 아날로그 회로를 만들 수 있게 한다.일부 IC는 아날로그와 디지털 MOSFET 회로를 결합하여 기판 공간을 줄인다. 이를 위해 절연 링과 절연체 위 실리콘(SOI)을 사용하여 칩 단계에서 아날로그 회로와 디지털 회로를 격리한다. MOSFET는 BJT보다 주어진 양의 전력을 처리하는 데 더 많은 공간이 필요하므로, 제조 공정에서 BJT와 MOSFET을 단일 장치에 통합하기도 한다. 혼성 트랜지스터 장치는 BJT-FET 하나만 포함하면 바이-FET(바이폴라 FET), 상보적인 BJT-FET를 포함하면 바이CMOS(바이폴라-CMOS)라고 부르며, 절연 게이트와 더 높은 전류 밀도의 장점을 모두 가진다.[1]

6. 3. 아날로그 스위치

MOSFET 아날로그 스위치는 온(on) 상태에서 낮은 저항으로 아날로그 신호를 통과시키고, 오프(off) 상태에서는 높은 임피던스로 신호를 차단한다. 신호는 MOSFET 스위치를 통해 양방향으로 흐른다. MOSFET의 드레인과 소스는 게이트와 비교한 각 전극의 전압에 따라 위치를 서로 바꾼다. 소스는 N형 MOSFET에서는 더 낮은 전압 쪽에, P형 MOSFET에서는 더 높은 전압 쪽에 위치한다. 이러한 스위치는 게이트-소스, 게이트-드레인, 소스-드레인 전압에 의해 통과/차단 여부가 결정되며, 제한 전압을 초과하면 스위치가 손상될 수 있다.[1]6. 3. 1. 단독형 MOSFET 스위치

아날로그 스위치는 N형이나 P형의 4단자 단순 MOSFET을 사용한다.N형 스위치의 경우, 바디(body)는 가장 낮은 전원(일반적으로 그라운드)에 연결되고 게이트는 스위치 제어로 사용된다. 게이트 전압이 소스 전압보다 임계 전압 이상으로 높아지면 MOSFET은 전도된다. 더 높은 전압은 MOSFET이 더욱 전도되게 한다. N-MOS는 ''V''gate − ''V''tn보다 낮은 모든 전압을 통과시킬 것이다. 스위치가 전도되면 소스와 드레인 전압은 일반적으로 거의 비슷하기 때문에 일반적으로 선형 영역으로 동작한다.

P-MOS의 경우에 바디는 가장 높은 전압에 연결되고 게이트는 낮은 전압이 스위치를 열게 한다. P-MOS 스위치는 ''V''gate − ''V''tp보다 높은 모든 전압을 통과시킨다. (강화형 P-MOS의 경우 임계 전압 ''V''tp는 음수임).

P-MOS 스위치는 동일한 면적의 N-MOS 소자 저항의 약 3배 정도이다. 왜냐하면 전자는 실리콘에서 양공보다 3배 정도의 이동도를 갖기 때문이다.[1]

6. 3. 2. 이중형 (CMOS) MOSFET 스위치

시모스형 스위치는 P-MOSFET과 N-MOSFET을 결합하여 단독형 스위치의 제한을 보완한다. 두 트랜지스터는 드레인과 소스가 병렬로 연결되고, P-MOSFET의 보디는 고전압(VDD), N-MOSFET의 보디는 저전압(GND)에 연결된다. P-MOSFET의 게이트에 저전압을, N-MOSFET의 게이트에 고전압을 인가하면 스위치가 켜진다. (VDD-Vtn)과 (Gnd+Vtp) 사이 전압에서는 두 트랜지스터 모두 신호를 전도하고, (Gnd+Vtp)보다 낮은 전압에서는 N-MOSFET만, (VDD-Vtn)보다 높은 전압에서는 P-MOSFET만 양공을 전도한다.이 스위치의 유일한 제한은 모든 장효과 트랜지스터의 게이트-소스, 게이트-드레인, 소스-드레인 전압 제한이다. P-MOSFET은 일반적으로 N-MOSFET보다 3배 정도 폭이 커서 스위치는 안정적이다.

삼상 논리 회로는 때때로 시모스 MOSFET 스위치를 출력에 통합하여 켜져 있을 때 저저항, 전범위 출력을 제공하고, 꺼져 있을 때 고저항, 중간 레벨 신호를 제공한다.

7. MOSFET 구성

MOSFET의 반도체로는 주로 실리콘이 사용된다. IBM, 인텔 등 일부 칩 제조업체는 MOSFET 채널에 실리콘과 저마늄의 합금(SiGe)을 사용하기도 한다. 갈륨 비소처럼 실리콘보다 전기적 특성이 우수한 반도체도 있지만, 양호한 반도체-절연체 계면을 형성하기 어려워 MOSFET에는 부적합하다. 따라서 다른 반도체 재료에 대해 허용 가능한 전기적 특성을 갖는 절연체를 개발하기 위한 연구가 계속되고 있다.

게이트 누설 전류로 인한 전력 소비 증가를 막기 위해 게이트 절연체로 이산화규소 대신 고유전율 유전체를 사용하고, 폴리실리콘 대신 금속 게이트(예: 인텔, 2009)를 사용하기도 한다.[21]

게이트는 얇은 절연층을 통해 채널과 분리된다. 이 절연층은 전통적으로 이산화규소를 사용했지만, 이후에는 산화질화규소를 사용하기도 한다. 최근에는 45나노미터 노드에서 고유전율 유전체와 금속 게이트 조합을 사용하는 경우도 있다.

게이트와 소스 사이에 전압을 가하면 전기장이 발생하여 산화물을 지나 반도체-절연체 계면에 '반전층' 또는 '채널'이 형성된다. 이 반전층은 소스와 드레인 단자 사이의 전류 통로 역할을 한다. 게이트와 바디 사이의 전압을 조절하면 이 층의 전도도가 변화하여 드레인과 소스 사이의 전류 흐름을 제어할 수 있는데, 이를 인핸스먼트 모드라고 한다.

7. 1. 게이트 재료

폴리실리콘은 수용 가능하지만 이상적인 전도체는 아니며, 몇 가지 기술적 결함이 있다. 이러한 단점을 해결하기 위해 금속 게이트나 규화물(실리사이드) 등의 재료가 사용되기도 한다.폴리실리콘 게이트의 단점은 다음과 같다.

- 폴리실리콘은 좋은 전도체가 아니어서(대략 금속보다 1000배 더 큰 저항) 신호의 전파 속도를 감소시킨다. 저항값은 도핑을 통해 낮출 수 있지만, 도핑된 폴리실리콘도 대부분의 금속만큼 전도되지 않는다. 전도력을 향상시키기 위해 텅스텐, 티타늄, 코발트, 니켈 같은 고온금속을 폴리실리콘 상위막과 합금하여 규화물을 만들기도 한다. 규화 폴리실리콘 조합은 전기적 특성이 좋고 고온 공정에서도 녹지 않는다. 또한 문턱 전압도 크게 높지 않다.

- 트랜지스터가 극도로 작아지면 게이트 전극막을 매우 얇게(1 nm 근처) 만들어야 한다. 이때 폴리 공핍 현상이 발생하는데, 이는 트랜지스터가 반전되었을 때 게이트 유전층 옆의 게이트 폴리실리콘에서 공핍막이 형성되는 현상이다. 이 문제를 해결하기 위해 금속 게이트가 필요하다. 탄탈, 텅스텐, 질화 탄탈, 질화 텅스텐 같은 금속 게이트는 일반적으로 높은 k 유전체와 결합되어 사용된다. 다른 대안으로는 완전 규화 폴리실리콘 게이트를 사용하는 FUSI 공정이 있다.

7. 2. 절연체

MOSFET에서 게이트와 채널 사이의 절연체는 유전체이며, LOCOS 공정으로 형성된 실리콘 산화물이 주로 사용되지만, 다른 여러 유전체 재료도 사용된다. 이 유전체를 일반적으로 게이트 유전체라고 부르는데, 이는 유전체가 게이트 전극 바로 아래, MOSFET의 채널 위에 위치하기 때문이다.소자가 소형화되면서 절연층도 얇아지고 있다. 이는 열 산화나 LOCOS 공정을 통해 이루어진다. 나노 스케일 소자에서는 채널에서 게이트 전극으로 캐리어가 터널링하는 현상이 발생한다. 이로 인해 발생하는 누설 전류를 줄이기 위해, 더 높은 유전율을 가진 재료를 사용하여 절연체의 두께를 늘릴 수 있다. 두께와 유전율의 관계는 다음과 같다.

:

여기서 ''Q''는 전하 밀도, κ는 유전율, ε0는 진공의 유전율, ''E''는 전기장이다. 이 식에서 κ(유전율)가 증가하면 더 낮은 전계에서도 채널에 동일한 전하를 유지할 수 있다. 게이트 전압은 다음과 같이 표현된다.

:

여기서 ''V''G는 게이트 전압, ''V''ch는 절연체의 채널 측 전압, ''t''ins는 절연체 두께이다. 이 식에서 ''t''ins / κ 값이 일정하게 유지되면, κ(유전율)가 증가하여 절연체 두께(''t''ins)가 증가해도 게이트 전압(''V''G)은 증가하지 않는다. (고유전율 유전체 및 게이트 산화막 누설 섹션 참조).

8. MOSFET 축소

지난 수십 년간 MOSFET의 크기는 지속적으로 감소되어 왔다. 과거에는 MOSFET 채널 길이가 몇 마이크로미터 수준이었지만, 현대 집적 회로에는 0.1 마이크로미터보다 작은 채널 길이를 가진 MOSFET이 사용되고 있다. 인텔은 2006년에 65nm 최소 배선폭(채널은 더 짧음)을 갖는 공정 생산을 시작했고, 2009년 말에는 32nm 특징 크기(채널은 더 짧음)를 갖는 공정 생산을 시작했다. 이러한 지속적인 축소는 로버트 데나드의 스케일링 이론 연구를 통해 가능해졌다. 반도체 산업은 MOSFET 개발의 속도를 설정하는 "로드맵"인 ITRS[54]를 유지하고 있다.

MOSFET 크기 축소의 어려움은 반도체 소자 제조 공정과 관련이 깊다. 특히 소스-바디 접합 및 드레인-바디 접합 설계는 소자의 전류-전압(''I-V'') 특성, 속도, 대기 전력 소모에 큰 영향을 미친다.

얕은 접합 확장은 임계 전압의 드레인 유도 장벽 저하 및 ''I-V'' 곡선에 대한 채널 길이 변조 효과를 감소시킨다. 또한, ''헬로'' 도핑, 즉 접합 벽에 바짝 붙어 바디와 같은 도핑 유형의 매우 얇고 고농도로 도핑된 영역을 추가하여 공핍 영역의 범위를 제한할 수 있다.[52] 상승된 소스 및 드레인 형상은 접촉 영역의 대부분이 실리콘 대신 두꺼운 유전체 경계를 형성하여 정전 용량 효과를 제한할 수 있다.[53]

마이크로미터보다 훨씬 작은 채널 길이를 가진 MOSFET을 생산하는 것은 어려운 과제이며, ALD과 같은 공정 개선에도 불구하고, MOSFET의 작은 크기(수십 나노미터 미만)는 작동상의 문제를 야기한다. 더 작은 MOSFET은 더 높은 누설 전류와 더 낮은 출력 저항을 나타내기 때문에 회로 재설계 및 혁신이 필요하다.

8. 1. MOSFET 축소의 이유

소형 모스펫(MOSFET)은 몇 가지 이유로 선호된다. 첫째, 소형 모스펫은 넓이 치수가 짧아져 더 많은 전류가 통과할 수 있다. 개념상 모스펫은 온(on) 상태의 저항기와 같고, 짧아진 저항기는 더 적은 저항값을 지닌다. 둘째, 소형 모스펫은 게이트 영역이 작아져 게이트 전기용량이 작아진다. 이 두 가지 요소는 짧은 스위칭 시간에 기여하여 빠른 처리 속도와 스위칭당 저전력 특성을 갖는다.[54] 셋째, 면적 감소는 비용 절감으로 이어진다. 소형 모스펫은 고밀도 집적을 가능하게 하여, 더 작은 칩이나 동일한 크기에서 더 뛰어난 계산 능력을 가진 칩을 만들 수 있게 한다. 반도체 웨이퍼 제조 비용은 상대적으로 고정되어 있기 때문에, 집적 회로당 비용은 웨이퍼당 생산할 수 있는 칩의 수와 주로 관련된다. 따라서 소형 집적 회로는 웨이퍼당 더 많은 칩을 생산할 수 있어 칩 단가를 낮출 수 있다.[55]8. 2. MOSFET 축소 때문에 발생하는 어려움

MOSFET의 크기가 마이크로미터보다 훨씬 작아지면서 여러 가지 문제점들이 발생하고 있다. 반도체 소자 제조의 어려움은 집적 회로 기술 발전의 제한 요소였으며, 원자층 증착(ALD)과 같은 공정 개선에도 불구하고 MOSFET의 소형화는 작동상의 문제를 야기한다.MOSFET 축소에 따라 발생하는 주요 어려움은 다음과 같다:

- 문턱 전압 감소 및 문턱아래 전도: MOSFET 소형화에 따라 성능 향상을 위해 문턱 전압을 낮춰야 하는데, 이는 트랜지스터를 완전히 끄는 것을 어렵게 만들어 소스와 드레인 사이에 문턱아래 누설 전류를 발생시킨다.

- 상호연결 전기용량 증가: 트랜지스터가 작아지고 칩에 더 많은 트랜지스터가 집적됨에 따라 상호연결 전기용량이 증가하여 신호 지연과 성능 저하를 유발한다.

- 열 발생: 집적 회로 내 MOSFET 밀도가 증가하면서 발열 문제가 심각해져 회로 동작을 손상시키고 신뢰성을 저하시킨다.

- 게이트 산화막 누설: 게이트 산화막이 얇아짐에 따라 양자역학적 전자 터널링 현상이 발생하여 전력 소모가 증가한다. 이산화규소 대신 유전 상수가 높은 물질을 사용하기도 하지만, 이 경우에도 다른 문제점이 발생할 수 있다.

- 공정 변이: MOSFET 소형화에 따라 공정 변이가 트랜지스터 특성에 미치는 영향이 커져 트랜지스터의 동작을 예측하기 어려워진다.

이 외에도 드레인 유기 장벽 저하(DIBL), Vt 롤오프(VT roll-off) 등의 단채널 효과(short-channel effect)와 캐리어 이동도 감소 등의 문제가 발생한다. 아날로그 회로에서는 높은 이득을 얻기 위해 MOSFET 출력 임피던스가 높아야 하는데, 소자 크기가 작아지면서 출력 저항이 감소하여 회로 설계가 복잡해진다.

8. 2. 1. 문턱아래 전도

MOSFET의 소형화에 따라 성능 향상을 위해 문턱 전압도 낮춰야 한다. 문턱 전압 감소는 트랜지스터의 완전한 차단을 어렵게 하여, 소스와 드레인 사이에 문턱아래 누설 또는 문턱아래 전도를 유발한다. 과거에는 무시되던 문턱아래 전도가 현재 고성능 VLSI 칩 총 소비전력의 절반 이상을 차지할 수 있다.[56][57]저전력 아날로그 회로는 문턱아래 전도를 활용하기도 한다. 미약한 역 영역에서 동작하는 MOSFET은 가능한 가장 높은 트랜스컨덕턴스-전류 비율을 제공하기 때문이다.

8. 2. 2. 상호연결 전기용량

트랜지스터가 작아지고 더 많은 트랜지스터가 칩 위에 배치되면서, 상호연결 전기용량(칩의 다른 부분을 연결하는 전선의 커패시턴스)이 전체 전기용량에서 큰 비중을 차지하게 되었다. 신호는 상호연결을 통해 전송되기 때문에 상호연결 전기용량은 지연 증가와 성능 감소를 발생시킨다.[61][62]8. 2. 3. 열 발생

집적 회로 위에 MOSFET의 밀도가 증가함에 따라 발열 문제가 심각해져 회로 동작을 손상시킬 수 있다.[54] 회로는 고온에서 느리게 동작하여 신뢰성을 떨어뜨리고 수명을 단축한다. 따라서 방열판과 다른 냉각 방법이 필요하다.[55]전력 MOSFET은 열폭주의 위험이 있다. 온상태 저항이 온도에 따라 증가함에 따라 전력 손실이 증가하고 더 많은 열을 발생시킨다. 방열판이 온도를 충분히 낮게 유지할 수 없으면 접합부 온도가 빠르게 상승하여 소자가 파괴될 수 있다.[56]

8. 2. 4. 게이트 산화물 누설

게이트 산화막은 게이트와 채널 사이의 절연체 역할을 하는데, 트랜지스터가 켜졌을 때 채널 전도도와 성능을 높이고, 꺼졌을 때 서브스레숄드 누설 전류를 줄이기 위해 가능한 한 얇게 만들어야 한다. 그러나 현재 약 1.2 nm(실리콘의 경우 약 5개의 원자 두께) 두께의 게이트 산화막에서는 양자역학적 현상인 전자 터널링이 발생하여 전력 소모가 증가한다.[56][57]이산화규소가 전통적인 게이트 절연체로 사용되어 왔지만, 유전체 상수가 더 큰 절연체( 고유전율 유전체)를 사용하면 높은 정전용량을 유지하면서 더 두꺼운 층을 사용할 수 있어 게이트와 채널 사이의 양자 터널링 전류를 감소시킬 수 있다. 예를 들어 하프늄 및 지르코늄 규산염과 산화물과 같은 4족 금속 규산염이 45나노미터 기술 노드부터 게이트 누설을 줄이기 위해 사용되고 있다. 하지만, 새로운 게이트 절연체의 장벽 높이는 누설 전류 수준에 영향을 미치기 때문에 중요한 고려 사항이다. 기존 게이트 산화막인 이산화규소의 경우 전자의 장벽은 약 8 eV인데, 많은 대체 유전체의 경우 이 값이 훨씬 낮아 터널링 전류가 증가하는 경향이 있다.[56][57]

8. 2. 5. 공정 변이

MOSFET이 소형화되면서 트랜지스터 특성을 결정하는 실리콘 원자 수가 줄어들고 있다. 칩 제조 과정에서 발생하는 무작위적인 공정 변이는 트랜지스터의 크기(길이, 폭, 접합 깊이, 산화막 두께 등)에 영향을 미치는데, 트랜지스터가 작아질수록 이러한 변이가 트랜지스터 전체 크기에서 차지하는 비율이 커진다. 따라서 트랜지스터의 특성은 덜 결정론적(deterministic)이 되고 더 통계적(statistical)으로 변하며, 이는 설계에 어려움을 더한다.[63] 제조 과정의 무작위성 때문에 특정 회로에 어떤 MOSFET이 사용될지 정확히 예측하기 어렵고, 다양한 특성의 MOSFET에 대해 회로가 작동하도록 설계해야 하므로 최적의 설계가 어려워진다.9. 다른 MOSFET 종류

집적 회로 상의 MOSFET 밀도가 높아짐에 따라 발생하는 국부적인 발열은 회로 작동 속도 저하, 신뢰성 저하, 수명 단축 등의 문제를 야기한다. 따라서 마이크로프로세서를 비롯한 많은 집적 회로에는 방열판 및 기타 냉각 장치가 필요하다. 전력 MOSFET은 열 폭주 현상으로 인해 소자가 파괴될 위험이 있다. 온저항이 온도에 따라 증가하면서 전력 손실이 커지고, 이는 더 많은 열을 발생시켜 접합 온도가 급상승하기 때문이다.

- '''이중 게이트 MOSFET'''

이중 게이트 MOSFET은 사극관처럼 두 개의 게이트로 소자의 전류를 제어한다. 주로 라디오 주파수 응용 분야에서 소신호 소자에 사용되며, 두 번째 게이트는 증폭값 제어, 혼합, 주파수 변환 등에 활용된다.[64][65] FinFET는 이중 게이트 실리콘 온 인슐레이터 소자의 일종으로, 짧은 채널 효과를 완화하고 드레인 유도 배리어 저하를 줄이기 위해 도입되었다.

- '''공핍형 MOSFET'''

공핍형 MOSFET은 게이트에 전압을 인가하지 않아도 채널이 존재하여 전류가 흐르는 소자이다. 게이트에 음의 전압을 가하면 공핍 채널이 감소하여 전류가 줄어든다. TV 수상기와 같은 RF 프런트 엔드에서 바이폴라 트랜지스터보다 잡음 지수가 낮고 이득이 우수하여 선호되는 경우가 많다.[66]

- '''엔모스 논리'''

엔모스 논리는 N채널 MOSFET만으로 구성된 논리 회로이다. P채널 MOSFET보다 크기가 작고, 생산 비용이 저렴하며 기술적으로 간단하다는 장점이 있다. 그러나 CMOS 논리와 달리 스위칭이 없을 때도 전력을 소비하는 단점이 있어, 1980년대 중반 이후 CMOS 논리에 대체되었다.[1]

- '''전력 MOSFET'''

전력 MOSFET은 수직 구조를 가지며, 높은 전압과 전류를 견딜 수 있다.[92] 전압 등급은 도핑과 N에픽택시막 두께에, 전류 등급은 채널 폭에 의해 결정된다. 수직 구조는 소자 면적을 효율적으로 사용할 수 있게 해준다. 측면 구조의 전력 MOSFET은 주로 오디오 증폭기와 고출력 PA 시스템에 사용되며, 포화 영역에서 더 나은 특성을 보인다.[73] 전력 MOSFET은 바이폴라 파워 트랜지스터에 비해 구동 회로의 전력 손실이 적고, 고속 스위칭이 가능하여 스위칭 손실이 작다는 장점이 있다. 그러나 내압이 높아짐에 따라 온 저항이 증가하는 문제가 있다. 최근에는 트렌치 게이트, 초접합 구조 등의 기술을 통해 이러한 문제점을 개선한 제품들이 개발되고 있다.[71][72]

- '''디모스 (DMOS)'''

디모스(DMOS)는 이중 확산 금속 산화막 반도체(double-Diffused Metal Oxide Semiconductor영어)의 약자로, 대부분의 전력 MOSFET 제조에 사용되는 기술이다.[92]

9. 1. 이중 게이트 MOSFET

이중 게이트 MOSFET은 사극관 환경을 지녀서 소자에서 전류를 양쪽 게이트로 제어한다. 라디오 주파수 응용에서 소신호 소자에 일반적으로 사용돼서 두 번째 게이트는 일반적으로 증폭값 제어나 혼합과 주파수 변환에 사용된다.[64][65]이중 게이트 MOSFET는 두 개의 게이트가 소자의 전류를 제어하는 사극관 구성을 가지고 있다. 이는 드레인 측 게이트를 일정 전위로 바이어싱하여 밀러 효과로 인한 이득 손실을 줄이는 무선 주파수 응용 분야의 소신호 소자에 일반적으로 사용되며, 캐스코드 구성의 두 개의 개별 트랜지스터를 대체한다. RF 회로에서의 다른 일반적인 용도에는 이득 제어 및 믹싱(주파수 변환)이 포함된다.

FinFET는 여러 가지 형상 중 하나인 이중 게이트 실리콘 온 인슐레이터 소자로, 짧은 채널의 영향을 완화하고 드레인 유도 배리어 저하를 줄이기 위해 도입되었다. "fin"은 소스와 드레인 사이의 좁은 채널을 나타낸다. 핀의 양쪽에 있는 얇은 절연 산화물 층이 핀을 게이트와 분리한다. 핀 상단에 두꺼운 산화물을 가진 SOI FinFET는 "이중 게이트"라고 하고, 상단과 측면에 얇은 산화물을 가진 것은 "삼중 게이트" FinFET라고 한다.

9. 2. 공핍형 MOSFET

공핍형 MOSFET은 게이트에 전압을 인가하지 않아도 채널이 존재하는 MOSFET 소자이다. 채널을 제어하기 위해 게이트에 음의 전압을 가하면 공핍 채널이 감소하여 소자를 통과하는 전류가 줄어든다. 공핍형 소자는 일반적으로 닫힌 스위치와 같고, 확장형 소자는 일반적으로 열린 스위치와 같다.[66]잡음 지수가 낮고 RF 영역에서 이득이 더 우수하여, TV 수상기와 같은 RF 프런트 엔드에서 바이폴라 트랜지스터보다 선호되는 경우가 많다.

공핍형 MOSFET 제품군에는 지멘스와 텔레푼켄의 BF960, 1980년대 필립스(후에 NXP 반도체가 됨)의 BF980이 있으며, 이들의 파생 제품은 현재까지도 AGC 및 RF 믹서 프런트 엔드에 사용되고 있다.

9. 3. 엔모스 논리

엔모스 논리는 N채널 MOSFET만을 사용하여 구성된 논리 회로이다. N채널 MOSFET은 P채널 MOSFET보다 크기가 작고, 실리콘 기판에서 한 종류의 MOSFET만 생산하면 되므로 더 저렴하고 기술적으로 간단하다는 장점이 있다.[1] 그러나 CMOS 논리와 달리 NMOS 논리는 스위칭이 일어나지 않을 때에도 전력을 소비하는 단점이 있다.[1] 이러한 단점에도 불구하고, 1980년대 중반 CMOS 논리가 NMOS 논리를 대체하기 전까지 디지털 칩에 널리 사용되었다.[1]9. 4. 전력 MOSFET

전력 MOSFET은 수직 구조를 가지고 있다.[92] 수직구조를 사용한 전력 MOSFET은 차단 시 고전압과 고전류를 유지할 수 있다. 트랜지스터의 전압등급은 도핑과 N에픽택시막 두께의 기능이고 전류등급은 채널폭의 기능이다. (넓은 채널은 고전류) 평판 구조에서 전류와 항복전압 등급은 채널면적(채널의 폭과 길이)의 기능으로 "실리콘 재산"의 비효율적 사용을 초래한다. 수직구조에서 소자면적은 유지할 수 있는 전류에 대충 비례하고 소자두께 (실제로는 N에픽택시막 두께)는 항복전압에 비례한다.[71][72]측면 구조가 존재하는 전력 모스펫은 최상급 오디오 증폭기와 고출력 PA 시스템에 주로 사용된다. 장점은 포화영역 (접합형 트랜지스터의 선형영역과 일치됨)에서 수직형 모스펫보다 좋은 특성이다. 수직형 모스펫은 스위칭 응용에 설계되어서 통과와 차단상태에만 사용된다.[73]

전력 MOSFET은 특히 대전력 스위칭용으로 설계된 MOSFET이다. 바이폴라 파워 트랜지스터에 비해 전압 구동형 소자이므로 구동 회로의 전력 손실이 작다. 또한 다수 캐리어 디바이스이며, 본질적으로 고속 스위칭이 가능하여 스위칭 손실이 작다. 그러나 내압이 높아짐에 따라 온 저항이 높아지는 문제가 있다.

2000년대에 들어 트렌치 게이트, 의사 평면 접합 등의 구조적인 개선을 통해 고내전압화, 온 저항 및 스위칭 손실 감소를 모두 만족하는 것도 개발되었다. 더 나아가, 2006년 현재 초접합 구조를 사용하여 실리콘의 이론적 한계를 뛰어넘는 저손실 제품도 개발되고 있다.

9. 5. 디모스 (DMOS)

디모스(DMOS)는 이중 확산 금속 산화막 반도체(double-Diffused Metal Oxide Semiconductor영어)의 줄임말이다. 대부분의 전력 MOSFET은 이 기술을 이용하여 만든다.[92]참조

[1]

웹사이트

D-MOSFET OPERATION AND BIASING

https://massless.inf[...]

[2]

특허

Method and apparatus for controlling electric currents

1926-10-08

[3]

특허

Improvements in or relating to electrical amplifiers and other control arrangements and devices

http://v3.espacenet.[...]

1935-12-06

[4]

학술지

Frosch and Derick: Fifty Years Later (Foreword)

https://iopscience.i[...]

2007-09-01

[5]

특허

Oxidation of semiconductive surfaces for controlled diffusion

https://patents.goog[...]

1957-08-13

[6]

학술지

Surface Protection and Selective Masking during Diffusion in Silicon

https://iopscience.i[...]

1957

[7]

학술지

Surface Protection and Selective Masking during Diffusion in Silicon

https://iopscience.i[...]

1957

[8]

서적

Advanced Materials Innovation: Managing Global Technology in the 21st century

https://books.google[...]

John Wiley & Sons

2016

[9]

서적

Makers of the Microchip: A Documentary History of Fairchild Semiconductor

https://books.google[...]

MIT Press

2010

[10]

서적

ULSI Process Integration III: Proceedings of the International Symposium

https://books.google[...]

The Electrochemical Society

2003

[11]

서적

History of Semiconductor Engineering

Springer Science & Business Media

2007

[12]

학술지

The mechanisms for silicon oxidation in steam and oxygen

https://linkinghub.e[...]

1960-07-01

[13]

서적

Silicon materials science and technology

The Electrochemical Society

1998

[14]

서적

History of Semiconductor Engineering

Springer Science & Business Media

2007

[15]

서적

To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology

https://books.google[...]

Johns Hopkins University Press

2007

[16]

학술지

Silicon-silicon dioxide field induced surface devices

1960

[17]

웹사이트

1960 – Metal Oxide Semiconductor (MOS) Transistor Demonstrated

https://www.computer[...]

Computer History Museum

2023-01-16

[18]

학술지

Silicon-Silicon Dioxide Surface Device

https://doi.org/10.1[...]

1961

[19]

서적

History of Semiconductor Engineering

Springer-Verlag Berlin Heidelberg

2007

[20]

서적

To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology

JHU Press

[21]

웹사이트

Intel 45nm Hi-k Silicon Technology

http://www.intel.com[...]

Intel

[22]

웹사이트

memory components data book

http://bitsavers.tra[...]

Intel

2015-08-30

[23]

웹사이트

Using a MOSFET as a Switch

http://brunningsoftw[...]

[24]

논문

Modeling and simulation of insulated-gate field-effect transistor switching circuits

https://ieeexplore.i[...]

[25]

서적

MOSFET modeling & BSIM3 user's guide

https://books.google[...]

Springer

[25]

웹사이트

BSIM-CMG 106.1.0beta Multi-Gate MOSFET Compact Model

http://www-device.ee[...]

Department of Electronic Engineering and Computer Science, University of California Berkeley

2012-04-01

[26]

서적

Analysis and Design of Analog Integrated Circuits

http://worldcat.org/[...]

Wiley

[27]

서적

Low-Power Deep Sub-Micron CMOS Logic: Subthreshold Current Reduction

https://books.google[...]

Springer

[28]

웹사이트

Wikipedia fails subvt

https://sites.google[...]

[29]

서적

Analog VLSI and Neural Systems

Addison-Wesley

[30]

서적

Neuromorphic Systems: Engineering Silicon from Neurobiology

https://books.google[...]

World Scientific

1998

[31]

서적

Neural Networks: A Classroom Approach

https://books.google[...]

Tata McGraw-Hill

2004

[32]

서적

Field-programmable Logic and Applications: 12th International Conference

https://books.google[...]

Springer

2002

[33]

서적

Circuits and systems tutorials

John Wiley and Sons

1996

[34]

서적

Nano, Quantum and Molecular Computing

https://books.google[...]

Springer

[35]

서적

Statistical Analysis and Optimization For VLSI: Timing and Power

https://books.google[...]

Springer

[36]

서적

MOSFET modeling for circuit analysis and design

http://worldcat.org/[...]

World Scientific

[37]

서적

Electronic circuits: analysis, simulation, and design

http://worldcat.org/[...]

Prentice Hall

[38]

서적

Microelectronic Circuits

http://worldcat.org/[...]

Oxford University Press

[39]

서적

Analysis and design of analog integrated circuits

http://worldcat.org/[...]

Wiley

[40]

서적

Microelectronic circuits

http://worldcat.org/[...]

Oxford University Press

2004

[41]

서적

Mosfet modeling for VLSI simulation: theory and practice

World Scientific

[42]

웹사이트

Body effect

http://equars.com/~m[...]

Equars.com

2012-06-02

[43]

웹사이트

Electronic Circuit Symbols

http://www.circuitst[...]

2011-11-09

[44]

간행물

IEEE Std 315-1975 — Graphic Symbols for Electrical and Electronics Diagrams (Including Reference Designation Letters)

[45]

서적

Microelectronic Circuit Design

http://highered.mcgr[...]

[46]

웹사이트

1955 – Photolithography Techniques Are Used to Make Silicon Devices

http://www.computerh[...]

Computer History Museum

2012-06-02

[47]

웹사이트

1964 – First Commercial MOS IC Introduced

http://www.computerh[...]

[48]

웹사이트

2-1/2-generation μP's-$10 parts that perform like low-end mini's

http://www.swtpc.com[...]

EDN

1975-09-20

[49]

웹사이트

Computer History Museum – The Silicon Engine | 1963 – Complementary MOS Circuit Configuration is Invented

http://www.computerh[...]

Computerhistory.org

2012-06-02

[50]

웹사이트

Computer History Museum – Exhibits – Microprocessors

http://www.computerh[...]

Computerhistory.org

2012-06-02

[51]

웹사이트

ReVera's FinFET Control

http://www.revera.co[...]

[52]

서적

Physics of Semiconductor Devices

https://books.google[...]

Springer

[53]

서적

Predictive Simulation of Semiconductor Processing: Status and Challenges

https://books.google[...]

Springer

[54]

웹사이트

International Technology Roadmap for Semiconductors

https://web.archive.[...]

[55]

웹사이트

1965 – "Moore's Law" Predicts the Future of Integrated Circuits

http://www.computerh[...]

[56]

서적

Low Voltage, Low Power VLSI Subsystems

https://books.google[...]

McGraw-Hill Professional

[57]

서적

Computational Electronics

https://books.google[...]

Morgan & Claypool

[58]

웹사이트

Frontier Semiconductor Paper

http://frontiersemi.[...]

[59]

서적

The VLSI Handbook

https://books.google[...]

CRC Press

[60]

학술지

A Comparison of Spike, Flash, SPER and Laser Annealing for 45nm CMOS

[61]

논문

VLSI wiring capacitance

http://www.research.[...]

IBM Journal of Research and Development

2021-02-09

[62]

서적

Integrated Circuit Design: Power and Timing Modeling, Optimization, and Simulation (10th Int. Workshop)

https://books.google[...]

Springer

[63]

서적

Design for Manufacturability And Statistical Design: A Constructive Approach

https://www.amazon.c[...]

Springer

2007

[64]

서적

Frontiers in electronics: future chips : proceedings of the 2002 Workshop on Frontiers in Electronics (WOFE-02), St Croix, Virgin Islands, USA, 6–11 January 2002

World Scientific

[65]

서적

Silicon-on-Insulator Technology and Devices

The Electrochemical Society

[66]

백과사전

Depletion Mode

https://web.archive.[...]

2010-01-29

[67]

웹사이트

MIS

https://web.archive.[...]

[68]

서적

Semiconducting polymers: chemistry, physics and engineering

https://books.google[...]

Wiley-VCH

[69]

서적

Organic Molecular Solids: Properties and Applications

https://books.google[...]

CRC Press

[70]

논문

High performance organic field-effect transistors using cyanoethyl pullulan (CEP) high-k polymer cross-linked with trimethylolpropane triglycidyl ether (TTE) at low temperatures

https://pubs.rsc.org[...]

[71]

서적

Power Semiconductor Devices

PWS publishing Company

[72]

웹사이트

Power MOSFET Basics: Understanding MOSFET Characteristics Associated With The Figure of Merit

http://www.element-1[...]

2010-11-27

[73]

웹사이트

Power MOSFET Basics: Understanding Gate Charge and Using It To Assess Switching Performance

http://www.element-1[...]

2010-11-27

[74]

약어

insulated-gate FET

[75]

약어

metal-insulator-semiconductor FET

[76]

웹사이트

微細MOSFETとパワーMOSFETの違い

https://engineer-edu[...]

[77]

웹사이트

パワーMOSFETを使った設計 よくある問題や故障モードの回避方法

https://www.infineon[...]

[78]

기타

[79]

학술지

アーリー電圧の導出について

https://doi.org/10.5[...]

国立高等専門学校機構群馬工業高等専門学校

[80]

웹사이트

MOSFETのボディーダイオードとは

https://www.macnica.[...]

[81]

text

[82]

text

[83]

특허

미국특허 1,900,018

1933-03-07

[84]

text

[85]

text

[86]

발표

IRE 고체 상태 소자 개발 및 발표

1960

[87]

논문

IEEE의 회보

1963-09

[88]

수상

노벨 물리학상

1956

[89]

특허

미국 특허 3,472,712

1966-08-14

[90]

발표

소스-드레인 마스크처럼 게이트를 이용하여 제작된 저항층 게이트 전계효과 트랜지스터 (IGFET)

1966

[91]

논문

실리콘 게이트 기술

1970-08

[92]

서적

전력 반도체 소자

PWS 출판사

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com