이중 직렬 패키지

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

이중 직렬 패키지(DIP)는 집적 회로(IC)를 위한 전자 부품 패키징 방식 중 하나이다. DIP는 핀이 두 줄로 배열된 형태이며, 플라스틱(PDIP), 세라믹(CERDIP), 축소형(SPDIP), 스키니(SDIP) 등 다양한 종류가 있다. DIP는 브레드보드에서의 사용이 용이하여 프로토타입 제작에 널리 사용되었으나, 표면 실장 기술(SMT)의 발달로 사용 빈도가 감소했다. DIP는 스루홀 납땜 또는 소켓을 통해 장착되며, 핀 번호는 패키지의 식별 노치를 기준으로 시계 반대 방향으로 매겨진다.

더 읽어볼만한 페이지

- CPU 소켓 - 소켓 7

- CPU 소켓 - 슬로켓

- 칩 패키지 - 스루홀 기술

스루홀 기술은 인쇄회로기판의 구멍에 전자 부품을 삽입하여 납땜하는 실장 방식으로, 기계적 결합력이 높지만 생산 비용이 높아 SMT 기술로 대체되었으나, 특정 분야에서 여전히 사용되며 자동화 기술을 통해 발전을 모색하고 있다. - 칩 패키지 - 표면 실장 기술

표면 실장 기술(SMT)은 전자 부품을 인쇄 회로 기판 표면에 직접 납땜하는 기술로, 소형화, 자동화, 생산성 향상 등의 장점으로 첨단 전자 기기 제조에 필수적이지만, 정교한 기술과 장비, 수리 난이도 등의 단점도 존재한다. - 전문가의 참여가 필요한 문서 - 클릭당 지불

클릭당 지불 광고는 광고주가 광고 클릭당 비용을 지불하는 온라인 광고 방식으로, 정액제와 입찰 기반 모델이 있으며 검색엔진 결과 페이지 등에 게재되고 키워드 매칭, 광고 품질, 실시간 입찰 등이 노출 순위에 영향을 미치며 클릭 사기 등의 문제점도 존재하지만 인공지능 기반 타겟팅 기술과 함께 진화하고 있다. - 전문가의 참여가 필요한 문서 - 코넬 웨스트

코넬 웨스트는 하버드와 프린스턴에서 철학 박사 학위를 받고 여러 대학에서 교수로 재직한 미국의 철학자, 작가, 사회 활동가, 공공 지식인으로, 진보적 사회 운동에 참여하며 미국의 인종, 정치, 경제 문제에 대한 비판적 시각을 견지하고 2024년 미국 대통령 선거에 무소속으로 출마하기도 했다.

| 이중 직렬 패키지 | |

|---|---|

| 기본 정보 | |

| |

| 창립일 | 1973년 1월 10일 (인도네시아 민주당) |

| 재창당 | 1999년 2월 1일 |

| 이념 | 판차실라 민족주의 세속주의 수카르노주의 |

| 정치적 위치 | 중도-좌파 |

| 상징색 | 빨간색 |

| 의장 | 메가와티 수카르노푸트리 |

| 사무총장 | Hasto Kristiyanto |

| 재무 | Olly Dondokambey |

| 청소년 조직 | Taruna Merah Putih |

| 정치적 스펙트럼 | |

| 하원 | 128석 / 575석 (2019년) |

| 인민대표자회의 | 1999년: 153석 2004년: 109석 2009년: 95석 2014년: 109석 2019년: 128석 |

| 국제 관계 | |

| 국제 제휴 | 진보적 제휴 |

| 유럽 의회 그룹 | 사회민주진보동맹 |

| 웹사이트 | |

| 공식 웹사이트 | pdiperjuangan.id |

2. 종류

IC 패키징에는 여러 종류의 DIP가 있으며, 주로 재료에 따라 구분된다.

- '''세라믹 듀얼 인라인 패키지(CERDIP 또는 CDIP)'''

- '''플라스틱 듀얼 인라인 패키지(PDIP)'''

- '''축소형 플라스틱 듀얼 인라인 패키지(SPDIP)'''

- '''스키니 듀얼 인라인 패키지(SDIP 또는 SPDIP)'''

2. 1. 세라믹 듀얼 인라인 패키지 (CERDIP 또는 CDIP)

세라믹 듀얼 인라인 패키지(CERDIP 또는 CDIP)는 집적 회로(IC)를 포장하는 방식 중 하나로, 주로 포장 재료에 따라 구분되는 여러 DIP 변형 중 하나이다.[6] 높은 신뢰성이 요구되는 분야에 사용된다.

EPROM은 칩 다이 위에 투명 석영의 원형 창이 있는 세라믹 DIP로 판매되어 자외선으로 부품을 지울 수 있었다. 종종 동일한 칩은 일회성 프로그래밍 가능(OTP) 버전으로 창이 없는 더 저렴한 PDIP 또는 CERDIP 패키지로도 판매되었다. 창이 있는 패키지와 창이 없는 패키지는 마이크로컨트롤러 및 EPROM 메모리가 포함된 기타 장치에도 사용되었다. 창이 있는 CERDIP 패키지 EPROM은 많은 초기 IBM PC 호환 기종의 BIOS ROM에 사용되었으며, 접착 라벨로 창을 덮어 주변광 노출로 인한 의도하지 않은 삭제를 방지했다.

1979년의 한 연구에 따르면 플라스틱 14핀 DIP는 약 0.063USD이고 세라믹 패키지는 0.82USD였다.[7]

2. 2. 플라스틱 듀얼 인라인 패키지 (PDIP)

플라스틱 듀얼 인라인 패키지(PDIP)는 성형 플라스틱으로 만들어져 세라믹 패키지보다 비용이 훨씬 저렴하다. 1979년의 한 연구에 따르면 플라스틱 14핀 DIP는 약 0.063USD이고 세라믹 패키지는 0.82USD였다.[7]EPROM은 칩 다이 위에 투명 석영의 원형 창이 있는 세라믹 DIP로 판매되어 자외선으로 부품을 지울 수 있었다. 종종 동일한 칩은 일회성 프로그래밍 가능 (OTP) 버전으로 창이 없는 더 저렴한 PDIP 또는 CERDIP 패키지로도 판매되었다. 창이 있는 패키지와 창이 없는 패키지는 마이크로컨트롤러 및 EPROM 메모리가 포함된 기타 장치에도 사용되었다. 창이 있는 CERDIP 패키지 EPROM은 많은 초기 IBM PC 호환 기종의 BIOS ROM에 사용되었으며, 접착 라벨로 창을 덮어 주변광 노출로 인한 의도하지 않은 삭제를 방지했다.

2. 3. 축소형 플라스틱 듀얼 인라인 패키지 (SPDIP)

축소형 플라스틱 듀얼 인라인 패키지(SPDIP)는 PDIP보다 핀 간 간격(리드 피치)이 0.07인치(1.778mm)로 더 좁아, 높은 밀도를 제공한다.[6]2. 4. 스키니 듀얼 인라인 패키지 (SDIP 또는 SPDIP)

스키니 듀얼 인라인 패키지(SDIP 또는 SPDIP)[6]는 때때로 "좁은" 약 0.76cm 너비의 DIP를 지칭하는 데 사용되며, 일반적으로 24핀 이상인 DIP와 같이 "넓은" 약 1.52cm 너비의 DIP 패키지로 제공될 때 명확하게 설명해야 할 때 사용된다. "좁은" DIP 패키지에 대한 일반적인 전체 사양의 예는 300밀 바디 너비, 약 0.25cm 핀 피치이다.3. 응용 분야

DIP는 집적 회로(IC)를 비롯한 다양한 전자 장치 및 부품에 사용된다. 저항 네트워크, DIP 스위치, LED 세그먼트 디스플레이 및 막대 그래프 디스플레이, 전자기계식 릴레이 등에도 사용된다.[4] 또한 DIP 커넥터 플러그는 컴퓨터 및 기타 전자 장비에서 리본 케이블 연결에 흔히 사용된다.

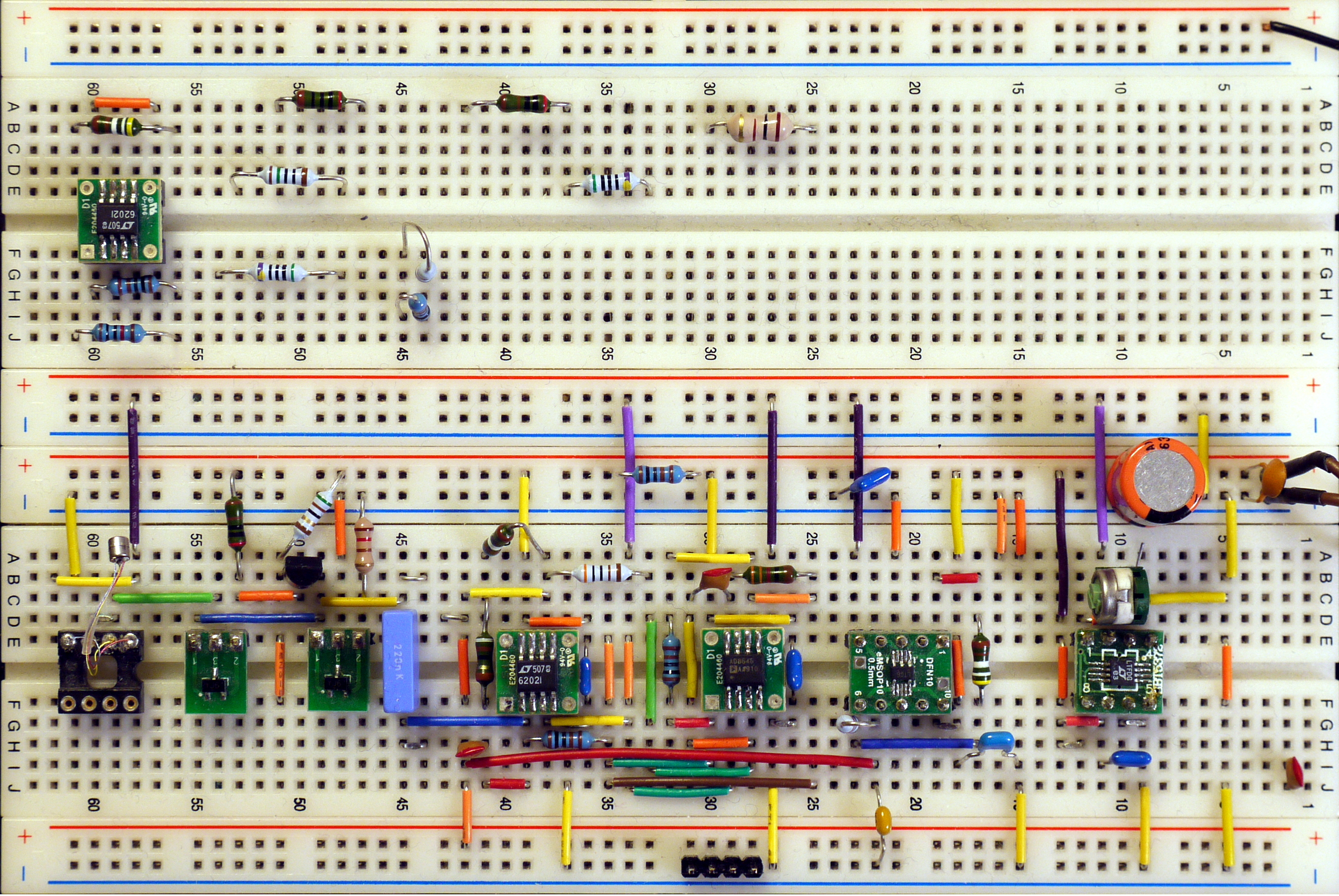

1970년대와 1980년대에 DIP는 마이크로 전자 산업의 주류였으며, 1990년대까지 널리 사용되었다. 플라스틱 리드 칩 캐리어(PLCC) 및 소형 외곽 집적 회로(SOIC)와 같은 표면 실장 기술(SMT) 패키지가 등장하면서 21세기 초 사용량이 감소했지만, 오늘날에도 여전히 사용되고 있다. DIP는 브레드보드를 이용한 회로 프로토타입 제작에 편리하다.

EPROM 및 범용 어레이 로직(GAL)과 같은 프로그래밍 가능한 장치는 외부 프로그래밍 회로를 통해 DIP를 쉽게 처리할 수 있어 오랫동안 인기가 있었다. 그러나 인 시스템 프로그래밍(ISP) 기술의 발전으로 이러한 장점은 빠르게 사라지고 있다.

3. 1. 장치 유형

DIP는 일반적으로 집적 회로(IC)에 사용된다. DIP 패키지의 다른 장치로는 저항 네트워크, DIP 스위치, LED 세그먼트 디스플레이 및 막대 그래프 디스플레이, 그리고 전자기계식 릴레이가 있다.[4]DIP 커넥터 플러그는 컴퓨터 및 기타 전자 장비에서 리본 케이블에 흔히 사용된다.

달라스 반도체(Dallas Semiconductor)는 IC 칩과 교체 불가능한 10년 수명 리튬 배터리를 포함하는 집적 DIP 실시간 시계(RTC) 모듈을 제조했다.[5]

개별 부품을 납땜할 수 있는 DIP 핀 헤더 블록은 구성 변경, 옵션 기능 또는 보정을 위해 구성 요소 그룹을 쉽게 제거해야 하는 경우에 사용되었다.

3. 2. 용도

DIP는 브레드보드에서 회로 프로토타입을 제작하는 데 편리하여 널리 사용된다.1970년대와 1980년대에 DIP는 마이크로 전자 산업의 주류였다. 1990년대까지 널리 사용되었으며, 플라스틱 리드 칩 캐리어(PLCC) 및 소형 외곽 집적 회로(SOIC)와 같은 새로운 표면 실장 기술(SMT) 패키지가 등장하면서 21세기 첫 10년 동안 사용이 감소했지만, 오늘날에도 여전히 사용되고 있다. 일부 최신 칩은 표면 실장 패키지 형태로만 제공되기 때문에, 여러 회사에서 다양한 프로토타입 어댑터를 판매하여 이러한 표면 실장 장치(SMD)를 DIP 장치처럼 사용할 수 있도록 한다. 이를 통해 스트립보드 및 천공 기판과 같은 스루홀 브레드보드 및 납땜 프로토타입 기판과 함께 사용할 수 있다. SMT는 대량 생산에는 유리하지만, 프로토타입 제작에는 어려움이 따르기 때문이다.

EPROM 및 범용 어레이 로직(GAL)과 같은 프로그래밍 가능한 장치의 경우, DIP는 외부 프로그래밍 회로를 통해 쉽게 처리할 수 있어 오랫동안 인기가 있었다. DIP 장치를 프로그래밍 장치의 소켓에 꽂기만 하면 되었기 때문이다. 그러나 현재 인 시스템 프로그래밍(ISP) 기술이 발전하면서 DIP의 이러한 장점은 빠르게 사라지고 있다.

1990년대까지는 20개 미만의 리드를 가진 장치는 새로운 형식 외에도 DIP 형식으로 제조되었다. 2000년경부터는 새로운 장치가 DIP 형식으로 제공되지 않는 경우가 많다.

4. 장착 방법

DIP는 스루홀 납땜 또는 소켓을 통해 장착할 수 있다. 소켓을 사용하면 장치를 쉽게 교체할 수 있으며, 납땜 시 과열로 인한 손상 위험을 없앨 수 있다. 일반적으로 소켓은 고가 또는 대형 IC에 사용되었다. 테스트 장비 또는 EPROM 프로그래머와 같이 장치를 자주 삽입하고 제거해야 하는 경우에는 제로 삽입력(ZIF) 소켓이 사용된다.

DIP는 교육, 설계 개발 또는 장치 테스트를 위한 임시 장착 방식으로 브레드보드와 함께 사용되기도 한다. 일부 애호가들은 일회성 제작 또는 영구적인 프로토타이핑을 위해 DIP를 사용하여 점대점 배선을 사용하는데, 이 방법의 일부로 물리적으로 거꾸로 뒤집혔을 때의 외관 때문에 "데드 버그 스타일"이라는 비공식적인 용어가 사용되기도 한다.

5. 구조

IC 칩을 포함하는 DIP의 본체(하우징)는 일반적으로 성형 플라스틱 또는 세라믹으로 만들어진다. 세라믹 하우징의 밀폐성은 극도로 높은 신뢰성이 요구되는 장치에 선호된다. 하지만, DIP의 대다수는 열경화성 성형 공정을 통해 제조되며, 이 공정에서는 에폭시 몰드 컴파운드를 가열하여 압력을 가해 장치를 캡슐화한다.

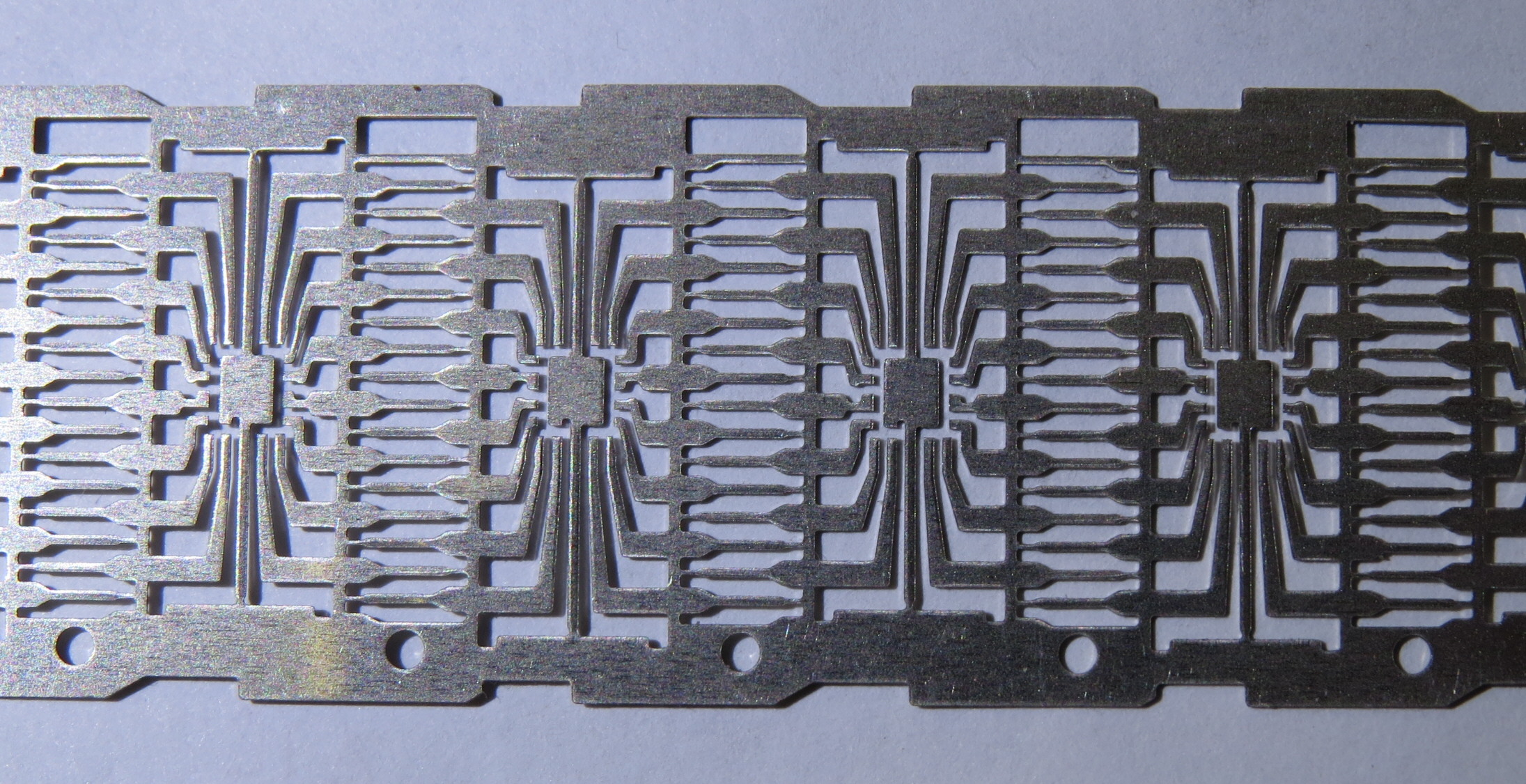

리드는 패키지의 긴 측면에서 봉합선을 따라 패키지의 상단 및 하단 평면에 평행하게 나오며, 약 90도(또는 그보다 약간 적게)로 구부러진다.[1] 세라믹(CERDIP) 패키지에서는 에폭시 또는 그라우트를 사용하여 두 반쪽을 밀폐하여 IC 내부의 다이를 보호하는 공기 및 수분 밀봉을 제공한다. 플라스틱 DIP(PDIP) 패키지는 일반적으로 리드 주변의 플라스틱 반쪽을 융착하거나 접착하여 밀봉하지만, 높은 수준의 밀폐성을 얻을 수는 없다.[1]

패키지 내부에는 하단 반쪽에 리드가 내장되어 있으며, 패키지 중앙에는 IC 다이가 시멘트 처리되는 직사각형 공간이 있다. 패키지의 리드는 주변을 따라 나오는 위치에서 다이를 둘러싼 직사각형 둘레를 따라 패키지 내부로 대각선으로 확장되며, 다이에서 가는 접촉부가 되도록 가늘어진다. 초미세 본드 와이어가 이러한 다이 주변 접촉부와 다이 자체의 본드 패드 사이에 용접되어 각 본드 패드에 하나의 리드를 연결하고, 마이크로 회로와 외부 DIP 리드 사이의 최종 연결을 만든다. 본드 와이어는 일반적으로 팽팽하지 않고 재료의 열팽창 및 수축을 위한 여유를 주기 위해 약간 위로 굽혀져 있다.[1]

일반적으로 회사 로고, 영숫자 코드 및 때로는 단어가 패키지 상단에 인쇄되어 제조사 및 유형, 제조 시기(일반적으로 연도와 주 번호로 표시) 등을 식별한다.[1]

다이 주변에서 패키지 주변의 두 줄까지 모든 리드를 기본적으로 방사형 패턴으로 단일 평면에 배치해야 한다는 필요성이 더 많은 리드 수를 가진 DIP 패키지가 리드 열 사이에 더 넓은 간격을 가져야 하는 주요 이유이다.[1] 큰 DIP 패키지(예: 모토로라 68000 CPU에 사용되는 DIP64)는 핀과 다이 사이에 긴 리드를 가지고 있어 고속 장치에 적합하지 않다.[1]

다른 유형의 DIP 장치는 매우 다르게 구성된다. 이들 대부분은 성형 플라스틱 하우징과 직선 리드 또는 패키지 하단에서 직접 뻗어 나오는 리드를 가지고 있다. 일부는 하우징은 일반적으로 바닥/뒷면이 열린 속이 빈 플라스틱 상자이며, 리드가 나오는 단단한 반투명 에폭시 재료로 채워진다. 다른 것들은 리드는 플라스틱에 성형된 구멍 또는 노치를 통해 나온다.[1]

6. 변형

IC를 위한 여러 DIP 변형이 존재하며, 주로 포장 재료에 따라 구분된다.

- '''세라믹 듀얼 인라인 패키지 (CERDIP 또는 CDIP)'''

- '''플라스틱 듀얼 인라인 패키지 (PDIP)'''

- '''축소형 플라스틱 듀얼 인라인 패키지 (SPDIP)''' – PDIP의 더 밀도가 높은 버전으로, 리드 피치는 약 0.18cm이다.

- '''스키니 듀얼 인라인 패키지 (SDIP 또는 SPDIP)'''[6] – 때로는 "좁은" 약 0.76cm 너비의 DIP를 지칭하는 데 사용되며, 일반적으로 24핀 이상인 DIP와 같이 "넓은" 약 1.52cm 너비의 DIP 패키지로 제공될 때 명확하게 설명해야 할 때 사용된다.

EPROM은 칩 다이 위에 투명 석영의 원형 창이 있는 세라믹 DIP로 판매되어 자외선으로 부품을 지울 수 있었다. 종종 동일한 칩은 일회성 프로그래밍 가능 (OTP) 버전으로 창이 없는 더 저렴한 PDIP 또는 CERDIP 패키지로도 판매되었다. 창이 있는 CERDIP 패키지 EPROM은 많은 초기 IBM PC 호환 기종의 BIOS ROM에 사용되었으며, 접착 라벨로 창을 덮어 주변광 노출로 인한 의도하지 않은 삭제를 방지했다.

성형 플라스틱 DIP는 세라믹 패키지보다 비용이 훨씬 저렴하다. 1979년의 한 연구에 따르면 플라스틱 14핀 DIP는 약 0.063USD이고 세라믹 패키지는 0.82USD였다.[7]

6. 1. 싱글 인라인 패키지 (SIP 또는 SIL 패키지)

연결 핀이 한 줄로 배열된 형태이다. 듀얼 인라인 패키지(DIP)만큼 널리 사용되지는 않지만, RAM 칩과 공통 핀을 가진 다수의 저항을 패키징하는 데 사용되었다. 일반적으로 최대 64개의 핀을 가진 DIP와 비교하여 SIP는 전형적으로 최대 24개의 핀을 가지며, 패키지 비용이 더 낮다.[9]단일 인라인 패키지의 한 변종은 리드 프레임의 일부를 방열 탭으로 사용한다. 이 다중 리드 전력 패키지는 예를 들어 오디오 전력 증폭기와 같은 응용 분야에 유용하다.

6. 2. 쿼드 인라인 패키지 (QIP)

QIP는 때때로 "QIL 패키지"라고도 불리며, DIL 패키지와 동일한 치수를 갖지만, 각 측면의 리드가 교대로 지그재그 형태로 구부러져 있어 DIL의 경우 2줄 대신 4줄의 솔더 패드를 맞출 수 있다. QIL 설계는 패키지 크기를 늘리지 않으면서 솔더 패드 간의 간격을 늘렸는데, 그 이유는 다음과 같다.

# 더욱 신뢰할 수 있는 납땜을 가능하게 했다. 오늘날에는 훨씬 더 좁은 솔더 패드 간격이 사용되고 있다는 점을 감안하면 이상하게 보일 수 있지만, QIL의 전성기였던 1970년대에는 DIL 칩에서 인접한 솔더 패드의 솔더 브리지가 때때로 문제였다.

# QIL은 또한 2개의 솔더 패드 사이에 구리 트랙을 배치할 가능성을 높였다. 이는 당시 표준 단면 단층 PCB에서 매우 유용했다.

7. 리드 수 및 간격

일반적으로 사용되는 JEDEC 표준을 따르는 DIP 패키지는 약 0.25cm (2.54mm)의 리드 간 간격(리드 피치)을 사용한다. 행 간 간격은 리드 수에 따라 다르며, 약 0.76cm (7.62mm) 또는 약 1.52cm (15.24mm)가 가장 일반적이다. 덜 일반적인 표준화된 행 간 간격으로는 약 1.02cm (10.16mm) 및 약 2.29cm (22.86mm), 그리고 약 0.18cm (1.778mm) 리드 피치를 가진 약 0.76cm (7.62mm), 약 1.52cm (15.24mm) 또는 약 1.91cm (19.05mm)의 행 간 간격이 있다.

구소련 및 동구권 국가들은 유사한 패키지를 사용했지만, 약 0.25cm (2.54mm) 대신 2.5mm의 미터법 핀 간 간격을 사용했다.

리드 수는 항상 짝수이다. 약 0.76cm (7.62mm) 간격의 경우 일반적인 리드 수는 8, 14, 16, 20개이며, 4, 6, 18, 24, 28개 리드는 덜 일반적이다. 짝수 개의 리드를 가지기 위해 일부 DIP는 내부 칩에 사용되지 않는 미연결 (NC) 리드를 갖거나,[10] 예를 들어 두 개의 접지 핀처럼 중복된다. 약 1.52cm (15.24mm) 간격의 경우 일반적인 리드 수는 24, 28, 32, 40개이며, 36, 42, 48, 52, 64개 리드는 덜 일반적이다. 모토로라 68000 및 Zilog Z180과 같은 일부 마이크로프로세서는 64개까지의 리드 수를 사용했으며, 이는 일반적으로 DIP 패키지의 최대 리드 수이다.[10]

8. 방향 및 리드 번호

그림과 같이, 리드는 핀 1부터 순차적으로 번호가 매겨진다. 패키지의 식별 노치(또는 들여쓰기, 페인트 점)가 상단에 있을 때, 핀 1은 장치의 왼쪽 상단 모서리이다.

예를 들어, 노치가 상단에 있는 14핀 DIP의 경우, 왼쪽 리드는 1부터 7까지(위에서 아래로) 번호가 매겨지고, 오른쪽 리드 열은 8에서 14까지(아래에서 위로) 번호가 매겨진다.

세그먼트 LED 표시기와 같이 일부 DIP 장치에서는 리드가 건너뛰는 경우가 있다. 이 경우에도 나머지 리드는 모든 위치에 리드가 있는 것처럼 번호가 매겨진다.

노치는 사람이 시각적으로 패키지의 방향을 식별할 수 있게 해줄 뿐만 아니라, 자동 칩 삽입 기계가 기계적 감지를 통해 칩의 올바른 방향을 확인할 수 있게 해준다.

9. 파생 기술

SOIC(Small Outline IC, 소형 외곽 IC)는 표면 실장 패키지의 일종으로, 특히 소비자 가전 제품과 개인용 컴퓨터에 널리 사용된다. PDIP(이중 직렬 패키지)의 축소 버전이며, SMT 장치로 만들기 위해 플라스틱 하우징 바닥면과 평행하게 납땜부를 평평하게 만드는 두 번째 굽힘이 있다. SOJ(소형 외곽 J-리드) 및 이름에 "SOP"("소형 외곽 패키지"의 약자)가 포함된 기타 SMT 패키지 또한 DIP에서 파생된 것으로 볼 수 있다. SOIC 패키지는 DIP 피치의 절반, SOP는 DIP 피치의 1/4 간격을 갖는다. (각각 2.54mm, 1.27mm 및 0.635mm)

핀 그리드 배열(PGA) 패키지는 DIP에서 발전된 형태이다. 대부분의 DIP와 동일하게 2.54mm 핀 간격을 가지며, 1980년대 초반부터 1990년대 중반까지 마이크로프로세서에 널리 사용되었다. 인텔의 80286부터 P5 펜티엄 프로세서를 사용한 개인용 컴퓨터 사용자들은 PGA 패키지에 익숙할 것이며, 이들은 종종 ZIF 소켓에 삽입되었다. PGA 소켓은 일부 DIP 장치와 물리적으로 호환되기도 하지만, 그 반대의 경우는 드물다.

참조

[1]

웹사이트

see for instance

https://web.archive.[...]

2010-01-02

[2]

서적

Electronic Inventions and Discoveries

Pergamon Press

[3]

서적

Handbook of Semiconductor Technology

John Wiley & Sons

[4]

서적

Electronic Inventions and Discoveries

Pergamon Press

[5]

웹사이트

Computer Museum

http://www.computerh[...]

2008-04-16

[6]

웹사이트

Microchip

http://www.microchip[...]

[7]

서적

Microelectronics Packaging Handbook: Semiconductor packaging

Springer

[8]

웹사이트

Single-in-Line Package (SIP)

https://eesemi.com/s[...]

[9]

서적

Integrated circuit, hybrid, and multichip module package design guidelines

https://books.google[...]

Wiley-IEEE

[10]

서적

CMOS digital integrated circuits

McGraw-Hill

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com