플립플롭

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

플립플롭은 클럭 신호의 엣지에서 입력 값을 받아 출력에 반영하는 순차 회로이다. SR, D, T, JK 플립플롭과 같은 다양한 종류가 있으며, 내부 논리 회로를 통해 데이터를 저장하는 기능을 한다. 초기에는 에클스-조던 트리거 회로로 시작하여, 1954년 몬트고메리 피스터에 의해 플립플롭 유형이 논의되었고, JK 플립플롭은 1953년 엘드레드 넬슨에 의해 명명되었다. 플립플롭은 SRAM으로 사용되며, CPU 레지스터, 캐시 메모리, DSP 등에 활용된다. 플립플롭의 안정적인 동작을 위해 개구 시간, 설정 시간, 유지 시간 등의 타이밍 요소를 고려해야 하며, 메타 안정성 문제도 발생할 수 있다. 플립플롭은 다중 출력 및 다치 논리로 일반화될 수 있다.

더 읽어볼만한 페이지

- 디지털 전자공학 - 트랜지스터-트랜지스터 논리

트랜지스터-트랜지스터 논리(TTL)는 1961년 제임스 L. 부이에 의해 발명된 바이폴라 접합 트랜지스터 기반의 디지털 회로 기술로, 텍사스 인스트루먼츠의 7400 시리즈를 통해 널리 사용되었으며, 저렴한 비용으로 디지털 기술 발전에 기여했다. - 디지털 전자공학 - 마이크로컨트롤러

마이크로컨트롤러는 프로세서, 메모리, 입출력 기능을 단일 칩에 통합하여 임베디드 시스템의 핵심이 되는 부품으로, 프로그램 내장 방식을 통해 소프트웨어만으로 제어 기능 변경이 가능하며, 현재는 32비트 ARM, MIPS 아키텍처 기반 제품이 주를 이루고, 저전력 소모, 소형화, 다양한 기능 통합을 특징으로 다양한 분야에서 활용된다. - 기억 장치 - EPROM

EPROM은 자외선을 사용하여 내용을 지울 수 있는 읽기 전용 메모리이며, MOSFET의 부유 게이트를 사용하여 데이터를 저장하고, 펌웨어 업데이트가 용이하여 소량 생산에 사용되었으나 EEPROM과 플래시 메모리에 의해 대체되었다. - 기억 장치 - 정적 램

정적 램(SRAM)은 전원이 공급되는 동안 데이터를 저장하며, 갱신 회로가 필요 없고 빠른 접근 속도를 가지는 휘발성 메모리 유형이다. - 전자공학 - 전자전

전자전은 적의 전투 능력을 저하시키기 위해 전자기 에너지를 사용하는 군사 작전이며, 전자 공격, 전자 보호, 전자 지원의 세 가지 영역으로 나뉘어 통신 방해, 레이더 교란, 스텔스 기술 등을 포함한다. - 전자공학 - 옴의 법칙

옴의 법칙은 1827년 게오르크 옴이 발표한, 전압(V)은 전류(I)와 저항(R)의 곱(V=IR)으로 표현되는, 전압, 전류, 저항 간의 관계를 나타내는 기본 법칙이다.

| 플립플롭 | |

|---|---|

| 개요 | |

| |

| 종류 | SR 플립플롭 D 플립플롭 JK 플립플롭 T 플립플롭 |

| 설명 | |

| 정의 | 두 개의 안정된 상태를 갖는 전자 회로 |

| 기능 | 2진수 정보를 저장하는 데 사용 디지털 시스템의 기본적인 메모리 요소 |

| 작동 방식 | 입력 신호에 따라 두 가지 상태 중 하나를 유지 특정 신호가 입력될 때 상태를 변경 |

| 응용 분야 | 컴퓨터 통신 제어 시스템 다양한 디지털 장치 |

| 다른 이름 | 래치 (latch) |

| 세부 종류 | |

| SR 플립플롭 | 두 개의 입력 (Set, Reset)을 가짐 S 입력으로 상태를 1로 설정 R 입력으로 상태를 0으로 설정 |

| D 플립플롭 | 하나의 데이터 입력 (D)을 가짐 클록 신호에 따라 D 입력 값을 저장 |

| JK 플립플롭 | 두 개의 입력 (J, K)을 가짐 SR 플립플롭의 문제점을 개선 J, K 입력 조합에 따라 다양한 동작 수행 |

| T 플립플롭 | 하나의 입력 (T)을 가짐 클록 신호가 입력될 때마다 상태 반전 |

| 추가 정보 | |

| 동기식과 비동기식 | 동기식: 클록 신호에 맞춰 동작 비동기식: 클록 신호 없이 즉시 동작 |

| 트리거 방식 | 에지 트리거: 클록 신호의 상승 또는 하강 에지에서 동작 레벨 트리거: 클록 신호의 높은 또는 낮은 레벨에서 동작 |

2. 종류

플립플롭과 래치는 '''SR'''("셋-리셋"), '''D'''("데이터"), '''T'''("토글"), '''JK''' 등 일반적인 유형으로 나눌 수 있다. 특정 유형의 동작은 특성 방정식으로 설명할 수 있으며, 이 방정식은 입력 신호 및/또는 현재 출력 에 따라 "다음" 출력()을 도출한다.

최초의 전자 래치는 1918년 영국의 물리학자 윌리엄 에클스와 F. W. 조던에 의해 발명되었다.[5][6] 처음에는 '에클스-조던 트리거 회로'라고 불렸으며, 진공관 두 개로 구성되었다.[7] 이 설계는 1943년 영국의 콜로서스 암호 해독 컴퓨터에 사용되었고,[8] 이러한 회로와 그 트랜지스터 버전은 집적 회로가 도입된 후에도 컴퓨터에서 흔히 사용되었지만, 논리 게이트로 만들어진 래치와 플립플롭도 현재 흔하다.[9][10] 초기 래치는 트리거 회로 또는 멀티바이브레이터로 다양하게 알려져 있었다.

플립플롭의 어원은 시소가 좌우로 기울어지는 모습[35]이나 플립플롭을 신었을 때 나는 소리인 'flip, flop'이라는 의성어에서 유래했다.[36] 영어에서는 방향 전환이나 태도, 결정의 전환 등을 의미하기도 한다.[37][38]

미국 제트 추진 연구소의 엔지니어인 P. L. 린들리에 따르면, SR, D, T, JK 플립플롭 유형은 1954년 몬트고메리 피스터가 UCLA에서 컴퓨터 설계에 관한 강의에서 처음 논의되었고, 그의 책 ''디지털 컴퓨터의 논리 설계''에 등장했다.[11][12]

2. 1. 래치 (Latch)

래치(Latch)는 1비트의 정보를 입력 신호가 바뀔 때까지 유지하는 회로이다. 출력 Q는 0 또는 1의 상태로 바뀔 수 있으며, 래치의 종류에 따라 하나 또는 두 개의 입력을 사용한다.논리 회로 시스템 설계 시, 필요에 따라 래치의 입력 반영 시점을 조절해야 할 때가 있다. 즉, 입력 신호가 들어와도 특정 시점까지는 Q의 상태 변화를 막는 제어 신호가 필요하다. 이 제어 신호를 게이트(gate) 또는 인에이블(enable)이라고 하며, 보통 E (E, EN, G 등으로 표시)로 표기한다. 게이트 신호는 입력 신호와는 별도로 존재하며, 이 신호가 있는 래치를 게이트 래치(gated latch)라고 한다.

E 신호가 없는 래치는 입력 상태가 즉시 출력에 반영된다. 반면 E 신호가 있는 게이트 래치는 E 신호가 활성화(active)되었을 때만 입력이 출력에 반영된다. E 신호가 활성화되면 입력이 계속 반영되는데, 이는 클럭 신호의 엣지(edge)와는 다르다. 게이트 래치는 내부에 AND 게이트 등을 사용하여 입력 반영 시점을 제어한다.

| E 신호가 없는 경우 | E 신호가 있는 경우 |

|---|---|

|  |

| 입력에 따라 Q의 상태가 변하거나 이전 상태를 유지한다. | EN 신호가 활성화되면 입력이 반영된다. |

래치는 게이트 신호(E, EN, G)가 1일 때 입력된 데이터를 출력하며, 게이트 신호가 계속 1이면 입력 신호가 그대로 출력 신호로 전달된다. 즉, 게이트 신호는 입력을 출력에 반영할지 여부를 결정하는 조건 입력이다.

투명(transparent) 또는 비동기식(asynchronous) 래치는 한 쌍의 교차 결합된 반전 소자를 중심으로 구성될 수 있다. 진공관, 바이폴라 접합 트랜지스터, 전계 효과 트랜지스터, 인버터, 그리고 반전 논리 게이트는 모두 실제 회로에서 사용되었다.

기본 증폭 단계는 반전되므로, 두 단계를 연속으로 연결(캐스케이드)하여 필요한 비반전 증폭기를 형성할 수 있다. 이 구성에서 각 증폭기는 다른 반전 증폭기에 대한 능동 반전 피드백 네트워크로 간주될 수 있다. 따라서 두 단계는 비반전 루프로 연결되지만, 회로 다이어그램은 일반적으로 대칭적인 교차 결합 쌍으로 그려진다.

정적 게이트를 구성 요소로 사용할 때 가장 기본적인 래치는 SR 래치이다.

상황에 따라 래치는 레지스터(register)라고도 불린다. 래치는 컴퓨터의 주기억장치나 캐시 메모리, 레지스터를 구성하는 기본 회로 중 하나이다. 래치는 조합회로에서 일반적으로 부정적인 성질로 여겨지는 입력 신호에 대한 출력 신호의 지연을 피드백 루프를 통해 정보를 유지하는 순서회로를 만드는데 사용된다. 그 구조는 계전기(릴레이)를 이용한 자기 유지 회로와도 유사하다. 플립플롭은 그 구조상 정보는 통전 중에만 유지되고, 전원이 차단되면 유지하고 있던 정보는 손실되는 휘발성이다.

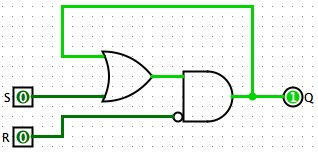

2. 1. 1. SR 래치

NOR 논리 게이트의 교차 되먹임 입력을 통해 만들어지는 가장 간단한 순차 회로가 SR 래치이다. S(''set'')는 출력 1을, R(''reset'')은 출력 0으로 되도록 한다는 의미를 갖는다. 저장된 현재 상태 출력은 Q로 표시한다.[39]S와 R 입력이 모두 0이면, Q와 출력 상태가 되먹임(feedback) 입력되어 이전 상태가 유지된다. S (''Set'')가 H이고, R (''Reset'')이 L이면, 출력 Q는 H가 된다. R이 H이고 S가 L로 입력되면, 출력 Q는 L 상태가 된다.[39]

| 특성표 | 여기표 | ||||||

|---|---|---|---|---|---|---|---|

| S | R | Q다음 | 동작 | Q | Q다음 | S | R |

| 0 | 0 | Q | 상태 유지 | 0 | 0 | 0 | |

| 0 | 1 | 0 | 리셋 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 세트 | 1 | 0 | 0 | 1 |

| 1 | 1 | 허용되지 않음 | 1 | 1 | 0 | ||

NAND 논리 게이트로 구성된 간단한 SR 래치도 있다. '''Set'''과 '''reset'''가 L 입력에 의해 활성화(active-low) 되고, 과 로 나타낸다. 래치는 입력 L에서 활성화 된다.[4]

R = S = 1 조합은 '''제한된 조합''' 또는 '''금지된 상태'''라고 하며, 두 NOR 게이트 모두 0을 출력하기 때문에 논리 방정식 Q = '''not''' 를 깨뜨린다. 이 조합은 ''두'' 입력이 동시에 낮아질 수 있는 회로(즉, ''제한된'' 상태에서 ''유지'' 상태로의 전환)에서도 부적절하다. 출력은 메타 안정 상태에 머물 수 있으며 게이트 간의 전파 시간 관계에 따라 결국 1 또는 0으로 고정될 수 있다(경쟁 조건).[14]

SR 래치의 특성 방정식은 다음과 같다.[14]

: 또는

다른 표현은 다음과 같다.[15]

: with

* A: S = 1, R = 0: 세트

- B: S = 0, R = 0: 유지

- C: S = 0, R = 1: 리셋

- D: S = 1, R = 1: 허용되지 않음

제한된 조합(D)에서 (A)로 전환하면 불안정한 상태가 된다.

]]

2. 1. 2. D 래치

D 래치는 SR 래치의 금지된 입력 상태를 방지하기 위해 고안된 래치이다. D(Data) 입력 하나만을 사용하며, NOT 게이트를 추가하여 S와 R 입력이 항상 반대 값을 가지도록 설계되었다.[4]

게이트 D 래치(''gated D latch'')는 D 입력 신호를 제어하는 게이트 신호(E, EN, G)를 추가하여 D 입력의 반영 여부를 결정한다. 게이트 신호가 활성화(1)되면 D 입력이 Q 출력에 그대로 반영되고, 비활성화(0)되면 이전 상태를 유지한다.[4]

위 진리표에서 E/C 입력이 0이면 D 입력 신호는 무시되고, 1이면 D 입력이 반영되어 Q 출력이 D와 같게 된다.

2. 1. 3. JK 래치

JK 래치는 SR 래치에서 S와 R이 모두 1인 경우를 토글(toggle, 출력 반전) 기능으로 대체한 래치이다. J와 K 입력이 모두 1일 때, 출력이 반전된다.[16]| J | K | Q다음 | 설명 |

|---|---|---|---|

| 0 | 0 | Q | 변화 없음 |

| 0 | 1 | 0 | 리셋 |

| 1 | 0 | 1 | 세트 |

| 1 | 1 | 토글 |

JK 래치는 SR 래치의 변형으로, 입력 조합 (1, 1)이 들어왔을 때 출력을 토글(0과 1 사이를 전환)한다.[16] 그러나 JK 래치는 토글 동작을 제어하는 클럭 신호가 없기 때문에, JK 플립플롭과 달리 (1,1) 입력 조합은 실용적이지 않다.[17]

2. 2. 플립플롭 (Flip-flop)

플립플롭(Flip-flop)은 클럭 신호의 엣지(상승 또는 하강)에서 입력 값을 받아 출력에 반영하는 회로로, 엣지 트리거형 래치라고도 불린다.최초의 전자 래치는 1918년 영국의 물리학자 윌리엄 에클스와 F. W. 조던에 의해 발명되었다.[5][6] 처음에는 '에클스-조던 트리거 회로'라고 불렸으며, 진공관 두 개로 구성되었다.[7] 이 설계는 1943년 영국의 콜로서스 암호 해독 컴퓨터에 사용되었고,[8] 이러한 회로와 그 트랜지스터 버전은 집적 회로가 도입된 후에도 컴퓨터에서 흔히 사용되었지만, 논리 게이트로 만들어진 래치와 플립플롭도 현재 흔하다.[9][10] 초기 래치는 트리거 회로 또는 멀티바이브레이터로 다양하게 알려져 있었다.

플립플롭은 컴퓨터의 주기억장치, 캐시 메모리, 레지스터를 구성하는 기본 회로 중 하나이다. 조합회로에서 입력에 대해 지연된 출력을 입력 쪽으로 피드백하여 정보 유지를 실현하고 순서회로로 만드는 특징이 있다.

플립플롭의 어원은 시소가 좌우로 기울어지는 모습[35]이나 플립플롭을 신었을 때 나는 소리인 'flip, flop'이라는 의성어에서 유래했다.[36] 영어에서는 방향 전환이나 태도, 결정의 전환 등을 의미하기도 한다.[37][38]

플립플롭과 래치는 '''SR'''("셋-리셋"), '''D'''("데이터"), '''T'''("토글"), '''JK''' 등 일반적인 유형으로 나눌 수 있다.

2. 2. 1. D 플립플롭

D 플립플롭은 가장 널리 사용되는 플립플롭으로, 클럭 신호의 특정 부분(예: 클럭의 상승 에지)에서 D(Data) 입력 값을 캡처하여 Q 출력에 반영한다. 캡처된 값은 Q 출력이 된다. 다른 시간에는 출력 Q가 변경되지 않는다.[40] D는 데이터(''data'') 또는 ''delay''로 알려져 있다.

D 플립플롭의 동기 클럭 신호는 상승 엣지와 하강 엣지를 사용한다. 심볼에서 > 앞에 동그라미를 붙이면 하강 엣지를 사용하고 있다는 뜻이다.

D 플립플롭 진리표:

| Clock | D | Qnext |

|---|---|---|

| 상승 엣지 (Rising edge) | 0 | 0 |

| 상승 엣지 (Rising edge) | 1 | 1 |

| 엣지 없음 | X | Q |

- 'X'표시는 ''Don't care'' 조건을 말한다. H와 L 어느 것이든 상관이 없다는 뜻이다.

IC의 대부분의 D형 플립플롭은 SR 플립플롭과 마찬가지로 설정 또는 재설정 상태로 강제될 수 있는 기능을 가지고 있다(D 및 클럭 입력을 무시함). 일반적으로 불법적인 S = R = 1 조건은 D형 플립플롭에서 해결된다. S = R = 0으로 설정하면 플립플롭이 위에서 설명한 대로 동작한다.

| 입력 | 출력 | ||||

|---|---|---|---|---|---|

| S | R | D | > | Q | |

| 0 | 1 | X | X | 0 | 1 |

| 1 | 0 | X | X | 1 | 0 |

| 1 | 1 | X | X | 1 | 1 |

D 플립플롭은 시프트 레지스터의 기초를 형성하며, 이는 많은 전자 장치의 필수적인 부분이다. D 플립플롭이 D형 "투명 래치"보다 우수한 점은 D 입력 핀의 신호가 플립플롭이 클럭될 때 캡처되고, 후속 D 입력의 변경은 다음 클럭 이벤트까지 무시된다는 것이다. 예외적으로 일부 플립플롭에는 Q를 0으로 재설정하는 "재설정" 신호 입력이 있으며, 클럭과 비동기 또는 동기일 수 있다.

위 회로는 클럭의 각 활성 전이에서 레지스터의 내용을 오른쪽으로 한 비트 위치만큼 시프트한다. 입력 X는 왼쪽 끝 비트 위치로 시프트된다.

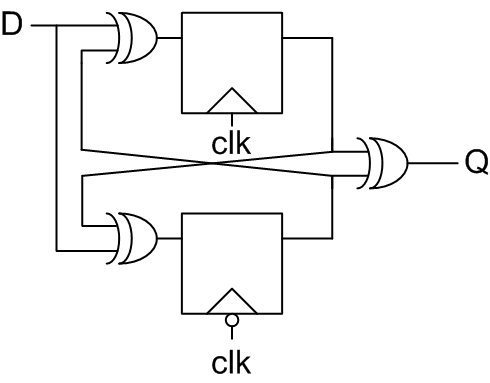

마스터-슬레이브 D 플립플롭은 두 개의 게이트형 D 래치를 직렬로 연결하고, 하나의 활성화 입력을 반전시켜 생성된다.

클럭의 상승 에지와 하강 에지 모두에서 새로운 값을 읽는 플립플롭을 이중 에지 트리거 플립플롭이라고 한다.

2. 2. 2. T 플립플롭

T 플립플롭은 T(Toggle) 입력이 HIGH(1)일 때 클럭 신호가 들어올 때마다 상태가 변경(토글)되는 플립플롭이다. T 입력이 LOW(0)이면 이전 상태를 유지한다. 이러한 동작은 XOR 연산을 사용하여 다음과 같은 특성 방정식으로 설명할 수 있다.[27]

:

이는 다음 진리표와 같다.

T 입력이 HIGH로 유지되면 T 플립플롭은 클럭 주파수를 2로 나눈다. 예를 들어 클럭 주파수가 4 MHz이면 출력 주파수는 2 MHz가 된다. 이러한 '나누기' 기능은 다양한 디지털 카운터에 활용된다. T 플립플롭은 JK 플립플롭(J, K 핀을 함께 연결하여 T처럼 동작)이나 D 플립플롭(T 입력 XOR Q이전이 D 입력을 구동)으로 구현할 수 있다.

T 플립플롭은 토글 플립플롭 또는 카운터라고도 불리며, T 단자에 1주기 변화(High→Low→High)가 입력될 때마다 출력이 반전된다.

2. 2. 3. JK 플립플롭

JK 플립플롭은 RS 플립플롭의 동작을 확장한 것으로, J = K = 1 조건을 "플립" 또는 토글 명령으로 해석한다.[27] 즉, 출력을 현재 값의 논리적 보수로 변경한다. J = K = 0으로 설정하면 현재 상태를 유지한다.JK 플립플롭의 구체적인 동작은 다음과 같다.

- J = 1, K = 0 조합은 플립플롭을 설정하는 명령이다.

- J = 0, K = 1 조합은 플립플롭을 리셋하는 명령이다.

- J = K = 1 조합은 플립플롭을 토글하는 명령이다.

D 플립플롭을 합성하려면 K를 J의 보수로 설정하면 되고(입력 J는 입력 D로 작용), T 플립플롭을 합성하려면 K를 J와 같게 설정하면 된다. 따라서 JK 플립플롭은 SR 플립플롭, D 플립플롭, 또는 T 플립플롭으로 구성하여 작동할 수 있는 범용 플립플롭이다.[27]

JK 플립플롭의 특성 방정식은 다음과 같다.

:

JK 플립플롭의 동작을 나타내는 진리표는 다음과 같다.[27]

| 특성표 | 여기 표 | |||||||

|---|---|---|---|---|---|---|---|---|

| J | K | 설명 | Qnext | Q | Qnext | 설명 | J | K |

| 0 | 0 | 상태 유지 | Q | 0 | 0 | 변경 없음 | 0 | |

| 0 | 1 | 리셋 | 0 | 0 | 1 | 설정 | 1 | |

| 1 | 0 | 설정 | 1 | 1 | 0 | 리셋 | 1 | |

| 1 | 1 | 토글 | 1 | 1 | 변경 없음 | 0 | ||

플립플롭은 내부가 논리 회로로 구성되어 데이터를 저장할 수 있어, 컴퓨터의 정적 램(SRAM) 같은 기억 장치를 구성하는 회로로 자주 사용된다. 동적 램(DRAM)과 비교했을 때, 주기적인 리프레시 동작(재기록)이 필요 없어, 기억 영역에 대한 간단하고 빠른 접근이 가능하다. 그러나 1비트당 트랜지스터 수와 배선이 DRAM보다 복잡해지기 때문에, 비트당 비용은 높아진다.[35][36][37][38]

프리셋(preset)은 주로 기기에 전원을 넣고 전원 전압이 일정하게 안정된 후 플립플롭의 출력 상태를 미리 설정된 값으로 설정하여 기기 동작 시작 전 준비(초기화)를 위해 사용된다. 클리어(Clear)도 프리셋과 비슷하게 사용되는 경우가 있지만, 기기 동작 중에 Q값을 0으로 설정하는 데 사용된다.[26] 다만, 프리셋과 클리어를 어떻게 사용하는지는 기기의 논리 회로 설계에 따라 달라진다.[26]

플립플롭의 안정적인 동작을 보장하기 위해서는 다음과 같은 타이밍 파라미터를 고려해야 한다.

3. 역사

최초의 전자 래치는 1918년 영국의 물리학자 윌리엄 에클스와 F. W. 조던에 의해 발명되었다.[5][6] 처음에는 ''에클스-조던 트리거 회로''라고 불렸으며, 두 개의 능동 소자(진공관)로 구성되었다.[7] 이 설계는 1943년 영국의 콜로서스 암호 해독 컴퓨터에 사용되었고,[8] 이러한 회로와 그 트랜지스터 버전은 집적 회로가 도입된 후에도 컴퓨터에서 흔히 사용되었지만, 논리 게이트로 만들어진 래치와 플립플롭도 현재 흔하다.[9][10] 초기 래치는 트리거 회로 또는 멀티바이브레이터로 다양하게 알려져 있었다.

미국 제트 추진 연구소의 엔지니어인 P. L. 린들리에 따르면, SR, D, T, JK 플립플롭 유형은 1954년 몬트고메리 피스터가 UCLA에서 컴퓨터 설계에 관한 강의에서 처음 논의되었고, 그의 책 ''디지털 컴퓨터의 논리 설계''에 등장했다.[11][12] 당시 린들리는 휴즈 항공에서 엘드레드 넬슨 밑에서 일하고 있었는데, 넬슨은 두 입력이 모두 켜져 있을 때(논리적 "1") 상태가 변경되는 플립플롭에 JK라는 용어를 만들어냈다. 다른 이름들은 피스터가 만들어냈다. 린들리는 엘드레드 넬슨으로부터 JK 플립플롭에 대한 이야기를 들었다고 설명하는데, 넬슨은 휴즈 항공에서 일하면서 이 용어를 만든 장본인이다. 당시 휴즈에서 사용 중이던 플립플롭은 모두 나중에 J-K로 알려지게 된 유형이었다. 논리 시스템을 설계하면서 넬슨은 플립플롭 입력에 다음과 같이 문자를 할당했다. #1: A & B, #2: C & D, #3: E & F, #4: G & H, #5: J & K. 넬슨은 1953년에 출원한 특허 출원에서 "''j''-입력"과 "''k''-입력"이라는 표기법을 사용했다.[13]

4. 장단점

이러한 특성 때문에, 최근에는 비교적 소용량이라도 고속 동작이 필요한 휘발성 램 영역에서는 플립플롭 기반의 정적 램(SRAM)을 CPU의 레지스터나 캐시 메모리, DSP 등에 사용하고, 대용량이 필요한 일반적인 휘발성 램 영역에서는 주로 동적 램(DRAM)을 사용하는 등, 각각의 특징을 살려 활용하고 있다.

5. 추가 기능

6. 타이밍 고려 사항

이러한 타이밍 제약 조건을 지키지 않으면 메타 안정성 문제가 발생할 수 있다. 메타 안정성은 두 입력 신호가 거의 동시에 변할 때 출력이 불안정해지는 현상으로, 데이터 손실이나 프로그램 충돌을 유발할 수 있다.[29]

메타 안정성을 방지하기 위한 방법은 다음과 같다.

플립플롭의 또 다른 중요한 타이밍 파라미터는 클럭-투-출력 지연(Clock-to-Output Delay, tCO) 또는 전파 지연(tP)이다. 이는 플립플롭이 클럭 신호 이후 출력을 변경하는 데 걸리는 시간이다.

시프트 레지스터와 같이 동일한 클럭을 공유하는 플립플롭을 직렬로 연결할 때는, 이전 플립플롭의 tCO가 다음 플립플롭의 유지 시간(th)보다 길어야 한다. 또한, 정상 작동을 위해 클럭 주기는 tsu + th의 합보다 커야 한다.

7. 일반화

플립플롭은 적어도 두 가지 방식으로 일반화할 수 있다. 하나는 1-of-2 대신 1-of-N으로 만드는 것이고, 다른 하나는 두 개 이상의 상태를 갖는 논리에 적용하는 것이다. 1-of-3 인코딩 또는 다치 3진 논리의 특수한 경우에는 이러한 요소를 "플립플랩플롭"(flip-flap-flop)이라고 할 수 있다.[30]

기존의 플립플롭은 두 개의 상보적인 출력 중 정확히 하나만 높은 값을 갖는다. 이것은 N개의 출력 중 정확히 하나만 높은 값을 갖는 (또는 N개 중 정확히 하나만 낮은 값을 갖는) 메모리 요소로 일반화할 수 있다. 따라서 출력은 항상 원핫(또는 "원콜드") 표현이다. 구성은 기존의 상호 결합 플립플롭과 유사하며, 각 출력은 높은 값일 때 다른 모든 출력을 억제한다.[31] 또는 출력당 하나씩 더 많거나 적은 기존의 플립플롭을 사용하여 한 번에 하나만 참이 될 수 있도록 추가 회로를 사용할 수 있다.[32]

7. 1. 다중 출력 플립플롭

Edge-triggered영어 D 플립플롭은 동적 논리를 사용하는 고속 집적 회로에서 자주 구현된다. 이는 디지털 출력이 소자가 전이되지 않는 동안 기생 소자 커패시턴스에 저장됨을 의미한다. 이 설계는 하나 이상의 내부 노드를 단순히 방전시킴으로써 리셋을 용이하게 한다. 일반적인 동적 플립플롭 종류는 진정한 단상 클록(TSPC) 유형으로, 적은 전력으로 고속에서 플립플롭 동작을 수행한다. 그러나 동적 플립플롭은 일반적으로 정적 또는 저속 클록에서는 작동하지 않는데, 충분한 시간이 주어지면 누설 경로가 기생 커패시턴스를 충분히 방전시켜 플립플롭이 잘못된 상태로 들어갈 수 있기 때문이다.[1]7. 2. 다치 논리 플립플롭

기존 플립플롭은 두 개의 상보적인 출력 중 정확히 하나만 높은 값을 갖는다. 이를 다치 논리를 위한 메모리 요소로 일반화할 수 있다. 이 경우 메모리 요소는 제어 입력이 변경될 때까지 논리 상태 중 하나를 정확히 유지한다.[33] 또한 다치 클럭을 사용하여 새로운 클럭 전환을 가능하게 할 수도 있다.[34] 3진 논리와 같이 다치 논리를 사용하는 특별한 경우, 이러한 요소를 "플립플랩플롭"(flip-flap-flop)이라고 부르기도 한다.[30]참조

[1]

웹사이트

Digital Logic Handbook Flip Chip™ Modules

http://www.bitsavers[...]

Digital Equipment Corporation

[2]

서적

Digital electronics and design with VHDL

https://books.google[...]

Morgan Kaufmann

2008

[3]

웹사이트

Latches and Flip Flops

http://rfic.eecs.ber[...]

[4]

서적

Fundamentals of Logic Design

PWS

1995

[5]

특허

Improvements in ionic relays

1920-08-05

[6]

간행물

Report of the Eighty-seventh Meeting of the British Association for the Advancement of Science: Bournemouth: 1919, September 9–13

https://archive.org/[...]

1919

[7]

서적

IBM's 360 and early 370 systems

https://archive.org/[...]

MIT Press

1991

[8]

저널

The Design of Colossus

http://www.ivorcatt.[...]

1983

[9]

서적

Introduction to electronics

https://books.google[...]

Delmar Thomson (Cengage) Learning

2000

[10]

서적

The Electronics problem solver, Volume 1

https://books.google[...]

Research & Education Assoc.

1998

[11]

저널

letter dated June 13, 1968

1968-08

[12]

서적

Logical Design of Digital Computers

https://books.google[...]

Wiley

1958

[13]

특허

High-speed printing system

https://patentimages[...]

1958-09-02

[14]

서적

Foundations of Digital Logic Design

https://books.google[...]

World Scientific

1998

[15]

웹사이트

Summary of the Types of Flip-flop Behaviour

https://www.ee.usyd.[...]

2018-04-16

[16]

서적

Mathematical Systems Theory I: Modelling, State Space Analysis, Stability and Robustness

https://books.google[...]

Springer

2006

[17]

서적

Digital design and computer organization

https://books.google[...]

CRC Press

2004

[18]

서적

The Architecture of Pipelined Computers

McGraw-Hill

1981

[19]

저널

Circuit implementation of high-speed pipeline systems

1965

[20]

저널

Latched Carry-Save Adder

1965-03

[21]

서적

The Microarchitecture of Pipelined and Superscalar Computers

https://books.google[...]

Springer

1999

[22]

저널

Optimal Pipelining in Supercomputers

ACM

1986-05

[23]

웹사이트

The D Flip-Flop

https://web.archive.[...]

2016-06-05

[24]

웹사이트

Edge-Triggered Flip-flops

https://web.archive.[...]

2011-12-15

[25]

웹사이트

A Survey of Digital Computer Memory Systems

https://ieeexplore.i[...]

[26]

웹사이트

SN7474 TI datasheet

https://www.ti.com/l[...]

[27]

서적

Logic and Computer Design Fundamentals, 3rd Edition

Pearson Education International

2004

[28]

서적

Digital Design and Computer Architecture - ARM Edition

Morgan Kaufmann, Waltham, MA

2016

[29]

저널

Anomalous Behavior of Synchronizer and Arbiter Circuits

1973-04

[30]

간행물

The ternary computer

https://scholar.goog[...]

IET

1964-02

[31]

웹사이트

Ternary "flip-flap-flop"

https://web.archive.[...]

2009-10-17

[32]

특허

Flip flop supporting glitchless operation on a one-hot bus and method

2005-12-13

[33]

저널

Flip-Flops for Multiple-Valued Logic

1976-03

[34]

저널

Research into ternary edge-triggered JKL flip-flop

1991-07

[35]

웹사이트

順序回路、フリップフロップ

https://www.renesas.[...]

2023-09-08

[36]

웹사이트

フリップフロップ (flip-flop) の語源

http://itdict.ddo.jp[...]

2013-06-05

[37]

뉴스

ニュースの英語

読売新聞

2008-12-06

[38]

웹사이트

【“サンダル”だけじゃない】flip-flopの意味:意見を突然変える | 上級英語ウェブメディア らいトレ

https://lion-eigo.co[...]

2023-09-08

[39]

서적

Latches and Flip-Flops

PWS

[40]

웹인용

Edge-Triggered Flip-flops

http://www.ee.usyd.e[...]

2013-09-16

[41]

서적

Logic and Computer Design Fundamentals, 3rd Edition

Pearson Education International

관련 사건 타임라인

( 최근 20개의 뉴스만 표기 됩니다. )

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com