연산 증폭기

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

연산 증폭기는 두 입력 단자 간의 전압 차이를 증폭하는 차동 증폭기로, 다양한 전자 회로에서 핵심적인 역할을 한다. 1941년 "가산 증폭기"로 처음 개발되었으며, 1968년 μA741 출시를 통해 대중화되었다. 연산 증폭기는 이상적인 특성을 갖는 것으로 가정하여 회로를 설계하지만, 실제로는 유한한 개루프 이득, 입력 임피던스, 출력 임피던스, 대역폭 등의 제약이 존재한다. 음의 피드백을 사용하여 안정적인 동작을 확보하며, 반전 증폭기, 비반전 증폭기, 가산 증폭기, 미분기, 적분기 등 다양한 회로로 구성될 수 있다. 연산 증폭기는 제조 공정, 입력단 트랜지스터, 용도, 위상 보상 유무 등에 따라 다양한 종류로 분류되며, 오디오, 비디오, 필터, 전압 조정기 등 광범위한 응용 분야에서 사용된다.

더 읽어볼만한 페이지

- 증폭기 - 중합효소 연쇄 반응

DNA 중합 효소를 사용하여 DNA 특정 부위를 복제 및 증폭하는 중합효소 연쇄 반응(PCR)은 유전체 연구, 분자생물학, 법의학, 의학 진단 등 다양한 분야에서 활용되는 기술로, 캐리 멀리스에 의해 고안되어 발전해왔다. - 증폭기 - 주파수 응답

주파수 응답은 시스템의 주파수별 특성을 분석하기 위해 입력 신호에 따른 출력 신호를 측정하고, 이를 크기와 위상으로 표현하며, 선형 시불변 시스템의 경우 전달 함수를 통해 분석한다. - 증폭 회로 - 저잡음 증폭기

저잡음 증폭기(LNA)는 통신 시스템에서 약한 신호를 증폭하고 잡음을 최소화하여 수신 감도를 향상시키는 필수 부품으로, 전파망원경, 휴대전화, GPS 등 다양한 분야에서 활용되며, 낮은 잡음 지수와 충분한 이득을 갖도록 설계되어 시스템의 신호대 잡음비를 개선한다. - 증폭 회로 - 메가폰

메가폰은 소리를 멀리 전달하는 기구로, 음향식과 전자식으로 구분되며, 고대 그리스 시대부터 사용되었고, 1878년 토머스 에디슨에 의해 '메가폰'이라는 용어가 처음 사용되었으며, 1954년에는 휴대성을 높인 트랜지스터 메가폰이 개발되어 현재 다양한 분야에서 활용된다. - 전자 회로 - 트랜지스터-트랜지스터 논리

트랜지스터-트랜지스터 논리(TTL)는 1961년 제임스 L. 부이에 의해 발명된 바이폴라 접합 트랜지스터 기반의 디지털 회로 기술로, 텍사스 인스트루먼츠의 7400 시리즈를 통해 널리 사용되었으며, 저렴한 비용으로 디지털 기술 발전에 기여했다. - 전자 회로 - 바이어스

바이어스는 전자 회로에서 부품의 동작점을 설정하여 원하는 특성을 얻는 과정으로, 선형 증폭기에서는 트랜지스터가 능동 영역에서 동작하도록 직류 전압과 전류를 제공하며, 진공관에서는 그리드 바이어스를 통해 동작점을 조절하고, 마이크로폰에서는 접합형 전계 효과 트랜지스터의 동작 전류를, 자기 테이프 녹음에서는 교류 바이어스 기법을 의미한다.

| 연산 증폭기 | |

|---|---|

| 기본 정보 | |

| |

| 유형 | 개별 회로 집적 회로 |

| 발명자 | 칼 D. 스와젤 주니어 |

| 핀 | V+: 비반전 입력 V−: 반전 입력 Vout: 출력 VS+: 양극 전원 공급 장치 VS−: 음극 전원 공급 장치 |

| 기호 | [[File:Op-amp symbol.svg|250px]] |

| 기호 설명 | 대표적인 연산 증폭기의 회로도 기호. 핀은 위에 나열된 대로 레이블이 지정됨. |

| 추가 정보 | |

| 가격 | 100 미국 달러 |

| Apex OP PA98 | Apex OP PA98 모듈 판매 가격: 207.51 미국 달러 |

| 기타 정보 | |

| 응용 분야 | 싱글 엔드, 유사 차동 및 완전 차동 ADC 입력 이해하기 아날로그 디바이스 MT-044 튜토리얼 |

2. 연산 증폭기의 역사

연산 증폭기는 1941년 벨 연구소의 칼 D. 스워트젤 주니어가 출원한 "가산 증폭기"에서 처음 발견되었다.[27] 이 설계는 세 개의 진공관을 사용하여 90dB의 이득을 달성했으며, 제2차 세계 대전 기간 동안 M9 포병 조준기에 사용되어 연합군의 승리에 기여했다.[27]

연산 증폭기는 기본적으로 두 입력 단자, 즉 비반전 입력(+)과 반전 입력(-) 간의 전압 차이를 증폭하는 차동 증폭기이다.[4] 출력 전압 ''V''out은 개방 루프 이득 *A*OL (또는 *A*d)과 입력 전압 차이의 곱으로 나타낼 수 있다.

회로 이론상으로는 “이상적인 연산 증폭기(ideal op-amp)”라는 회로를 가정한다.

1947년, 컬럼비아 대학교의 존 R. 라가지니(John R. Ragazzini)의 논문에서 연산 증폭기가 처음으로 공식적으로 정의되고 명명되었다.[28] 이 논문에서는 로에베 줄리(Loebe Julie)가 설계한, 반전 입력과 비반전 입력을 모두 가진 최초의 연산 증폭기를 소개했다.[27]

1949년, 에드윈 A. 골드버그는 초퍼 안정화 연산 증폭기를 설계했다.[29] 초퍼 안정화 연산 증폭기는 출력 드리프트와 직류 오프셋을 크게 줄여 연산 증폭기의 성능을 향상시켰다.

1953년, 조지 A. 필브릭(George A. Philbrick) 연구소에서 K2-W 모델을 출시하면서 진공관 연산 증폭기가 상용화되었다.[27]

1961년, 고체, 분리형 연산 증폭기가 생산되기 시작했다.

1963년, 페어차일드 반도체(Fairchild Semiconductor)의 밥 위들러(Bob Widlar)가 최초의 모놀리식 집적 회로 연산 증폭기인 μA702를 출시했다.

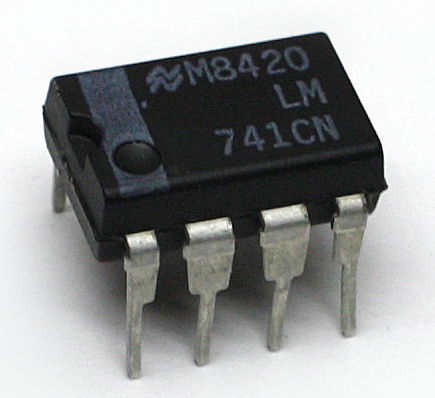

1968년, μA741이 출시되어 연산 증폭기의 대중화를 이끌었다. μA741은 칩 내부에 30pF 보상 커패시터를 포함하여 무조건 안정성을 확보했다.[17]

1970년대에는 FET를 사용한 고속, 저입력 전류 설계가 시작되었고, 1980년대에는 MOSFET로 만들어진 연산 증폭기가 등장했다. 1972년에는 단일측 전원 연산 증폭기가 생산되기 시작했다.

최근 아날로그 회로의 전원 전압이 감소함에 따라 저전압 연산 증폭기가 도입되었으며, 최신 연산 증폭기는 레일 투 레일 출력을 갖는 경우가 많다.[17]

3. 연산 증폭기의 동작 원리

:

여기서 ''A''OL은 증폭기의 개방 루프 이득이다.[4]

개방 루프 이득 *A*OL은 일반적으로 매우 크기 때문에(집적 회로 연산 증폭기의 경우 100,000 이상, +100 dB에 해당[4]), *V*+와 *V*− 사이의 미세한 마이크로볼트 차이라도 증폭기를 클리핑 또는 포화 상태로 몰아넣을 수 있다.[4] *A*OL의 크기는 제조 공정에 의해 잘 제어되지 않으므로, 개방 루프 증폭기를 독립형 차동 증폭기로 사용하는 것은 비실용적이다.[4]

음의 피드백 없이, 재생을 위한 양의 피드백을 선택적으로 사용하는 경우, ''개방 루프'' 연산 증폭기는 비교기 역할을 하지만, 비교기 IC가 더 적합하다.[4]

실제 회로에서는 예측 가능한 동작을 위해 출력 전압의 일부를 반전 입력에 적용하여 음의 피드백을 사용한다.[5] '폐루프' 피드백은 회로의 이득을 크게 감소시킨다. 음의 피드백을 사용하면 회로의 전체 이득과 응답은 연산 증폭기 특성이 아닌 피드백 네트워크에 의해 주로 결정된다. 피드백 네트워크가 연산 증폭기의 입력 임피던스에 비해 작은 값의 부품으로 구성된 경우, 연산 증폭기의 개루프 응답 ''A''OL 값은 회로 성능에 심각한 영향을 미치지 않는다.[5] 이러한 맥락에서 입력 단자의 높은 입력 임피던스와 출력 단자의 낮은 출력 임피던스는 연산 증폭기의 특히 유용한 특징이다.

입력, 출력 및 피드백 회로가 있는 연산 증폭기 회로의 입력에 대한 응답은 수학적으로 전달 함수에 의해 특징지어지며, 원하는 전달 함수를 갖도록 연산 증폭기 회로를 설계하는 것은 전기 공학의 영역이다. 전달 함수는 아날로그 컴퓨터와 같이 연산 증폭기의 대부분의 응용 분야에서 중요하다.

예를 들어, 오른쪽 비반전 증폭기에서 분압기 ''R''f, ''R''g를 통한 음의 피드백의 존재는 '폐루프 이득' ''A''CL = 을 결정한다. ''V''out이 반전 입력을 ''V''in과 같은 전압으로 당길 만큼 충분할 때 평형이 확립된다. 따라서 전체 회로의 전압 이득은 이다. 간단한 예로, ''V''in = 1 V이고 Rf = ''R''g이면, ''V''out은 2 V가 되는데, 이는 ''V''−를 1 V로 유지하는 데 필요한 정확한 양이다. ''R''f, ''R''g 네트워크에 의해 제공되는 피드백 때문에 이것은 '폐루프' 회로이다.[5]

이 회로를 분석하는 또 다른 방법은 다음과 같은 가정을 하는 것이다.[5]

# 연산 증폭기가 선형 모드로 작동할 때 비반전(+) 및 반전(−) 핀 사이의 전압 차이는 무시할 수 있을 정도로 작다.

# (+) 및 (−) 핀의 입력 임피던스는 회로의 다른 저항보다 훨씬 크다.

가정 1에 따라 입력 신호 ''V''in이 (+) 및 (−) 핀 모두에 나타나므로, 와 같은 ''R''g를 통한 전류 ''i''가 생성된다.

:

키르히호프의 전류 법칙에 따르면 같은 전류가 노드에 들어오는 만큼 나가야 하며, 가정 2에 따라 (−) 핀으로의 임피던스는 거의 무한대이므로, 거의 모든 같은 전류 ''i''가 ''R''f를 통해 흐르고 출력 전압을 생성한다고 가정할 수 있다.

:

항을 결합하여 폐루프 이득 ''A''CL을 결정한다.

:

연산 증폭기의 순 개방 루프 소신호 전압 이득은 약 4개의 트랜지스터의 전류 이득 hfe의 곱으로 결정된다. 실제로, 일반적인 741 스타일 연산 증폭기의 전압 이득은 약 200,000 정도이며,[23] 입력 임피던스(~2−6 MΩ)와 출력 임피던스(~50 Ω)의 비인 전류 이득은 추가적인 (전력) 이득을 제공한다.

차동 이득이 크고 입력 전류가 작은 연산 증폭기에서 음의 귀환 회로를 형성한 경우, 그 회로의 전달 함수는 연산 증폭기의 이득과 관계없이 주변 소자 상수로 결정되며, 그때 연산 증폭기는 입력 전압 차이가 0이 되도록(일반적으로 가상 단락[35]이라고 불림) 출력 전압(또는 출력 전류)을 조정하도록 동작한다.

4. 연산 증폭기의 이상적인 특성과 실제 특성

특성 기호 값 비고 차동 이득 Ad 무한대 동상 이득 Ac 0 동상 신호 제거율 CMRR 무한대 입력 임피던스 Zin 무한대 입력원의 전위에 영향을 주지 않는다. 출력 임피던스 Zout 0 연산 증폭기 뒤에 어떤 것을 연결하더라도 연산 증폭기는 동작한다. 주파수 대역폭 f 무한대 어떤 주파수에서도 일정한 비율로 증폭하는 것. 내부 잡음 0

실제로는 이상적인 특성은 실현할 수 없고, 예를 들어 다음과 같은 값이 된다.

이 외에도, 연산 증폭기가 동작하기 위해 인가하는 전원 전압을 넘는 입출력 전압은 처리할 수 없다.[34], 입력 전압의 오프셋이 있으며, 온도에 따라 변화하는 등의 제약이 있다.

그러나 이러한 값을 실현할 수 있다면, 이상적인 값과의 차이를 고려하면서 필요한 목적을 얻도록 회로를 설계하는 것이 가능하다.

연산 증폭기 IC는 입출력 기능이나, 필요로 하는 전원, 핀 배치 등의 패키징을 표준화한 것이 많으므로, 설계 작업의 효율화에 도움이 된다. 또한 연산 증폭기 IC는 여러 개의 연산 증폭기 회로를 내장한 것도 널리 보급되어 있다.

4. 1. 이상적인 연산 증폭기

이상 연산 증폭기는 가장 이상적으로 동작하는 증폭기이다. 증폭기 설계에서 이상적인 특성을 설정하고, 실제 제품을 만들 때 이 특성에 가깝게 만드는 것이 목표이다.[6][7][8]

이상적인 연산 증폭기는 다음과 같은 특성을 갖는다:

| 요소 | 영어 용어 | 값 |

|---|---|---|

| 되먹임없는 열린 이득 | open-loop gain | ∞ |

| 대역폭 | bandwidth | ∞ |

| 위상 | phase shift | 0 |

| 슬루율 | slew rate | ∞ |

| 입력 임피던스 입력 전류 입력 오프셋 전압 | input impedance input current input offset voltage | ∞ 0 0 |

| 출력 임피던스 | output impedance | 0 |

| 노이즈 | electronic noise | 0 |

| 공통 모드 제거비 | CMRR(Common-Mode Rejection Ratio) | ∞ |

| 전원 전압 제거비 | power supply rejection ratio | ∞ |

이러한 이상적인 특성은 다음 두 가지 "황금률"로 요약할 수 있다.[9]

# 폐루프에서 출력은 입력 간의 전압 차이를 0으로 만들기 위해 필요한 모든 동작을 수행한다.

# 입력은 전류를 소모하지 않는다.[9]

첫 번째 규칙은 연산 증폭기가 폐루프 설계(출력에서 반전 입력으로 되돌아가는 일종의 신호 경로가 있는 음의 피드백)로 사용되는 경우에만 적용된다. 이러한 규칙은 일반적으로 연산 증폭기 회로를 분석하거나 설계하기 위한 좋은 근사치로 사용된다.[9]

이러한 이상적 특성을 바탕으로, 연산 증폭기 회로 해석에 중요한 다음 두 가지 특징을 정의한다.

- 과 사이의 전압은 0으로 같다. (=0) : 열린 이득 G=∞.

- 에 들어가는 전류는 0이다 : 입력 임피던스 Rin=∞.

위의 두 조건은 종종 가상 접지(virtual-ground)라고 한다.

회로 이론상 “이상적인 연산 증폭기(ideal op-amp)”는 다음과 같은 특성을 갖는다고 가정한다.

| 특성 | 기호 | 값 | 비고 |

|---|---|---|---|

| 차동 이득 | Ad | 무한대 | |

| 동상 이득 | Ac | 0 | |

| 동상 신호 제거율 | CMRR | 무한대 | |

| 입력 임피던스 | Zin | 무한대 | 입력원의 전위에 영향을 주지 않는다. |

| 출력 임피던스 | Zout | 0 | 연산 증폭기 뒤에 어떤 것을 연결하더라도 연산 증폭기는 동작한다. |

| 주파수 대역폭 | f | 무한대 | 어떤 주파수에서도 일정한 비율로 증폭하는 것. |

| 내부 잡음 | 0 |

하지만 실제로는 이상적인 특성을 실현할 수 없다.[34] 예를 들어, 연산 증폭기가 동작하기 위해 인가하는 전원 전압을 넘는 입출력 전압은 처리할 수 없으며, 입력 전압의 오프셋, 온도에 따른 변화 등 여러 제약이 존재한다.

4. 2. 실제 연산 증폭기

실제 연산 증폭기는 이상적인 연산 증폭기의 특성에서 벗어나는 여러 제약 조건을 가진다.- 유한한 개루프 이득: 실제 연산 증폭기의 개루프 이득은 유한하다. 일반적인 소자는 100,000을 초과하는 개루프 DC 이득을 가지지만, 루프 이득이 매우 커야 폐루프 이득이 음의 귀환에 의해서만 결정된다. 폐루프 이득이 매우 높아야 하는 응용에서는 귀환 이득이 매우 낮아져 회로의 비이상적인 동작이 발생할 수 있다.

- 0이 아닌 출력 임피던스: 낮은 출력 임피던스는 저임피던스 부하에 중요하며, 출력 임피던스에 걸리는 전압 강하는 개루프 이득을 감소시킨다. 전압 감지 음의 귀환이 있는 구성에서는 출력 임피던스가 효과적으로 낮아진다. 저임피던스 출력에는 일반적으로 높은 정지 전류가 필요하여 더 많은 전력을 소비하므로, 저전력 설계에서는 의도적으로 낮은 출력 임피던스를 희생할 수 있다.

- 유한한 입력 임피던스: 연산 증폭기의 ''차동 입력 임피던스''는 두 입력 ''사이''의 임피던스이고, ''공통 모드 입력 임피던스''는 각 입력에서 접지까지의 임피던스이다. MOSFET 입력 연산 증폭기는 보호 회로를 가질 수 있지만, 일반적인 고이득 음의 귀환 응용에서는 비활성 상태가 된다.

- 입력 커패시턴스: 기생 커패시턴스로 인한 추가 입력 임피던스는 고주파 동작에서 입력 임피던스를 낮추고 위상 이동을 일으킬 수 있다.

- 입력 전류: 바이어싱 또는 누설로 인해 소량의 전류[10]가 입력으로 흐른다. 이 전류는 전압 강하를 생성할 수 있으며, 입력 전류가 일치하고 ''두'' 입력 모두에서 ''바라보는'' 임피던스가 일치하는 경우 각 입력의 전압은 같다. 입력 전류의 불일치는 입력 오프셋 전류를 생성하여 오프셋 전압을 유발할 수 있다.

- 입력 오프셋 전압: 입력 오프셋 전압은 출력 전압을 0으로 만드는 데 필요한 입력 단자 전압이다.[11][12] 완벽한 증폭기에는 입력 오프셋 전압이 없지만, 차동 증폭기 입력 단계의 불완전성으로 인해 발생한다. 입력 오프셋 전압은 증폭기 출력 포화나 신호 증폭 시 문제를 야기할 수 있다.[13]

- 공통 모드 이득: 완벽한 연산 증폭기는 전압 차이만 증폭하고 공통 전압은 제거하지만, 실제로는 공통 모드 제거 비율(CMRR)이 유한하여 공통 전압이 어느 정도 증폭된다.

- 전원 공급 장치 제거: 실제 연산 증폭기는 유한한 전원 공급 장치 제거 비율(PSRR)을 가지므로, 전원 공급 장치의 노이즈가 출력으로 전파될 수 있다.

- 온도 효과: 증폭기의 성능과 특성은 온도 변화에 따라 변하며, 특히 입력 오프셋 전압의 온도 드리프트가 중요하다.

- 드리프트: 실제 연산 증폭기 매개변수는 시간, 온도, 입력 조건 등에 따라 느리게 변한다.

- 유한한 대역폭: 모든 증폭기는 유한한 대역폭을 가지며, 연산 증폭기는 이득-대역폭 곱(GBWP)으로 특징지어진다. 유한한 대역폭은 안정성 문제와 왜곡을 유발할 수 있다. 일반적인 저가형 연산 증폭기는 몇 메가헤르츠의 GBWP를 가지며, 특수 고속 연산 증폭기는 수백 메가헤르츠의 GBWP를 달성할 수 있다.

- 잡음: 증폭기는 신호가 없어도 내부 열 잡음과 플리커 잡음으로 인해 잡음을 출력한다.

- 포화: 출력 전압은 전원 공급 장치 전압에 가까운 최소값과 최대값으로 제한된다.[14] ''' 연산 증폭기'''는 낮은 출력 전류를 제공할 때 전원 레일에서 밀리볼트 이내에 도달할 수 있다.[17]

- 슬루율 제한: 증폭기의 출력 전압은 슬루율에 도달하며, 이는 입력 신호 증가에 따른 출력 변화율에 영향을 미치지 않는다. 슬루율 제한은 입력 단 포화로 인해 발생하며, 정전용량을 구동하는 일정한 전류에 의해 제한된다.

- 비선형 입력-출력 관계: 출력 전압이 입력 전압 차이에 정확하게 비례하지 않아 왜곡이 발생할 수 있지만, 음의 피드백 사용 시에는 매우 작다.

- 위상 반전: 일부 집적 연산 증폭기에서 공통 모드 전압 위반 시 출력이 반대 극성으로 슬루될 수 있다.[15][16]

- 제한된 출력 전류: 출력 전류는 유한하며, 대부분의 연산 증폭기는 소자 손상을 방지하기 위해 출력 전류를 제한한다.

- 제한된 출력 전압: 출력 전압은 연산 증폭기에 공급되는 전원 전압을 초과할 수 없다.

- 출력 싱크 전류: 출력 싱크 전류는 출력 단계로 흘러들어갈 수 있는 최대 전류이다.

- 제한된 소비 전력: 출력 전류는 내부 출력 임피던스를 통해 흐르며 열을 발생시키므로, 과도한 전력 소비는 연산 증폭기를 손상시킬 수 있다.

최신 집적 FET 또는 MOSFET 연산 증폭기는 바이폴라 IC보다 이상적인 연산 증폭기에 더 가깝지만, 바이폴라는 입력 전압 오프셋이 더 우수하고 잡음이 낮은 경우가 많다.

이상적인 연산 증폭기는 무한대의 공통 모드 제거율 또는 0의 공통 모드 이득을 갖는다.

일반적인 741 연산 증폭기의 경우, 공통 모드 제거율은 90 dB[23]이며, 이는 개방 루프 공통 모드 전압 이득이 약 6임을 의미한다.

5. 연산 증폭기의 회로 구성 및 응용

5. 1. 기본 회로 구성

연산 증폭기는 주로 음의 피드백과 함께 사용되어 안정적인 동작을 확보한다.[5] 음의 피드백을 사용하면 회로의 전체 이득과 응답은 연산 증폭기 특성이 아닌 피드백 네트워크에 의해 주로 결정된다.[5] 연산 증폭기 회로의 입력에 대한 응답은 전달 함수에 의해 수학적으로 특징지어진다.[5]thumb

::

::

- '''전압 팔로워 (버퍼):''' 이득이 1인 비반전 증폭기로, 높은 입력 임피던스와 낮은 출력 임피던스를 제공하여 신호 손실 없이 신호를 전달하는 데 사용된다.

- '''가산 증폭기:''' 여러 입력 신호를 합산하여 출력한다.[38]

thumb

::

thumb

::

- '''미분기:''' 입력 신호의 미분 값을 출력한다.

::

::

5. 2. 응용 분야

연산 증폭기는 다양한 전자 회로에서 핵심적인 역할을 수행하는 블록이다. 개별 부품으로 구성하는 대신 연산 증폭기를 사용하면 회로 설계가 간편해지고, 이상적인 차동 이득 블록처럼 동작하는 특성을 활용할 수 있다. 회로 설계 시뮬레이션을 통해 기본 회로를 설계하고, 요구 사양에 맞는 연산 증폭기와 부품을 선택한다. 프로토타입 제작 및 테스트를 통해 설계를 개선하며, 필요한 경우 사양을 수정한다.연산 증폭기는 개별 회로 요소(트랜지스터, 저항 등)를 모두 지정하는 것보다 훨씬 쉽고 명확하게 회로를 구성할 수 있도록 한다.

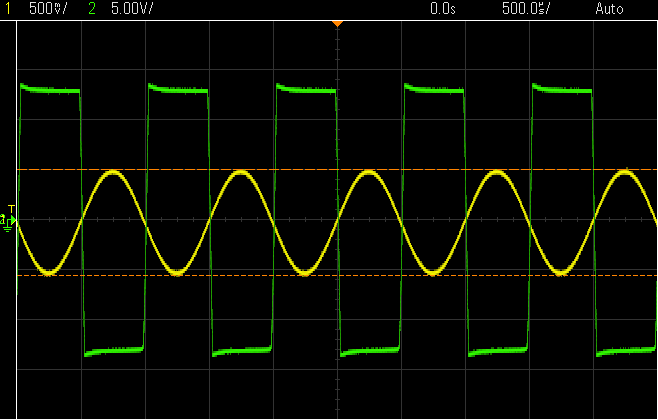

연산 증폭기는 피드백 없이 전압 비교기로 사용될 수 있지만, 속도가 중요하거나 넓은 범위의 입력 전압이 예상되는 경우에는 비교기로 주로 설계된 장치가 더 나은 성능을 보일 수 있다. 전압 레벨 검출기는 기준 전압과 입력 전압을 비교하여 양의 전압을 검출하는 비교기로 동작한다. 영전압 레벨 검출기는 함수 발생기의 사인파 출력을 구형파로 변환하거나, 트라이액을 최적 시점에 트리거하여 주전원 간섭을 줄이는 데 활용된다.

양의 피드백을 사용하는 슈미트 트리거는 히스테리시스를 갖는 비교기로, 연산 증폭기의 중요한 응용 분야 중 하나이다. 일부 회로에서는 삼각파 발진기나 능동 필터와 같이 양의 피드백과 음의 피드백을 모두 사용하기도 한다.

연산 증폭기 응용 분야:

- 오디오 및 비디오 주파수 전치 증폭기 및 버퍼

- 차동 증폭기

- 미분기 및 적분기

- 필터

- 정밀 정류기

- 정밀 피크 검출기

- 전압 및 전류 조정기

- 아날로그 계산기

- 아날로그-디지털 변환기

- 디지털-아날로그 변환기

- 전압 클램핑

- 발진기 및 파형 발생기

- 클리퍼

- 클램퍼 (DC 인서터 또는 복원기)

- 로그 및 역로그 증폭기

대부분의 연산 증폭기는 표준화된 DIP 핀 배치를 가지고 있어 배선 변경 없이 다른 유형으로 대체할 수 있다. 특정 목적에 맞게 개방 루프 이득, 대역폭, 잡음 성능, 입력 임피던스, 전력 소비 등을 고려하여 연산 증폭기를 선택할 수 있다.

thumb 핀 배치 741형 연산 증폭기]]

6. 연산 증폭기의 종류

연산 증폭기는 제조 공정, 입력단 트랜지스터, 용도, 위상 보상 유무, 기타 기능 등 다양한 기준에 따라 분류할 수 있다.

제조 공정에 따른 분류

- 개별형: 개별 트랜지스터 또는 진공관으로 구성된다.

- 하이브리드형: 개별 부품과 집적 회로 부품으로 구성된다.

- 완전 집적 회로형: 가장 일반적이며, 저렴한 가격으로 인해 앞의 두 가지 방식을 대체하고 있다.

집적 회로 연산 증폭기는 허용 동작 온도 범위 및 기타 환경/품질 요소에 따른 등급, DIP 및 표면 실장 부품 등의 패키지 유형에 따라서도 분류된다.

입력단 트랜지스터에 따른 분류

- 바이폴라 입력:

- 입력단이 바이폴라 트랜지스터로 구성된다.

- FET에 비해 소자 특성 편차가 적고, 입력 오프셋 전압이 작다.

- 입력 바이어스 전류가 커서 정(+)·부(-) 입력 임피던스가 불일치하면 큰 오프셋 전압이 발생할 수 있다.

- 전압성 노이즈 특성이 우수하다.

- JFET 입력:

- 입력단에 접합형 FET를 사용한다.

- 입력 임피던스가 높고, 입력 바이어스 전류가 매우 작거나 거의 흐르지 않는다.

- 정(+)·부(-) 입력 임피던스가 불일치해도 큰 오프셋 전압은 발생하지 않지만, JFET는 소자 특성 편차가 커서 절대적인 입력 오프셋 전압은 바이폴라 입력보다 크다.

- 슬루율을 비교적 높게 하기 쉽다.

- MOS 입력:

- 입력단에 MOSFET를 사용한다.

- 입력 임피던스가 매우 높고, 입력 바이어스 전류가 거의 흐르지 않아 정(+)·부(-) 입력 임피던스가 불일치해도 오프셋 전압은 거의 발생하지 않는다.

- MOSFET는 JFET 이상으로 소자 특성 편차가 커서 절대적인 입력 오프셋 전압이 열등한 경우가 많다.

- 잡음 특성이 나쁜 경우가 많지만, 새로운 제품에서는 개선되고 있다.

회로 구성 방식에 따른 분류

- 바이폴라: 모든 트랜지스터가 바이폴라 트랜지스터이거나, 입력 단이 JFET인 연산 증폭기이다. JFET만으로 구성된 연산 증폭기는 기본적으로 없으며, 출력 단에는 대부분 바이폴라 트랜지스터가 사용된다.

- CMOS: 입력부부터 출력부까지 모두 MOSFET으로 구성된 연산 증폭기이다. 소비 전력이 작고, 동작 전압이 낮은 것이 많다.

- BiMOS: 바이폴라 트랜지스터와 MOSFET을 병용하는 설계의 연산 증폭기이다. MOSFET을 pMOS와 nMOS 모두 사용하는 경우 BiCMOS가 된다. 바이폴라 트랜지스터와 MOSFET의 장점을 결합한 제품을 만들 수 있지만, 제조 비용이 증가한다.

용도별 분류

- 범용 연산 증폭기: 가격과 사용 편의성을 우선시한 사양의 제품으로, 뛰어난 특성을 갖지 않도록 함으로써 범용성을 확보하고 있다. 페어차일드 세미컨덕터(Fairchild Semiconductor)사의 μA741, 내쇼날 세미컨덕터(National Semiconductor)사의 LM301A가 그 시초이며, 이후 범용으로는 저잡음 광대역의 RC4558(레이시온(Raytheon)), FET 입력의 TL07x(텍사스 인스트루먼츠) 등이 등장했다.

- 고정밀 연산 증폭기: 밀리볼트 단위의 미세 전압(열전대) 등을 증폭하기 위한 제품이다. 절대적인 오프셋 전압 및 드리프트 특성에 뛰어난 바이폴라 입력 타입과, 차동 입력 임피던스 불균형에 의한 오프셋 전압 발생에 강한 FET 입력 타입이 있으며, 용도에 따라 선택한다. 아나로그 디바이스(Analog Devices)사의 OP07이 유명하다.

- 저잡음 연산 증폭기: 잡음을 배제해야 하는 용도에 적합한 특성을 가진다.

- 오디오 연산 증폭기: 오디오용으로 광대역·저왜율을 실현한 제품이다. 시그네틱스(Signetics)의 NE5532, 신일본무선(新日本無線)의 NJM4580, MUSES 시리즈, TI의 OPA627, OPA1612 등이 유명하다.

- 미소 전류 연산 증폭기: 전리함의 출력이나 포토다이오드의 출력, 전하 측정 등의 미소 전류를 처리하는 용도에 사용되며, 입력 전류가 fA(펨토암페어) 오더의 제품도 있다.

- 고속 연산 증폭기: 비디오 신호 증폭 등 고주파(VHF)까지 사용할 수 있는 제품으로, GB곱, 슬루율을 특별히 높였다.

- 파워 연산 증폭기: 대전력을 처리할 수 있으며, 원칙적으로 방열 처리가 필요하다.

- 저전력 연산 증폭기: 소비 전류를 매우 작게 한 제품이다.

- 레일 투 레일(Rail-To-Rail) 동작 연산 증폭기: 입력 전압과 출력 전압 모두 또는 어느 한쪽의 범위가 전원 전압까지 동작 가능하다.

- 완전 차동 연산 증폭기: 입력, 출력 모두 차동인 연산 증폭기이다.

- 디스크리트 연산 증폭기: 오디오 용도로, 모놀리식 IC의 음질이 좋지 않다고 여겨지는 경우나, 시판품에서 다른 제품과의 차별화를 위해 연산 증폭기와 유사한 회로를 디스크리트 부품을 사용하여 구성하는 경우가 있다.

위상 보상 유무에 따른 분류일부 음의 피드백 회로에서 연산 증폭기는 작은 보상 커패시터가 위상 및 주파수 응답을 수정하지 않는 한 고주파 불안정성을 겪을 수 있다. 내장 커패시터가 있는 연산 증폭기는 ''보상형''이라고 하며, 특정 폐루프 이득 이상의 회로가 외부 커패시터 없이 안정적으로 작동할 수 있게 한다. 특히, 폐루프 이득이 1인 경우에도 안정적인 연산 증폭기를 ''단일 이득 보상형''이라고 한다. 비보상 연산 증폭기는 용도에 따라 최적인 보상 커패시턴스를 외부에서 사용한다.

기타외부 저항으로 오프셋 전압을 조정하거나, 과열 시 자동 정지, 입력부 보호 다이오드 내장, 무신호 시 소비 전력 저감 기능 등 추가 기능이 포함된 연산 증폭기 IC가 다수 개발되었다.

7. 추가 정보

741 연산 증폭기는 과거 오디오 및 기타 민감한 장비에 사용되었지만, 현대적인 연산 증폭기의 향상된 잡음 성능으로 인해 이러한 용도는 드물다.[17] 741은 눈에 띄는 잡음을 발생시키는 것 외에도, 동상 제거비가 낮아 케이블을 통해 전원 험(hum) 및 스위치 ''클릭''과 같은 기타 동상 간섭을 민감한 장비에 유입시키는 경우가 많았다.[17]

'741'은 μA741, LM301, 558, LM324, TBA221 또는 TL071과 같은 보다 현대적인 대체품을 포함하여 일반적인 연산 증폭기 집적회로를 의미하게 되었다.[17] 741 출력 단계에 대한 설명은 많은 다른 설계에도 질적으로 유사하지만, 다음과 같은 예외가 있다.[17]

참조

[1]

문서

IC power supply pins

[2]

웹사이트

Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs

http://www.maxim-ic.[...]

2007-11-10

[3]

웹사이트

Apex OP PA98

https://web.archive.[...]

2015-11-08

[4]

논문

Application Note AN-849: Using Op Amps as Comparators

https://www.analog.c[...]

2011

[5]

서적

Microelectronics: Digital and Analog Circuits and Systems

https://archive.org/[...]

McGraw-Hill

1979

[6]

웹사이트

Understanding Basic Analog – Ideal Op Amps

http://www.ti.com.cn[...]

[7]

웹사이트

Lecture 5: The ideal operational amplifier

https://web.archive.[...]

2016-12-26

[8]

서적

IC01 Ideal Operational Amplifier

https://tubetime.us/[...]

Perfect Semiconductor

2022-12-20

[9]

서적

The Art of Electronics

https://books.google[...]

Cambridge University Press

[10]

문서

Bipolar junction transistor, JFET, MOSFET input stages

[11]

서적

Handbook of Operational Amplifier Circuit Design

McGraw-Hill

1976

[12]

문서

Op-amp parameters with respect to the zero voltage point

[13]

문서

chopper (electronics)

[14]

문서

Output stage

[15]

웹사이트

Op Amp Output Phase-Reversal and Input Over-Voltage Protection

https://web.archive.[...]

Analog Devices

2012-12-27

[16]

웹사이트

Bootstrapping your op amp yields wide voltage swings

http://www.edn.com/c[...]

Electronic Design News

2012-12-27

[17]

웹사이트

Application of Rail-to-Rail Operational Amplifiers

https://www.ti.com/l[...]

Texas Instruments

2021-06-08

[18]

웹사이트

IC Op-Amps Through the Ages

https://web.archive.[...]

Stanford University

2011-07-05

[19]

웹사이트

Electronics 2, Chapter 10

https://web.archive.[...]

National Taiwan University, Graduate Institute of Electronics Engineering

2014-02-22

[20]

웹사이트

Understanding silicon circuits: inside the ubiquitous 741 op amp

http://www.righto.co[...]

2018-04-28

[21]

문서

μA702 and μA709

[22]

문서

Input bias current

[23]

문서

National Semiconductor LM741 data sheet

[24]

웹사이트

The μA741 Operational Amplifier

http://ecow.engr.wis[...]

2016-06

[25]

문서

Input bias current and offset voltage

[26]

웹사이트

Op Amp Input Bias Current

https://web.archive.[...]

Analog Devices

2014-05-15

[27]

서적

Op Amp Applications Handbook

https://books.google[...]

Newnes

2008-11-15

[28]

논문

Analysis of Problems in Dynamics by Electronic Circuits

IEEE

1947-05

[29]

웹사이트

Op Amp Applications

https://web.archive.[...]

Analog Devices

2012-12-27

[30]

웹사이트

The Philbrick Archive

http://www.philbrick[...]

2018-04-28

[31]

웹사이트

The all-new, all solid-state Philbrick P2 amplifier

http://www.philbrick[...]

2011-05-11

[32]

서적

Electronic Principles

https://archive.org/[...]

McGraw-Hill

1979

[33]

문서

pp.11

[34]

문서

pp.14

[35]

문서

「イマジナリ(ル)ショート」は和製造語

[36]

서적

[37]

서적

[38]

서적

[39]

문서

특정 용도 오퍼앰프의 비추천 용도 사용 시 문제점

[40]

문서

OP로 시작하는 오퍼앰프의 기원

[41]

문서

모토로라 상표 및 "풀스윙" 표현

[42]

웹사이트

MAXIM Application Note 1108: Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs

http://www.maxim-ic.[...]

2007-11-10

[43]

웹인용

Analog devices MT-044 TUTORIAL

http://www.analog.co[...]

2010-10-28

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com