WDC 65816

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

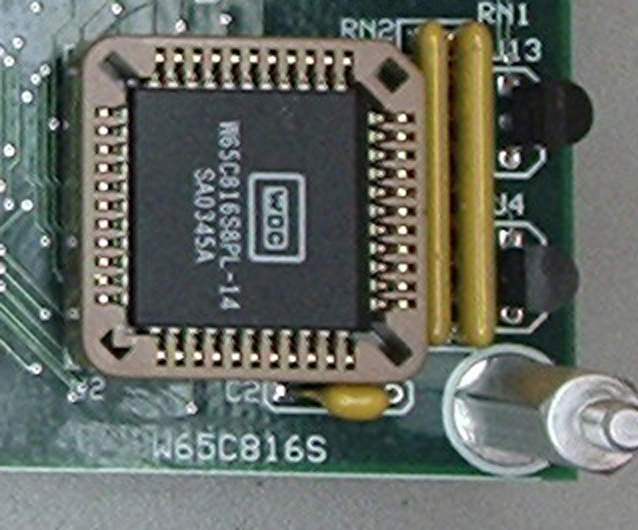

WDC 65816은 1980년대에 웨스턴 디자인 센터(WDC)에서 개발한 16비트 마이크로프로세서이다. 6502 프로세서와 호환성을 유지하면서 16비트 연산, 24비트 주소 지정, 뱅크 레지스터 등을 지원하며, 애플 IIGS, 슈퍼 패미컴 등 다양한 기기에 사용되었다. 정적 CMOS 설계를 통해 전력 소비를 줄였으며, 6502와의 호환성을 위해 에뮬레이션 모드를 제공한다.

더 읽어볼만한 페이지

- 65xx 마이크로프로세서 - 리코 5A22

리코 5A22는 65C816 코어를 기반으로 슈퍼 패미컴에 사용된 프로세서로, 컨트롤러 포트 인터페이스, 인터럽트 생성 회로, DMA 기능, 곱셈 및 나눗셈 연산을 위한 레지스터 등을 포함하며, 두 개의 개별 주소 버스로 제어되는 8비트 데이터 버스를 특징으로 한다. - 65xx 마이크로프로세서 - WDC 65C02

WDC 65C02는 6502의 저전력 CMOS 버전으로, 버그 수정, 명령어 추가, 성능 개선이 이루어진 8비트 마이크로프로세서이다. - 16비트 마이크로프로세서 - 인텔 8086

인텔 8086은 1978년 인텔에서 개발한 16비트 마이크로프로세서로, 8비트 프로세서인 인텔 8080을 확장하여 20비트 어드레스 버스를 통해 1MB의 메모리 공간을 지원하며 IBM PC에 채택되어 x86 아키텍처의 상업적 성공을 이끌었다. - 16비트 마이크로프로세서 - 인텔 80286

인텔 80286은 1984년에 출시된 16비트 x86 마이크로프로세서로, 8086과 호환되며 16MB의 물리 메모리와 1GB의 가상 메모리를 지원하고 보호 모드를 통해 멀티태스킹을 가능하게 했다.

| WDC 65816 | |

|---|---|

| 기본 정보 | |

| |

| 명칭 | WDC 65C816 |

| 생산 시작 | 1985년 |

| 아키텍처 | 6502 |

| 데이터 버스 폭 | 8비트 (외부) 16비트 (내부) |

| 주소 버스 폭 | 24비트 |

| 명령어 집합 | 92 |

| 패키지 | 40핀 DIP 44핀 PLCC, 기타 |

| 파생 버전 | W65C802 (W65C02와 핀 호환) W65C265 (MCU) |

| 이전 모델 | MOS 6502 WDC 65C02 |

| 다음 모델 | WDC 65C832 (미출시) |

| 생산자 | 웨스턴디자인센터, 기타 |

| 최고 속도 | 14MHz |

| 최저 속도 | 1MHz |

2. 역사

1981년, WDC의 창립자이자 CEO인 빌 멘쉬는 록웰 반도체 및 시너테크 등의 파트너와 함께 6502의 CMOS 버전인 65C02 개발을 시작했다. 65C02의 주요 목표는 기존 6502의 NMOS 공정을 CMOS 공정으로 전환하여 전력 소비를 줄이는 것이었다. 이를 통해 클럭 속도와 관계없이 소비 전력을 에서 로 억제할 수 있었다. 또한 최대 지원 클럭 속도를 높이는 것과, NMOS 6502에 존재했던 오류를 해결하고 새로운 명령어 및 어드레싱 모드를 도입하는 것도 목표였다.[4]

1982년, 멘쉬는 애플과 협의하여 그래픽 및 음향 기능이 개선된 애플 II 시리즈의 새로운 버전을 위해 W65C816S 개발을 시작했다. 애플은 애플 II에서 사용되던 6502와 소프트웨어 호환이 되면서 더 많은 메모리에 접근하고 16비트 데이터 워드를 로드 및 저장할 수 있는 MPU를 원했다. 1984년 3월, 65C816이 완성되었고, 그 해 후반에 샘플이 애플과 아타리에 제공되었으며, 1985년에 정식 출시되었다.[4] 멘쉬는 설계 과정에서 여동생 캐서린의 도움을 받았으며, 캐서린은 장치 레이아웃 일부를 담당했다.

같은 공정으로 65C802도 개발되었다. 65C802는 65C816과 내부적으로 동일하며, 둘 다 같은 제조 라인에서 생산되었고, 마지막 메탈화 단계에서 외부 핀에 연결될 때의 공정만 달랐다. 65C802는 핀이 오리지널 6502와 동일한 레이아웃을 가지고 있어, 대체품으로 사용할 수 있으면서도 CPU의 16비트 처리를 활용할 수 있었다. 그러나 오리지널 핀 배치를 사용했기 때문에 16개의 어드레스 핀만 가지고 있어, 외부 메모리는 64KB만 접근할 수 있었다.[4] 일반적으로 하드웨어 제조업체는 처음부터 프로젝트를 설계할 때 65C816을 사용했기 때문에 65C802는 생산이 중단되었다.

애플은 이후 65C816을 애플 IIGS 컴퓨터에 채택했다. 65C816의 기본 설계는 1980년대 중반부터 1990년대 초반까지 VLSI 테크놀로지,[14] GTE, 산요 전기 등에 의해 세컨드 소스로 공급되었다.

1990년대에는 65C816과 65C02가 모두 완전한 스태틱 코어로 변환되어, 프로세서의 Ø2 클럭을 완전히 정지시켜도 레지스터 내용을 잃지 않게 되었다. 이 기능과 SRAM의 사용으로, 대기 상태에서 최소한의 전력을 사용하는 설계를 가능하게 했다.

현재, W65C816S는 WDC에서 40핀 PDIP, PLCC44 또는 44핀 TQFP 패키지로 구할 수 있으며, W65C265를 통해 MCU로,[15] 그리고 ASIC 통합을 위한 IP 코어로 제공되고 있다.[16][17]

3. 특징

MVN, MVP 명령어)을 통해 메모리 블록을 빠르게 복사할 수 있다.WDM) 명령어를 제공한다. (WDM은 W65C816S 설계자 윌리엄 D. 멘쉬의 약자이다.)

65C816은 16비트 직접 페이지 레지스터(DP)를 통해 뱅크 $00 내에서 직접 페이지(제로 페이지) 위치를 변경할 수 있다. 65(c)02에서 직접 페이지는 항상 메모리의 처음 256바이트에 고정되어 있지만, 65C816은 이를 뱅크 $00 내의 임의의 위치로 재배치할 수 있다. 단, DP가 페이지 경계($xx00)로 설정되지 않으면 1 사이클의 접근 페널티가 발생한다.[13]

24비트 주소는 8비트 데이터 뱅크 레지스터(DB)와 프로그램 뱅크 레지스터(PB)를 통해 생성된다. 이 레지스터들은 주소의 비트 16-23을 설정하여 64KB의 연속된 메모리 세그먼트($xx0000-$xxFFFF)를 뱅크 주소 xx로 정의한다. 두 레지스터는 전원 투입 또는 리셋 시 $00으로 초기화된다.[8]

명령어 및 피연산자 페치 사이클에서 PB는 프로그램 카운터(PC)에 앞에 붙어 24비트 유효 주소를 형성한다. PC가 오버플로되어 0으로 돌아가도 PB는 증가하지 않으므로, 프로그램은 실행 중인 뱅크 범위 내로 제한된다. 뱅크 간 점프나 서브루틴 호출은 "롱" 점프나 서브루틴 호출을 사용해야 하며, 프로그램에서 직접 PB를 변경할 수 없다.[9]

데이터 페치 및 저장 사이클에서 DB는 16비트 데이터 주소에 앞에 붙어 24비트 유효 주소를 형성한다. 이로 인해 16비트 주소를 사용하는 6502 또는 65C02 코드가 정상 작동한다. PB와 달리 DB는 프로그램 제어로 변경 가능하며, 16비트 주소 지정 범위를 초과하는 데이터에 접근하는 데 사용된다. 또한 인덱스된 주소가 현재 DB의 뱅크 범위를 초과하면 DB가 일시적으로 증가한다.[10]

4. 레지스터

WDC 65816 프로세서의 주요 레지스터는 다음과 같다.

| 레지스터 | 설명 |

|---|---|

| 누산기 (A, B, C) | 8비트 또는 16비트 누산기로 사용된다. 16비트일 때는 C로 표시된다. |

| 인덱스 레지스터 (X, Y) | 8비트 또는 16비트 인덱스 레지스터로 사용된다. |

| 직접 페이지 레지스터 (DP) | 16비트 직접 페이지 레지스터. 65(C)02의 영 페이지를 뱅크 `$00`(메모리의 처음 64KB) 내의 어디든지 재배치할 수 있게 해준다. |

| 스택 포인터 (SP) | 16비트 스택 포인터. |

| 데이터 뱅크 레지스터 (DB) | 8비트 데이터 뱅크 레지스터. 16비트 데이터 주소 앞에 붙어 24비트 유효 주소를 형성한다. |

| 프로그램 뱅크 레지스터 (PB) | 8비트 프로그램 뱅크 레지스터. 프로그램 카운터(PC) 앞에 붙어 24비트 유효 주소를 형성한다. |

| 프로그램 카운터 (PC) | 16비트 프로그램 카운터. |

| 상태 레지스터 (P) | 프로세서의 상태를 나타내는 플래그들을 포함한다. |

누산기와 인덱스 레지스터는 네이티브 모드에서 8비트 또는 16비트로 설정될 수 있다. 상태 레지스터의 'm' 비트가 누산기의 크기를, 'x' 비트가 인덱스 레지스터의 크기를 제어한다. 이 비트들이 0이면 16비트, 1이면 8비트 크기로 설정된다.

5. 동작 모드

WDC 65816은 "에뮬레이션 모드"와 "네이티브 모드" 두 가지 동작 모드를 가진다. 에뮬레이션 모드에서는 16비트 연산이 비활성화되고 인덱스 레지스터가 8비트로 제한되어 6502와 매우 유사하게 동작하며, 연산 코드에 대한 사이클 타이밍도 동일하다. 네이티브 모드에서는 65C816의 모든 기능을 사용할 수 있다. CPU는 전원이 켜지거나 재설정될 때 자동으로 에뮬레이션 모드로 진입하며, 이는 핀 배열이 다른 경우 회로 변경을 통해 65(C)02를 대체할 수 있게 해준다.

네이티브 모드에서는 누산기(A), X 및 Y 인덱스 레지스터, 스택 포인터(SP)가 8비트에서 16비트 크기로 확장된다. 프로그램 카운터(PC)는 항상 16비트이므로 영향을 받지 않는다.

6502에서 사용되지 않던 상태 레지스터의 4, 5번 비트는 네이티브 모드에서 각각 x 플래그와 m 플래그로 의미가 변경된다. 이 플래그들은 인덱스 레지스터(x)와 누산기/메모리(m)의 크기(8비트 또는 16비트)를 제어한다. 0이면 16비트, 1이면 8비트로 설정된다. 이 비트들은 프로세서 전원 투입 또는 리셋 시 1로 고정되지만, 네이티브 모드로 전환된 후에는 변경할 수 있다.

`REP` 및 `SEP` 명령으로 m 및 x 상태 레지스터 비트를 조작하여 누산기와 인덱스 레지스터를 16비트 또는 8비트 크기로 설정할 수 있다. 이를 통해 워드 및 바이트 크기 데이터에 대한 연산이 가능하다. 누산기와 인덱스 레지스터 크기는 독립적으로 설정 가능하므로, 예를 들어 누산기를 8비트, 인덱스 레지스터를 16비트로 설정하여 포인터 연산 없이 64KB 범위에서 개별 바이트를 조작할 수 있다.

레지스터가 16비트로 설정되면 메모리 접근은 클록 사이클당 1바이트씩 두 개의 연속된 바이트를 읽거나 쓴다. 따라서 누산기가 16비트일 때 `ROR

5. 1. 모드 전환

WDC 65816 프로세서는 "에뮬레이션 모드"와 "네이티브 모드" 두 가지 작동 모드를 가진다. 전원을 켜거나 재설정하면 자동으로 에뮬레이션 모드로 시작하며, 이 모드에서는 6502 프로세서와 매우 유사하게 작동한다.

`XCE` (e'''X'''change '''C'''arry with '''E'''mulation) 명령어는 에뮬레이션 비트(e)와 캐리 비트(c)를 교환한다. 캐리 비트는 상태 레지스터(SR)의 비트 0에 해당한다. 이 명령어로 에뮬레이션 모드와 네이티브 모드를 전환할 수 있다. 네이티브 모드로 들어가려면, `CLC` 명령어로 캐리 비트를 0으로 만들고, `XCE` 명령어를 실행한다. 에뮬레이션 모드로 돌아가려면 `SEC` 명령어로 캐리 비트를 1로 설정하고, `XCE` 명령어를 실행한다.

네이티브 모드에서는 상태 레지스터의 `m`과 `x` 비트로 레지스터 크기를 조절한다. `SEP` 명령어는 해당 비트를 1로 설정하고, `REP` 명령어는 0으로 해제한다. `m` 비트가 0이면 누산기(accumulator)가 16비트, 1이면 8비트가 된다. `x` 비트가 0이면 인덱스 레지스터(X, Y)가 16비트, 1이면 8비트가 된다.

6. 65802

'''WDC 65802'''('''65C802''')는 6502와 핀 호환이 완벽하게 되는 65816 CPU로, 1980년대 중후반부터 1990년대 초까지 WDC와 GTE에서 생산되었다.

이 칩은 8비트 6502/65C02에서 16비트 65816으로 업그레이드하기 위한 목적으로 설계되었다. 65802는 65816의 24비트 주소 버스를 6502/65C02와 동일한 16비트(64KB 메모리)로 축소하였다. 65816의 모든 뱅크 선택 레지스터는 65802 코어에 남아있지만, 동작 시에는 작동하지 않는다. 일반적으로 하드웨어 제작자들은 설계 시 더 강력한 65816을 사용한다.

7. 사용 기기

- 아콘 커뮤니케이터 (2MHz)

- 애플 IIGS (2.8MHz)

- 6502 호환이라는 점 때문에 애플 II GS의 CPU로 채용되었다.

- 슈퍼 패미컴 (65816 호환 리코 5A22, 3.58MHz)

- 패밀리 컴퓨터의 CPU인 6502의 상위 호환이기 때문에 슈퍼 패미컴에도 탑재되었다. 슈퍼 패미컴 자체는 공식적으로 패밀리 컴퓨터와 호환되지 않지만, 상위 호환성을 갖도록 설계되었다.

- 일부 슈퍼 패미컴용 게임은 65816 상위 호환인 닌텐도 SA-1을 탑재했다.

- 코모도어 64용 확장 장치 (C-One, SuperCPU)

- Foenix Retro Systems C256 U/U+, F256K 모델[9][10]

8. 비판 (보수 진영 관점)

(빈 섹션 - 원본 소스에 내용 없음)

참조

[1]

웹사이트

A Report on the 65c832

https://mirrors.appl[...]

2024-04-07

[2]

웹사이트

W65C832 Information, Specification, and Data Sheet (March 1990)

https://downloads.re[...]

2024-04-07

[3]

웹사이트

W65C832 Information, Specification, and Data Sheet

http://6502.org/docu[...]

2024-04-07

[4]

서적

Application Specific Logic Products Data Book 1988

https://archive.org/[...]

VLSI Technology Inc.

1988-01-01

[5]

웹사이트

W65C265S 16-bit Microcontroller

https://www.westernd[...]

2024-04-07

[6]

웹사이트

W65C816 8/16-bit Microprocessor

https://www.westernd[...]

2024-04-07

[7]

웹사이트

W65C265S 8/16-bit Microcontroller

https://www.westernd[...]

2024-04-07

[8]

웹사이트

W55V92 TV-toy Controller Data Sheet

https://static6.arro[...]

2024-06-12

[9]

웹사이트

16bits CPU – New Retro Computers

https://c256foenix.c[...]

2024-12-24

[10]

웹사이트

F256K

https://c256foenix.c[...]

2024-12-24

[11]

웹사이트

A Report on the 65c832

https://mirrors.appl[...]

2024-04-07

[12]

웹사이트

W65C832 Information, Specification, and Data Sheet (March 1990)

https://downloads.re[...]

2024-04-07

[13]

웹사이트

W65C832 Information, Specification, and Data Sheet

http://6502.org/docu[...]

2024-04-07

[14]

서적

Application Specific Logic Products Data Book 1988

https://archive.org/[...]

VLSI Technology Inc.

1988-01-01

[15]

웹사이트

W65C265S 16-bit Microcontroller

https://www.westernd[...]

2024-04-07

[16]

웹사이트

W65C816 8/16-bit Microprocessor

https://www.westernd[...]

2024-04-07

[17]

웹사이트

W65C265S 8/16-bit Microcontroller

https://www.westernd[...]

2024-04-07

[18]

웹사이트

W55V92 TV-toy Controller Data Sheet

https://static6.arro[...]

2024-06-12

[19]

웹사이트

16bits CPU – New Retro Computers

https://c256foenix.c[...]

2024-12-24

[20]

웹사이트

F256K

https://c256foenix.c[...]

2024-12-24

[21]

웹인용

A Report on the 65c832

https://mirrors.appl[...]

2024-04-07

[22]

웹인용

W65C832 Information, Specification, and Data Sheet (March 1990)

https://downloads.re[...]

2024-04-07

[23]

웹인용

W65C832 Information, Specification, and Data Sheet

http://6502.org/docu[...]

2024-04-07

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com