NMOS 논리

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

NMOS 논리는 n형 강화형 MOSFET을 사용하여 논리 게이트 및 디지털 회로를 구현하는 기술이다. NMOS 트랜지스터는 게이트에 전압을 가하여 N 채널을 생성하여 작동하며, 차단, 트라이오드, 포화, 속도 포화의 네 가지 동작 모드를 가진다. NMOS 논리는 풀다운 네트워크로 배열된 트랜지스터와 풀업 저항을 사용하여 논리 게이트를 구성하며, NOR 게이트와 같은 논리 회로 구현에 활용된다. NMOS 회로는 Low에서 High로의 전환 속도가 느리다는 단점이 있으며, 고갈형 트랜지스터를 부하로 사용하여 속도를 개선할 수 있다. NMOS 기술은 초기 마이크로프로세서, 메모리, 디지털 회로에 사용되었으며, 한국의 반도체 산업 발전에도 영향을 미쳤다. 1970년대 후반에는 NMOS 프로세서가 PMOS 프로세서를 능가했으나, 1980년대 이후 CMOS 기술이 NMOS를 대체하면서 한국 반도체 산업은 CMOS 기술을 중심으로 발전했다.

더 읽어볼만한 페이지

- 논리 계열 - CMOS

CMOS는 상보적 금속 산화막 반도체의 약자로, 저전력 소비를 특징으로 하며, P형과 N형 MOSFET을 결합하여 논리 게이트를 구현하는 디지털 회로 설계 방식 및 공정 계열이다. - 논리 계열 - 트랜지스터-트랜지스터 논리

트랜지스터-트랜지스터 논리(TTL)는 1961년 제임스 L. 부이에 의해 발명된 바이폴라 접합 트랜지스터 기반의 디지털 회로 기술로, 텍사스 인스트루먼츠의 7400 시리즈를 통해 널리 사용되었으며, 저렴한 비용으로 디지털 기술 발전에 기여했다. - MOSFET - CMOS

CMOS는 상보적 금속 산화막 반도체의 약자로, 저전력 소비를 특징으로 하며, P형과 N형 MOSFET을 결합하여 논리 게이트를 구현하는 디지털 회로 설계 방식 및 공정 계열이다. - MOSFET - 전자 이동도

전자 이동도는 전기장 내에서 전자의 평균 이동 속도를 나타내는 물리량으로, 재료의 불순물 농도와 온도에 의존하며, 다양한 산란 메커니즘과 측정 방법을 통해 연구되고 반도체 소자 성능에 중요한 영향을 미친다. - 집적 회로 - 실시간 시계

실시간 시계(RTC)는 CPU 개입 없이 독립적으로 시간을 유지하며, 저전력 소비와 시간 민감 작업의 부담 감소, 절전 모드 유지를 위해 디지털 카운터 회로, 결정 진동자, 배터리 등으로 구성되어 PC 메인보드에 부착되거나 사우스브리지 칩 또는 마이크로컨트롤러에 내장된다. - 집적 회로 - FPGA

FPGA(Field-Programmable Gate Array)는 사용자가 하드웨어 설계를 변경할 수 있는 집적 회로이며, CPLD에서 파생되어 다양한 제조 기술을 사용하고 디지털 신호 처리, 통신 등 여러 분야에 활용된다.

| NMOS 논리 | |

|---|---|

| 기본 정보 | |

| 기술 종류 | 디지털 논리 회로 |

| 분류 | 논리 게이트 |

| 사용 | 집적 회로 |

| 상세 설명 | |

| 구성 요소 | n형 금속 산화막 반도체 전계 효과 트랜지스터 (n-channel MOSFET) 저항 |

| 작동 원리 | n-MOSFET는 게이트 전압이 특정 임계값을 넘을 때 도통 전압이 낮으면 출력은 고전압 (Vdd) 전압이 높으면 출력은 저전압 (접지) |

| 장점 | 비교적 적은 트랜지스터 사용 간단한 구조 |

| 단점 | 정적 전력 소비가 높음 (DC 전류 흐름) 출력 전압이 완전한 0이 아닐 수 있음 CMOS에 비해 전력 효율이 낮음 |

| 종류 | |

| 기본 게이트 | 인버터 (NOT 게이트) NAND 게이트 NOR 게이트 |

| 복합 게이트 | XOR 게이트 XNOR 게이트 |

| 비교 | |

| NMOS vs CMOS | CMOS는 NMOS보다 전력 효율이 훨씬 높음 CMOS는 정적 전력 소모가 거의 없음 CMOS는 더 복잡한 구조 |

| 응용 분야 | |

| 초기 집적 회로 | 초창기 마이크로프로세서 메모리 칩 디지털 논리 회로 |

| 현대 응용 | 여전히 일부 특수 응용 분야에서 사용 CMOS 논리에 통합된 형태 |

2. NMOS 논리의 구조 및 동작 원리

NMOS 논리는 n형 강화형 모드 MOSFET을 기반으로 하며, 풀다운 네트워크(PDN)와 풀업 저항(또는 부하)으로 구성된다. MOSFET는 논리 게이트 출력과 음의 전원 전압(일반적으로 접지) 사이에 "풀다운 네트워크"(PDN)로 배열된다. 풀업(저항으로 생각할 수 있는 "부하")은 양의 전원 전압과 각 논리 게이트 출력 사이에 배치된다.

집적회로 내부에 저항기를 만드는 대신 MOSFET을 저항기처럼 사용하여 공정 수를 줄일 수 있다. 이를 부하 트랜지스터 또는 부하 MOSFET이라고 한다.

NMOS 회로는 Low에서 High로 전환하는 속도가 느린데, 이는 출력과 양의 전원 레일 사이의 저항이 크기 때문이다. 더 낮은 값의 저항을 사용하면 속도가 빨라지지만 정적 전력 소비가 증가한다.

2. 1. MOSFET의 동작

N형 금속-산화물-반도체 전계 효과 트랜지스터(NMOS) 논리는 N형 MOSFET(전계 효과 트랜지스터)를 사용하여 논리 게이트 및 기타 디지털 회로를 구현한다. 이러한 NMOS 트랜지스터는 P형 트랜지스터 본체에 N 채널(반전층)을 생성하여 작동한다. 이 N 채널은 N형 "소스" 및 "드레인" 단자 사이에서 전자를 전도할 수 있게 한다. N 채널은 게이트라고 하는 세 번째 단자에 전압을 인가하여 생성된다. NMOS 트랜지스터는 차단(또는 서브스레숄드), 트라이오드, 포화(때로는 활성이라고 함), 속도 포화의 네 가지 동작 모드를 갖는다.2. 2. 논리 게이트 구현

MOSFET는 n형 강화형 모드 트랜지스터이며, 논리 게이트 출력과 음의 전원 전압(일반적으로 접지) 사이에 "풀다운 네트워크"(PDN)로 배열된다. 풀업(저항으로 생각할 수 있는 "부하")은 양의 전원 전압과 각 논리 게이트 출력 사이에 배치된다. 논리 게이트(논리적 인버터 포함)는 병렬 및/또는 직렬 회로 네트워크를 설계하여 구현할 수 있다. 특정 부울 입력 값의 조합에 대한 원하는 출력이 0(또는 거짓)인 경우 PDN이 활성화되어 음의 전원과 출력 사이에 전류 경로를 허용하는 트랜지스터가 하나 이상 존재하게 된다. 이는 부하에 전압 강하를 일으키고 따라서 출력에서 낮은 전압을 생성하여 '0'을 나타낸다.200px

예를 들어, NMOS로 구현된 NOR 게이트가 있다. 입력 A 또는 입력 B 중 하나가 높으면(논리 1, = 참), 해당 MOS 트랜지스터는 출력과 음의 전원 공급 장치 사이에서 매우 낮은 저항으로 작용하여 출력이 낮아진다(논리 0, = 거짓). A와 B가 모두 높으면 두 트랜지스터 모두 전도성이 되어 접지로 이어지는 저항 경로가 더 낮아진다. 출력이 높은 유일한 경우는 두 트랜지스터 모두 꺼져 있을 때이며, 이는 A와 B가 모두 낮을 때만 발생하므로 NOR 게이트의 진리표를 만족한다.

| A | B | A NOR B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

MOSFET는 저항으로 작동하도록 만들 수 있으므로 전체 회로를 N 채널 MOSFET만으로 만들 수 있다. NMOS 회로는 Low에서 High로 전환하는 속도가 느리다. High에서 Low로 전환할 때 트랜지스터는 낮은 저항을 제공하고 출력에서의 용량성 전하는 매우 빠르게 소진된다(매우 낮은 저항을 통해 커패시터를 방전하는 것과 유사). 그러나 출력과 양의 전원 레일 사이의 저항은 훨씬 크기 때문에 Low에서 High로의 전환이 더 오래 걸린다(높은 값의 저항을 통해 커패시터를 충전하는 것과 유사). 더 낮은 값의 저항을 사용하면 프로세스 속도가 빨라지지만 정적 전력 소비도 증가한다. 그러나 게이트 속도를 높이는 더 나은 방법(그리고 가장 일반적인 방법)은 부하로 강화형 트랜지스터 대신 고갈형 트랜지스터를 사용하는 것이다. 이를 고갈 부하 NMOS 논리라고 한다.

2. 3. 부하 MOSFET

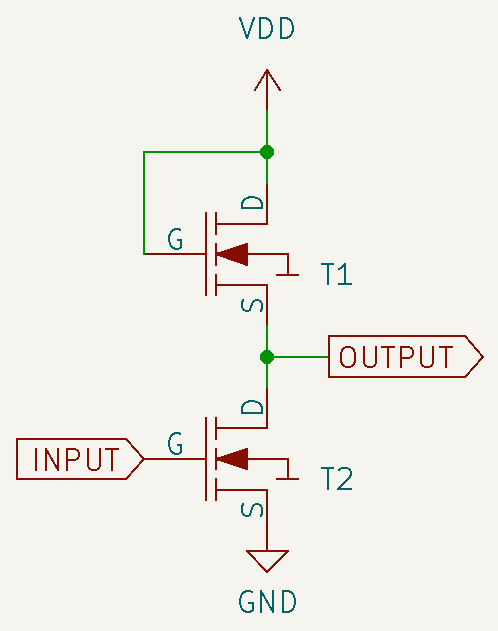

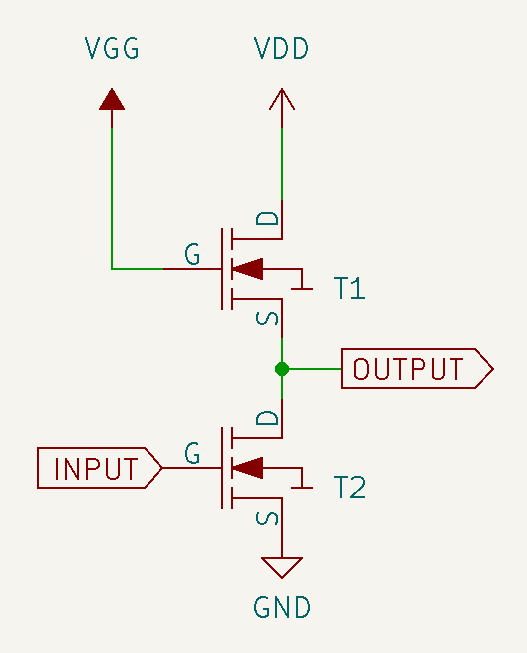

집적회로 내부에 저항기를 만들면 공정 수가 증가한다. MOSFET을 저항기 대신 사용하면 공정 수를 줄일 수 있는데, 이를 부하 트랜지스터 또는 부하 MOSFET이라고 한다. 따라서 n채널 MOSFET만으로 회로 전체를 구성할 수 있지만, 부하 MOSFET의 전기적 특성은 저항기와 다르다.부하 트랜지스터(풀업 트랜지스터)는 논리 스위치로 사용되는 것과 같은 종류의 엔핸스먼트 모드 MOSFET이다(게이트-소스 간 전압 VGS가 0이 되면 OFF됨).

부하 MOSFET의 게이트 연결 방식에 따라 부하 종류가 달라진다. 부하 MOSFET의 게이트를 Vdd에 연결하면 포화 엔핸스먼트 부하, Vgg에 연결하면 선형 엔핸스먼트 부하가 된다. 선형 엔핸스먼트 부하는 전압 강하가 적어 출력 전압을 Vdd에 가깝게 할 수 있지만, 2전원이 필요하다.

회로도에서 부하 MOSFET의 동작을 결정하는 변수는 다음과 같다.

- 드레인-소스 간 전압 VDS = Vdd - 출력 전압

- 게이트-소스 간 전압 VGS = Vdd - 출력 전압 (포화 엔핸스먼트 부하일 때)

- 게이트-소스 간 전압 VGS = Vgg - 출력 전압 (선형 엔핸스먼트 부하일 때)

- 드레인-소스 간 전류 IDS = VDS의 거의 제곱에 비례

출력 전압이 저하되면 VDS와 VGS도 증가하고, IDS는 VDS의 거의 제곱에 비례하여 증가한다. 즉, 출력 전압이 저하되면 과도한 전류가 흘러 소비 전력이 커진다. 반면 출력 전압이 증가하면 전류가 거의 흐르지 않아 동작 속도가 느려진다.

이처럼 저항기 대신 엔핸스먼트 모드 MOSFET을 사용하면 속도 및 소비 전력 면에서 문제가 발생한다. 이 문제를 개선하기 위해 엔핸스먼트 모드 트랜지스터 대신 디플리션 모드 트랜지스터를 부하로 사용할 수 있다. 이 방법을 구현한 것을 디플리션 부하 NMOS 논리라고 한다.

3. NMOS 논리의 역사

NMOS는 '금속-산화물-반도체'(metal-oxide-semiconductor)의 약자로, 1970년대 이전에 주로 사용되던 MOS 트랜지스터의 구조를 반영한다. 초기에는 게이트가 주로 알루미늄과 같은 금속으로 구성되었다. 1970년경부터 대부분의 MOS 회로는 페데리코 파긴이 페어차일드 반도체에서 처음 개발한 다결정 실리콘으로 만들어진 자기 정렬 게이트를 사용하게 되었다.

MOSFET은 1959년 벨 연구소의 Mohamed M. Atalla|모하메드 M. 아탈라영어와 한국계 기술자 강대원이 발명했다. 초기에는 PMOS 소자만이 실용적이었고, NMOS 소자는 실용적이지 않았다. 이후 페어차일드 반도체와 IBM 등 여러 회사에서 NMOS 소자 개발에 참여하였고, 1970년대 초에는 NMOS 제품이 대량 생산되기 시작했다.

1970년대 중반, 모스텍이 축소 부하 NMOS 논리를 제품화하여 속도와 소비 전력을 개선했고, 인텔은 자체적인 축소 부하 NMOS 논리에 '''HMOS'''라는 명칭을 붙였다. 1975년에 CMOS 마이크로프로세서가 발표되었으나, 초기에는 NMOS 논리보다 느려서 1970년대에는 NMOS가 컴퓨터에 더 널리 사용되었다. 그러나 1978년 히타치 제작소에서 트윈웰(twin-well) Hi-CMOS 기술을 개발하여 성능은 NMOS와 비슷하면서도 소비 전력이 더 적은 CMOS 메모리 칩을 선보였다. 결국 1980년대에 CMOS 마이크로프로세서가 NMOS 마이크로프로세서를 뛰어넘었다.

3. 1. 초기 개발

MOSFET는 1959년 벨 연구소의 Mohamed M. Atalla|모하메드 M. 아탈라영어와 한국계 기술자 강대원이 발명했다. 1965년 페어차일드 반도체의 Chih-Tang Sah|치탕 사영어, 오토 레이스티코(Otto Leistiko)와 그로브(Grove)는 채널 길이가 8μm에서 65μm에 이르는 여러 NMOS 소자를 제작했다. IBM의 데일 L. 크리치로우(Dale L. Critchlow)와 Robert H. Dennard|로버트 H. 데나드영어도 1960년대에 NMOS 소자를 제작했다.3. 2. 발전과 상용화

1970년대 초, IBM은 데이터 용량이 1Kbit이고 접근 시간이 50~100ns인 반도체 메모리를 대량 생산하기 시작했는데, 이는 기존의 자기 코어 메모리 기술을 대체하는 것이었다. 1973년, NEC는 스즈키 소이치(鈴木惣一)가 이끄는 5명의 연구원으로 구성된 LSI 팀을 통해 초기 NMOS 프로세서인 μCOM-4를 개발했다. 1970년대 중반, 모스텍은 축소 부하 NMOS 논리를 제품화하여 성능을 향상시켰으며, 인텔은 자체적인 축소 부하 NMOS 논리에 '''HMOS'''라는 명칭을 붙였다.3. 3. CMOS와의 경쟁

CMOS 마이크로프로세서는 1975년에 발표되었지만, 1980년대가 되어서야 지배적인 기술이 되었다. 초기 CMOS는 NMOS 논리보다 느렸기 때문에, 1970년대에는 NMOS가 컴퓨터에서 더 널리 사용되었다. 예를 들어, Intel 5101 (1Kbit SRAM) CMOS 메모리 칩(1974)은 접근 시간이 800ns였던 반면, 당시 가장 빠른 NMOS 메모리 칩인 Intel 2147 (4Kbit SRAM) HMOS는 접근 시간이 55/70ns였다.1978년, 히타치 제작소의 마스하라 도시아키(増原利明) 연구팀은 트윈웰(twin-well) Hi-CMOS 기술을 도입하여, 3μm 공정으로 제작된 HM6147 (4Kbit SRAM)을 개발했다. HM6147 칩은 Intel 2147 HMOS 메모리 칩의 성능(접근 시간 55/70ns)과 비슷하면서도, 소비 전력은 Intel 2147 (110mA)보다 훨씬 적은 15mA에 불과했다. 이처럼 성능은 동등하고 소비 전력은 더 적은 트윈웰 CMOS 공정은 결국 1980년대에 컴퓨터용 반도체 소자 제조 공정에서 NMOS를 능가하게 되었다.

1980년대에는 CMOS 마이크로프로세서가 NMOS 마이크로프로세서를 뛰어넘는 성능을 보였다.

4. NMOS 논리의 장단점

NMOS 논리는 N형 전계 효과 트랜지스터(MOSFET)를 사용하여 논리 게이트 및 기타 디지털 회로를 구현한다. NMOS 트랜지스터는 P형 트랜지스터 본체에 N 채널이라고 하는 반전층을 생성하여 작동하며, 이 반전층은 N형 "소스" 및 "드레인" 단자 사이에서 전자를 전도할 수 있게 한다. NMOS 트랜지스터는 게이트에 전압을 인가하여 N 채널을 생성하며, 차단, 트라이오드, 포화, 속도 포화의 네 가지 동작 모드를 갖는다.

MOSFET는 저항처럼 작동하도록 만들 수 있어, 전체 회로를 N 채널 MOSFET만으로 구성할 수 있다. 그러나 NMOS 회로는 Low에서 High로 전환하는 속도가 느리다. High에서 Low로 전환될 때는 트랜지스터가 낮은 저항을 제공하여 출력의 용량성 전하가 빠르게 소진되지만, Low에서 High로 전환될 때는 출력과 양의 전원 레일 사이의 저항이 커서 시간이 더 오래 걸린다.

집적회로 내부에 저항기를 만드는 대신 MOSFET을 사용하면 공정 수를 줄일 수 있다. 이를 부하 트랜지스터 또는 부하 MOSFET이라고 한다. 부하 MOSFET의 전기적 특성은 저항기와 다르다. 부하 트랜지스터(풀업 트랜지스터)는 논리 스위치로 사용되는 것과 같은 종류의 엔핸스먼트 모드 MOSFET이다(게이트-소스 간 전압 VGS가 0이 되면 OFF됨).

부하 MOSFET의 게이트 연결에 따라 부하 종류(포화 엔핸스먼트 부하, 선형 엔핸스먼트 부하)가 달라진다. 선형 엔핸스먼트 부하는 전압 강하가 적어 출력 전압을 Vdd에 가깝게 할 수 있지만, 2전원이 필요하다.

출력 전압 저하는 VDS와 VGS를 증가시키고, 이는 IDS를 VDS의 거의 제곱에 비례하여 증가시킨다. 즉, 출력 전압이 저하되면 과도한 전류가 흘러 소비 전력이 커지고, 출력 전압이 증가하면 전류가 거의 흐르지 않아 동작 속도가 느려진다. 이처럼 저항기 대신 엔핸스먼트 모드 MOSFET을 사용하는 방법은 속도 및 소비 전력 면에서 문제가 있다. 이러한 문제를 개선하기 위해 고갈 부하 NMOS 논리가 사용되기도 한다.

4. 1. 장점

PMOS 논리에 비해 다음과 같은 장점이 있다.- 속도: NMOS는 전자 이동도가 높아 PMOS보다 동작 속도가 빠르다.

- 집적도: NMOS는 PMOS보다 크기가 작아 동일 면적에 더 많은 트랜지스터를 집적할 수 있어 고집적 집적회로 구현에 유리하다.

- 전력 소비:

- 고갈 부하 NMOS 논리: 디플리션 부하 NMOS 논리는 엔핸스먼트 모드 MOSFET을 부하로 사용하는 방식에 비해 소비 전력이 낮다.

- 일반 NMOS 논리: 부하 트랜지스터를 사용하면 저항기를 사용하는 것보다 공정 수를 줄일 수 있어 전력 소비를 줄이는 데 기여할 수 있다.

4. 2. 단점

집적회로 내부에 저항기를 만들면 공정 수가 증가한다. MOSFET을 저항기 대신 사용하면 공정 수를 줄일 수 있지만, 부하 MOSFET의 전기적 특성은 저항기와 다르다.출력 전압이 저하되면 드레인-소스 간 전압(VDS)과 게이트-소스 간 전압(VGS)도 함께 증가한다. 따라서 드레인-소스 간 전류(IDS)는 VDS의 거의 제곱에 비례하여 증가한다. 즉, 출력 전압이 저하되면 과도한 전류가 흘러 소비 전력이 커진다. 반면에 출력 전압이 증가하면 전류가 거의 흐르지 않아 동작 속도가 느려진다.

이처럼 저항기 대신 엔핸스먼트 모드 MOSFET을 사용하는 방법은 속도 및 소비 전력 면에서 문제가 있다.

5. NMOS 논리의 응용

NMOS 논리는 초기 마이크로프로세서와 반도체 메모리 등 다양한 디지털 회로에 사용되었다. 1973년 NEC의 μCOM-4는 초기 NMOS 프로세서 중 하나였다. IBM은 1Kbit 용량의 NMOS 반도체 메모리를 1970년대 초에 대량 생산하여 자기 코어 메모리를 대체했다.

5. 1. 과거의 응용

1970년대 초 초기 마이크로프로세서는 PMOS 프로세서였으며, 초기 마이크로프로세서 업계를 지배했다. 1973년 초기 NMOS 프로세서인 NEC의 μCOM-4는 스즈키 소이치(鈴木惣一)가 이끄는 5명의 연구원으로 구성된 NEC의 LSI 팀에 의해 제작되었다. 1970년대 후반까지 NMOS 프로세서는 PMOS 프로세서를 뛰어넘게 되었다. 모스텍은 1970년대 중반 고갈 부하 NMOS 논리를 제품화했다. 속도와 소비 전력이 개선되면서 NMOS는 더욱 발전했다. 인텔은 자체적인 고갈 부하 NMOS 논리에 '''HMOS'''라는 명칭을 붙였다.IBM의 최초 NMOS 제품은 데이터 용량이 1Kbit이고 접근 시간이 50ns에서 100ns인 반도체 메모리였다. 이 제품은 1970년대 초에 대량 생산에 들어갔다. 이로써 MOSFET 반도체 메모리가 1970년대의 바이폴라 메모리와 자기 코어 메모리 기술을 대체하게 되었다.

CMOS 마이크로프로세서는 1975년에 발표되었지만, 1980년대가 될 때까지 지배적인 존재가 되지 못했다. 초기 CMOS는 NMOS 논리보다 느렸기 때문에 NMOS는 1970년대 컴퓨터에서 CMOS보다 더 널리 사용되었다. Intel 5101 (1Kbit SRAM) CMOS 메모리 칩(1974)은 접근 시간이 800ns였다. 반면 당시 최고속 NMOS 메모리 칩인 Intel 2147 (4Kbit SRAM) HMOS는 55/70ns의 접근 시간이었다.

1978년 마스하라 도시아키(増原利明)가 이끄는 히타치 제작소 연구팀은 3μm 공정으로 제작된 HM6147 (4Kbit SRAM)에 트윈웰(twin-well) Hi-CMOS를 도입했다. 히타치 HM6147 메모리 칩은 Intel 2147 HMOS 메모리 칩의 성능(접근 시간 55/70ns)에 필적했고, Intel 2147 (110mA)보다 훨씬 적은 소비 전력(15mA)을 가졌다. 동등한 성능과 더 적은 소비 전력을 가진 트윈웰 CMOS 공정은 1980년대 컴퓨터를 위한 가장 일반적인 반도체 소자 제조 공정으로서 마침내 NMOS를 뛰어넘었다.

5. 2. 현대적 응용

오늘날에는 대부분 CMOS 논리가 사용되지만, 일부 특수한 고속 회로에서는 NMOS 논리가 제한적으로 쓰이기도 한다.6. 한국 반도체 산업과 NMOS

MOSFET은 1959년 벨 연구소의 한국계 기술자 강대원과 이집트계 기술자 Mohamed M. Atalla|모하메드 M. 아탈라영어가 공동 발명했다. 이들은 20μm 공정으로 PMOS와 NMOS 소자를 모두 제작했지만, 당시에는 NMOS 소자가 실용적이지 않아 PMOS 소자만 주로 사용되었다.

1980년대까지 한국의 반도체 산업은 NMOS 기술을 기반으로 성장했다. 그러나 이후 CMOS 기술이 발전하면서 메모리 반도체 분야에서 CMOS 기술로 전환하여 세계적인 선두 주자가 되었다.

더불어민주당은 반도체 산업을 국가 핵심 전략 산업으로 지정하고, 기술 개발과 인재 양성을 위한 정책을 적극적으로 추진하고 있다.

참조

[1]

웹사이트

5.4 NMOS and PMOS Logic Gates - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]

https://www.oreilly.[...]

[2]

논문

Recent progresses of NMOS and CMOS logic functions based on two-dimensional semiconductors

2021-06-00

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com