디지털 회로

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

디지털 회로는 이진법을 기반으로 정보를 처리하는 전자 회로로, 1705년 라이프니츠에 의해 이진법이 발전하면서 그 기초가 마련되었다. 20세기 초 진공관을 시작으로 트랜지스터, 집적 회로(IC)의 발전을 거치며 소형화, 고집적화되었으며, 현재는 컴퓨터, 통신, 제어 시스템 등 다양한 분야에서 활용된다. 디지털 회로는 잡음에 강하고, 정보 표현의 정확성을 높일 수 있으며, 소프트웨어 업데이트를 통해 기능을 개선할 수 있다는 장점이 있다. 주요 회로로는 플립플롭, 카운터, 가산기 등이 있으며, 논리 게이트와 버퍼를 사용하여 설계된다.

더 읽어볼만한 페이지

- 디지털 회로 - 클럭 신호

클럭 신호는 디지털 회로의 동작을 동기화하는 주기적인 신호로, 수정 발진기나 위상동기회로를 통해 생성되며 마이크로프로세서의 동작 속도를 결정하고 전력 효율을 위한 동적 주파수 변경 기술과 잡음 감소를 위한 사인파 클럭이 사용되기도 하며, 칩 내부 분배 효율성이 중요하다. - 디지털 회로 - 타이머

타이머는 시간 간격을 측정하거나 제어하는 장치 또는 기능으로, 기계식부터 전자식, 디지털, 소프트웨어 방식 등 다양한 형태로 존재하며, 독립적으로 사용되거나 시스템 내부에 내장되어 폭넓게 활용되고, 작동 방식과 구현 방식에 따라 여러 종류로 나뉘며, 최근에는 모바일 기반 타이머와 인공지능 기술을 활용한 효율적인 시간 관리 기능으로 발전하고 있다. - 전자공학 - 전자전

전자전은 적의 전투 능력을 저하시키기 위해 전자기 에너지를 사용하는 군사 작전이며, 전자 공격, 전자 보호, 전자 지원의 세 가지 영역으로 나뉘어 통신 방해, 레이더 교란, 스텔스 기술 등을 포함한다. - 전자공학 - 옴의 법칙

옴의 법칙은 1827년 게오르크 옴이 발표한, 전압(V)은 전류(I)와 저항(R)의 곱(V=IR)으로 표현되는, 전압, 전류, 저항 간의 관계를 나타내는 기본 법칙이다. - 표시 이름과 문서 제목이 같은 위키공용분류 - 라우토카

라우토카는 피지 비치레부섬 서부에 위치한 피지에서 두 번째로 큰 도시이자 서부 지방의 행정 중심지로, 사탕수수 산업이 발달하여 "설탕 도시"로 알려져 있으며, 인도에서 온 계약 노동자들의 거주와 미 해군 기지 건설의 역사를 가지고 있고, 피지 산업 생산의 상당 부분을 담당하는 주요 기관들이 위치해 있다. - 표시 이름과 문서 제목이 같은 위키공용분류 - 코코넛

코코넛은 코코넛 야자나무의 열매로 식용 및 유지로 사용되며, 조리되지 않은 과육은 100g당 354kcal의 열량을 내는 다양한 영양 성분으로 구성되어 있고, 코코넛 파우더의 식이섬유는 대부분 불용성 식이섬유인 셀룰로오스이며, 태국 일부 지역에서는 코코넛 수확에 훈련된 원숭이를 이용하는 동물 학대 문제가 있다.

| 디지털 회로 | |

|---|---|

| 디지털 전자 | |

| |

| |

| 개요 | |

| 정의 | 디지털 신호를 활용하는 전자 회로 |

| 설명 | |

| 회로 구성 | 논리 다이어그램 (불 대수식 기반)을 통해 구성 |

| 신호 종류 | 두 개 이상의 구별 가능한 파형 |

| 응용 분야 | |

| 예시 | 디지털 제어기 |

2. 역사

이진법은 고트프리트 빌헬름 라이프니츠(Gottfried Wilhelm Leibniz)에 의해 1705년에 발전되었으며, 그는 이진법을 사용하여 산술과 논리의 원리를 결합할 수 있다는 것을 확립했다.[2] 우리가 알고 있는 디지털 논리는 19세기 중반 조지 불(George Boole)의 창안물이었다.[2] 1886년 편지에서 찰스 샌더스 피어스(Charles Sanders Peirce)는 논리 연산이 전기 스위칭 회로에 의해 수행될 수 있는 방법을 설명했다.[2] 결국 진공관이 논리 연산을 위한 계전기를 대체했다. 리 드 포레스트(Lee De Forest)가 1907년 플레밍 밸브(Fleming valve)를 개조한 것은 AND 게이트로 사용될 수 있었다. 루트비히 비트겐슈타인(Ludwig Wittgenstein)은 그의 저서 ''논리철학논고''(Tractatus Logico-Philosophicus, 1921)의 명제 5.101에서 16행 진리표의 한 버전을 소개했다. 일치 회로(coincidence circuit)의 발명가인 발터 보테(Walther Bothe)는 1924년 최초의 현대식 전자 AND 게이트를 만든 공로로 1954년 노벨상 물리학상을 공동 수상했다.

기계식 아날로그 컴퓨터는 1세기에 처음 등장하여 나중에 중세 시대에 천문학적 계산에 사용되었다. 제2차 세계 대전 중에는 어뢰 조준 계산과 같은 특수 군사 응용 프로그램에 기계식 아날로그 컴퓨터가 사용되었다. 이 기간 동안 최초의 전자 디지털 컴퓨터가 개발되었으며, "디지털"이라는 용어는 조지 스티비츠(George Stibitz)가 1942년에 제안했다. 원래는 큰 방만한 크기였으며, 수백 대의 현대 PC만큼 많은 전력을 소비했다.[3]

클로드 섀넌(Claude Shannon)은 불 대수의 전기적 응용이 어떤 논리적 수치 관계도 구성할 수 있다는 것을 보여주었고, 1937년 그의 석사 논문에서 궁극적으로 디지털 컴퓨팅과 디지털 회로의 기초를 마련했다. 이 논문은 역사상 가장 중요한 석사 논문으로 여겨지며, 1939년 알프레드 노벨상을 수상했다.[4][5]

Z3는 콘라트 추제(Konrad Zuse)가 설계한 전기 기계식 컴퓨터였다. 1941년에 완성된 이 컴퓨터는 세계 최초의 작동 가능한 프로그래밍 가능하고 완전 자동화된 디지털 컴퓨터였다.[6] 그 작동은 존 앰브로스 플레밍(John Ambrose Fleming)이 1904년에 발명한 진공관에 의해 가능해졌다.

디지털 계산이 아날로그를 대체하는 동시에 순수 전자 회로 요소가 곧 기계적 및 전기 기계적 등가물을 대체했다. 존 바딘(John Bardeen)과 월터 브래튼(Walter Brattain)은 1947년 벨 연구소(Bell Labs)에서 점접촉 트랜지스터를 발명했고, 이어 윌리엄 쇼클리(William Shockley)가 1948년 벨 연구소에서 바이폴라 접합 트랜지스터를 발명했다.[7][8]

맨체스터 대학교(University of Manchester)의 톰 킬번(Tom Kilburn)의 지휘 아래 한 팀이 진공관 대신 새로 개발된 트랜지스터를 사용하는 기계를 설계하고 제작했다.[9] 그들의 "트랜지스터식 컴퓨터"는 세계 최초였으며, 1953년까지 작동 가능했고, 두 번째 버전은 1955년 4월에 완성되었다. 1955년부터 트랜지스터는 컴퓨터 설계에서 진공관을 대체하여 "2세대" 컴퓨터의 등장을 가져왔다. 진공관에 비해 트랜지스터는 더 작고, 더 신뢰할 수 있으며, 수명이 무한하고, 진공관보다 전력 소비량이 적어 열 발생이 적고, 비교적 작은 공간에 수만 개의 회로를 집적할 수 있었다.

1955년 칼 프로슈(Carl Frosch)와 링컨 데릭(Lincoln Derick)은 이산화규소 표면 패시베이션 효과를 발견했다.[10] 1957년 프로슈와 데릭은 마스크와 전착을 사용하여 드레인과 소스가 같은 표면에 인접한 최초의 플래너 트랜지스터인 이산화규소 전계 효과 트랜지스터를 제조했다.[11] 벨 연구소에서는 프로슈와 데릭의 기술과 트랜지스터의 중요성을 즉시 인식했다. 그들의 연구 결과는 1957년에 발표되기 전에 BTL 메모 형태로 벨 연구소에 널리 알려졌다. 쇼클리 반도체(Shockley Semiconductor)에서 쇼클리는 1956년 12월에 그들의 논문 사전 인쇄본을 장 호에르니(Jean Hoerni)를 포함한 모든 고위 직원에게 배포했다.[12][13][14][15] 호에르니는 나중에 페어차일드 반도체(Fairchild Semiconductor)에 있으면서 1959년에 플래너 공정을 발명했다.[16][17] 벨 연구소에서 J.R. 리겐자(J.R. Ligenza)와 W.G. 스피처(W.G. Spitzer)는 열적으로 성장한 산화물의 메커니즘을 연구하고 고품질 Si/SiO2 스택을 제작하여 1960년에 그 결과를 발표했다.[18][19][20] 벨 연구소의 이 연구에 이어 모하메드 아탈라(Mohamed Atalla)와 다원 칸(Dawon Kahng)은 1959년에 실리콘 MOS 트랜지스터를 제안했고[21] 1960년에 벨 연구소 팀과 함께 작동하는 MOS 소자를 성공적으로 시연했다.[22][23] 이 팀에는 소자를 제작한 E. E. 라베이트(E. E. LaBate)와 E. I. 포빌로니스(E. I. Povilonis), 확산 공정을 개발한 M. O. 서스턴(M. O. Thurston), L. A. 다사로(L. A. D’Asaro), J. R. 리겐자, 그리고 소자를 특성화한 H. K. 검멜(H. K. Gummel)과 R. 린드너(R. Lindner)가 포함되어 있었다.[24][25]

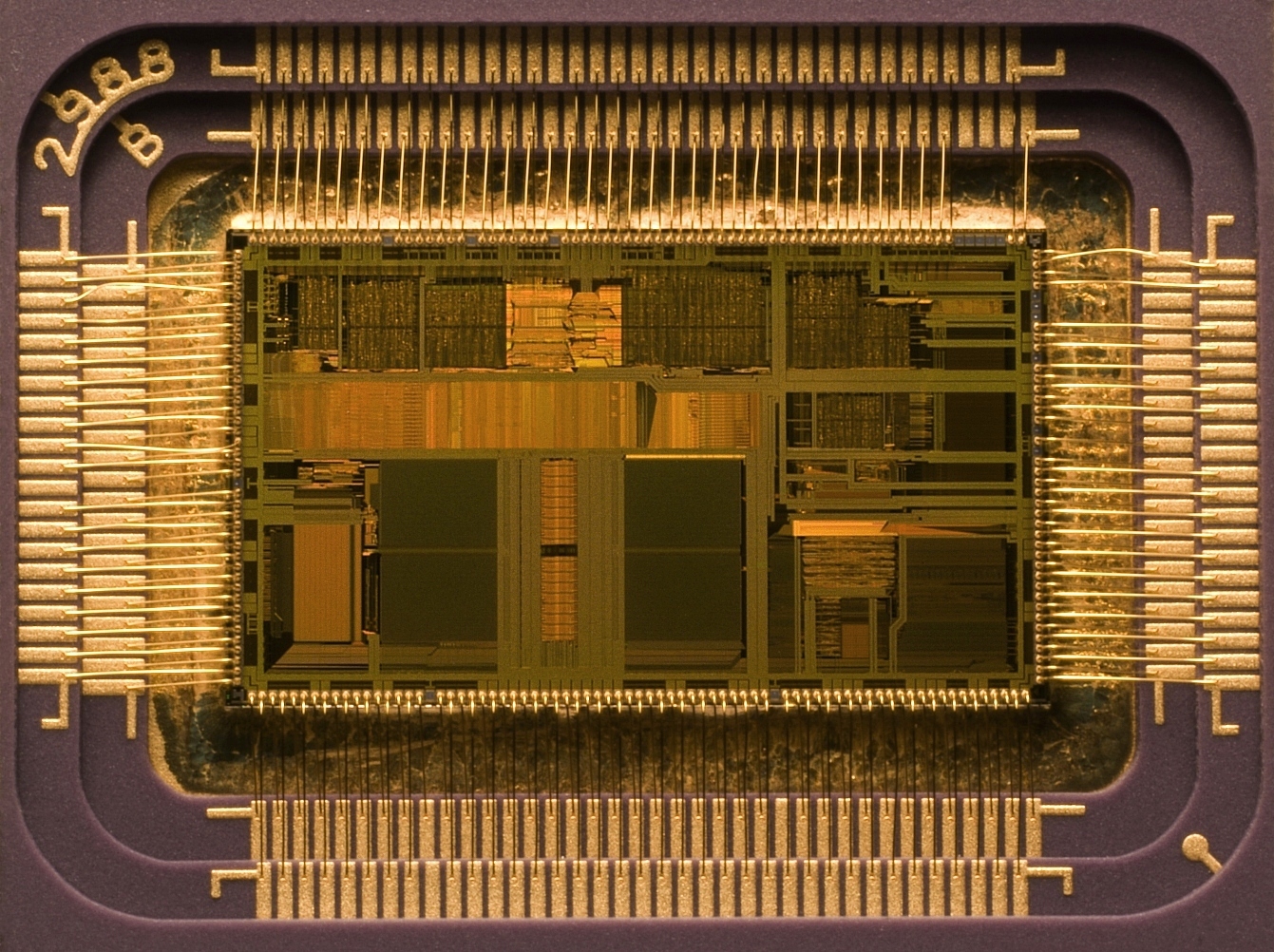

텍사스 인스트루먼츠(Texas Instruments)에서 1958년 7월에 근무하던 잭 킬비(Jack Kilby)는 집적 회로(IC)에 대한 초기 아이디어를 기록했고, 1958년 9월 12일에 최초의 작동하는 집적 회로를 성공적으로 시연했다.[26] 킬비의 칩은 게르마늄으로 만들어졌다. 다음 해 페어차일드 반도체(Fairchild Semiconductor)의 로버트 노이스(Robert Noyce)는 실리콘 집적 회로를 발명했다. 노이스의 실리콘 IC의 기반은 호에르니의 플래너 공정이었다.

MOSFET의 장점에는 높은 확장성,[27] 저렴한 가격,[28] 저전력 소비 및 높은 트랜지스터 밀도가 있다.[29] 또한 빠른 온-오프 전자 스위치 속도는 펄스 트레인을 생성하는 데 이상적이며,[30] 이는 전자 디지털 신호의 기반이 된다.[31][32] 반면에 BJT는 더 느리게 사인파를 닮은 아날로그 신호를 생성한다.[30] MOS 대규모 집적 회로(LSI)와 함께 이러한 요소들은 MOSFET을 디지털 회로의 중요한 스위칭 소자로 만듭니다.[33] MOSFET은 전자 산업에 혁명을 일으켰으며,[34][35] 가장 일반적인 반도체 소자이다.[36][37]

집적 회로 초기에는 각 칩이 몇 개의 트랜지스터로만 제한되었고, 통합 수준이 낮았기 때문에 설계 과정이 비교적 간단했다. 제조 수율도 오늘날의 기준으로는 상당히 낮았다. 1970년대 초 MOSFET 트랜지스터의 광범위한 채택은 단일 칩에 10,000개 이상의 트랜지스터가 있는 최초의 대규모 집적 회로(LSI) 칩으로 이어졌다.[38] 1980년대에 MOSFET 논리의 한 유형인 CMOS의 광범위한 채택에 따라 기술이 발전함에 따라 수백만 개, 그 후 수십억 개의 MOSFET을 하나의 칩에 배치할 수 있게 되었고,[39] 좋은 설계에는 철저한 계획이 필요하여 새로운 설계 방법이 등장했다. 소자의 트랜지스터 수와 총 생산량은 전례 없는 높이에 도달했다. 2018년까지 생산된 트랜지스터의 총량은 (13해 개)로 추정된다.[40]

무선 혁명(무선 네트워크의 도입과 확산)은 1990년대에 시작되었으며, MOSFET 기반 RF 전력 증폭기(전력 MOSFET 및 LDMOS)와 RF 회로(RF CMOS)의 광범위한 채택으로 가능해졌다.[41][42][43] 무선 네트워크는 케이블이 필요 없이 공개 디지털 전송을 가능하게 하여 1990년대~2000년대에 디지털 텔레비전, 위성 및 디지털 라디오, GPS, 무선 인터넷 및 휴대 전화로 이어졌다.

2. 1. 이진법의 발전

17세기 고트프리트 빌헬름 라이프니츠는 이진법을 발전시켜 산술 및 논리 연산을 결합할 수 있음을 확립했다.[2] 19세기 중반 조지 불은 현대 디지털 논리의 기반을 마련했다.[2] 1886년 찰스 샌더스 피어스는 논리 연산이 전기 스위칭 회로로 수행될 수 있음을 설명했다.[2] 클로드 섀넌은 불 대수의 전기적 응용이 어떤 논리적 수치 관계도 구성할 수 있다는 것을 보여주었고, 1937년 그의 석사 논문에서 궁극적으로 디지털 컴퓨팅과 디지털 회로의 기초를 마련했다.[4][5]2. 2. 초기 전자식 디지털 회로

조지 불이 19세기 중반 디지털 논리의 기반을 마련했고, 1886년 찰스 샌더스 피어스는 전기 스위칭 회로로 논리 연산을 수행할 수 있음을 설명했다.[2] 이후 진공관이 논리 연산에 사용되었으나, 크기가 크고 전력 소비가 많으며, 필라멘트가 끊어지기 쉬워 신뢰성이 낮다는 단점이 있었다. 팬아웃 수는 일반적으로 5~7이며, 발열에 제한되었다. 1950년대에는 컴퓨터 전용 진공관이 개발되어 수명이 수십만 시간으로 늘어났다. 클로드 섀넌은 1937년 석사 논문에서 불 대수의 전기적 응용이 어떤 논리적 수치 관계도 구성할 수 있다는 것을 보여주었고, 이는 디지털 컴퓨팅과 디지털 회로의 기초를 마련했다.[4][5]1941년 콘라트 추제가 개발한 Z3는 세계 최초의 프로그래밍 가능한 완전 자동 디지털 컴퓨터였다.[6] Z3는 존 앰브로스 플레밍이 1904년에 발명한 진공관을 사용하여 작동했다.

1947년 벨 연구소에서 존 바딘과 월터 브래튼이 점접촉 트랜지스터를 발명했고, 1948년에는 윌리엄 쇼클리가 바이폴라 접합 트랜지스터를 발명하면서 디지털 회로는 획기적인 발전을 이루게 되었다.[7][8] 맨체스터 대학교의 톰 킬번 연구팀은 1953년 세계 최초의 트랜지스터식 컴퓨터를 만들었고, 1955년에는 개선된 두 번째 버전을 완성했다.[9] 트랜지스터는 진공관보다 작고, 신뢰성이 높으며, 수명이 길고, 전력 소비량이 적어 디지털 회로에 널리 사용되기 시작했다.

2. 3. 집적 회로의 등장

1947년 벨 연구소(Bell Labs)에서 존 바딘(John Bardeen)과 월터 브래튼(Walter Brattain)이 점접촉 트랜지스터를 발명하고, 이어 1948년 윌리엄 쇼클리(William Shockley)가 바이폴라 접합 트랜지스터를 발명하면서 전자 회로 소자는 획기적인 전환을 맞이했다.[7][8] 1953년에는 맨체스터 대학교(University of Manchester)의 톰 킬번(Tom Kilburn) 팀이 진공관 대신 트랜지스터를 사용한 최초의 "트랜지스터식 컴퓨터"를 개발했다.[9] 1955년 이후 트랜지스터는 컴퓨터 설계에서 진공관을 대체하며 "2세대" 컴퓨터 시대를 열었다. 트랜지스터는 진공관보다 작고, 신뢰성이 높으며, 수명이 길고, 전력 소비가 적어 더 작은 공간에 더 많은 회로를 집적할 수 있었다.1958년 텍사스 인스트루먼츠(Texas Instruments)의 잭 킬비(Jack Kilby)는 최초의 집적 회로(IC)를 시연하였고,[26] 1959년 페어차일드 반도체(Fairchild Semiconductor)의 로버트 노이스(Robert Noyce)는 실리콘 집적 회로를 발명했다.[26] 이 실리콘 IC는 장 호에르니(Jean Hoerni)의 플래너 공정을 기반으로 했다.[16][17]

1959년 벨 연구소의 모하메드 아탈라(Mohamed Atalla)와 강대원(Dawon Kahng)은 MOSFET(금속 산화막 반도체 전계효과 트랜지스터)을 제안했으며,[21] 1960년에 작동하는 MOS 소자를 성공적으로 시연했다.[22][23] MOSFET은 높은 확장성,[27] 저렴한 가격,[28] 저전력 소비, 높은 트랜지스터 밀도[29], 빠른 스위칭 속도[30] 등의 장점을 바탕으로 디지털 회로의 핵심 소자가 되었다.[33]

1970년대 초 MOSFET 트랜지스터의 광범위한 채택은 단일 칩에 10,000개 이상의 트랜지스터를 집적한 최초의 대규모 집적 회로(LSI) 칩 개발로 이어졌다.[38] 1980년대에는 CMOS 논리의 광범위한 채택으로 수백만, 수십억 개의 MOSFET을 하나의 칩에 집적할 수 있게 되었고,[39] 이에 따라 새로운 설계 방법이 필요하게 되었다.

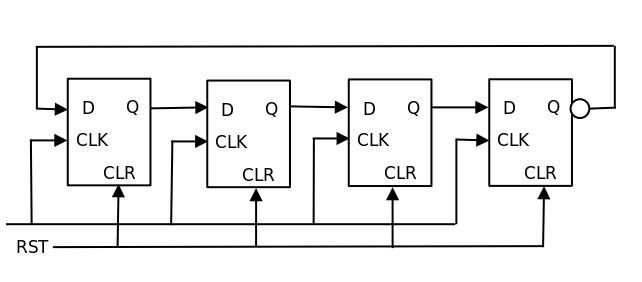

3. 주요 회로

디지털 회로는 기본적으로 논리 회로들을 조합하여 만들어지며, 기능에 따라서 다음과 같은 회로가 자주 사용된다.

- 플립플롭

- 카운터

- * 프로그래머블 카운터

- 위상동기회로

- 가산기

- 디지털-아날로그 변환회로

- 아날로그-디지털 변환회로

디지털 회로는 일반적으로 논리 게이트라고 하는 작은 전자 회로로 구성되며, 이는 조합 논리를 만드는 데 사용할 수 있다. 각 논리 게이트는 논리 신호에 작용할 때 부울 논리의 함수를 수행하도록 설계된다. 논리 게이트는 일반적으로 하나 이상의 전기적으로 제어되는 스위치, 일반적으로 트랜지스터(하지만 역사적으로는 진공관이 사용되었다)로 만들어진다. 논리 게이트의 출력은 차례로 더 많은 논리 게이트를 제어하거나 공급할 수 있다.

또 다른 형태의 디지털 회로는 조회 테이블(많은 것이 "프로그래머블 논리 디바이스"로 판매되지만 다른 종류의 PLD도 존재한다)로 구성된다. 조회 테이블은 논리 게이트 기반 머신과 동일한 기능을 수행할 수 있지만 배선을 변경하지 않고도 쉽게 재프로그래밍할 수 있다. 즉, 설계자는 배선 배치를 변경하지 않고도 설계 오류를 수정할 수 있다. 따라서 소량 생산품의 경우 프로그래머블 논리 디바이스가 종종 선호되는 솔루션이다. 이러한 디바이스는 일반적으로 전자 설계 자동화 소프트웨어를 사용하는 엔지니어가 설계한다.

집적 회로는 하나의 실리콘 칩에 여러 개의 트랜지스터로 구성되며, 많은 수의 상호 연결된 논리 게이트를 만드는 가장 저렴한 방법이다. 집적 회로는 일반적으로 인쇄 회로 기판에 상호 연결되는데, 이는 전기 부품을 보유하고 구리 도선으로 서로 연결하는 기판이다.

디지털 회로는 논리 게이트라고 불리는 작은 전자 회로로 구성되는 경우가 많으며, 이를 통해 조합 논리를 형성한다. 개별 논리 게이트는 부울 논리 함수를 구현한다. 논리 게이트는 전기로 제어되는 스위치를 배치한 것이며, 스위치로 트랜지스터를 사용하는 경우가 많다. 논리 게이트는 각각 회로 기호가 대응된다. 자세한 내용은 논리 회로를 참조.

논리 게이트의 출력은 전류 또는 전압이며, 그것이 후단의 논리 게이트들을 제어한다.

논리 게이트는 트랜지스터의 개수를 최소한으로 줄여 크기, 전력 소비, 비용을 가능한 한 낮추고 동시에 신뢰성을 높이도록 설계된다.

집적 회로는 많은 논리 게이트를 저렴하게 생산하는 수단이다. 집적 회로 설계에는 EDA 소프트웨어를 사용하는 것이 일반적이다(후술).

참조 테이블을 사용하여 디지털 회로를 구성하는 기법도 있다(프로그래머블 로직 디바이스 등). 참조 테이블을 사용하는 기법은 논리 게이트를 기반으로 하는 경우와 동등한 기능을 구현할 수 있으며, 동시에 배선을 변경하지 않고 쉽게 재프로그래밍이 가능하다. 즉, 설계자가 배선을 변경하지 않고 설계 오류를 수정할 수 있다. 따라서 소량 생산에서는 PLD 등을 자주 사용한다. 이것들도 일반적으로 EDA 소프트웨어로 설계된다.

디지털 회로로 대규모의 것이 필요하고, 저속이라도 복잡한 알고리즘이나 연쇄적인 동작이 필요한 경우, 임베디드 시스템으로 마이크로컨트롤러에 프로그램을 탑재하여 사용하는 경우가 많다.

공장의 생산 라인 제어 등에서는 프로그래머블 로직 컨트롤러(PLC)가 자주 사용된다. 이것은 래더 로직 등을 사용하여 생산 라인 엔지니어가 프로그래밍을 한다.

3. 1. 기본 논리 회로

디지털 회로는 기본적으로 논리 회로들을 조합하여 만들어지며, 기능에 따라서 플립플롭, 카운터, 위상동기회로, 가산기와 같은 회로가 자주 사용된다.디지털 회로는 일반적으로 논리 게이트라고 하는 작은 전자 회로로 구성되며, 이는 조합 논리를 만드는 데 사용할 수 있다. 각 논리 게이트는 논리 신호에 작용할 때 부울 논리의 함수를 수행하도록 설계된다. 논리 게이트는 일반적으로 하나 이상의 전기적으로 제어되는 스위치, 일반적으로 트랜지스터로 만들어진다. 논리 게이트의 출력은 차례로 더 많은 논리 게이트를 제어하거나 공급할 수 있다.

집적 회로는 하나의 실리콘 칩에 여러 개의 트랜지스터로 구성되며, 많은 수의 상호 연결된 논리 게이트를 만드는 가장 저렴한 방법이다. 집적 회로는 일반적으로 인쇄 회로 기판에 상호 연결된다.

3. 2. 변환 회로

디지털-아날로그 변환회로(DAC)는 디지털 신호를 아날로그 신호로 변환한다. 아날로그-디지털 변환회로(ADC)는 아날로그 신호를 디지털 신호로 변환한다.4. 디지털 회로의 논리 표현

디지털 회로는 전압 레벨을 기준으로 논리 상태를 표현한다. 초기에는 전압을 기준으로 논리를 표현하는 방법이 표준화되었다.

- 참 (True) : 전압 VCC [V]

- 거짓 (False) : 전압 0 [V]

일반적으로 단일 전원을 사용하며, 스위칭 소자의 특성상 출력 전압은 VCC 또는 0V가 정확히 되지 않는다. 따라서 특정 전압 범위 내에서 논리 레벨을 결정한다.

- H (논리 1) : (VCC - VS) ~ VCC

- L (논리 0) : VS ~ 0V

여기서 VS는 스위칭 소자(BJT, FET 등)의 임피던스에 걸리는 전압이다. BJT의 경우 포화 상태에서 C-E 간 전압(약 0.2V 이하)이며, 쇼트키 트랜지스터는 ON 시 약 0.35V이다. 실제로는 외부 회로와의 전압 관계 및 노이즈 마진을 고려하여 더 넓은 전압 범위로 표준화된다. (예: TTL LS형은 0 ~ 0.8V를 논리 0으로 설정)

디지털 회로의 입력-출력 관계는 진리표로 나타낼 수 있다. 논리 게이트는 IEEE/ANSI 91–1984에 의해 표준화된 모양으로 표현된다.[45] 하위 레벨에서는 트랜지스터와 같은 전자 스위치의 등가 회로를 사용한다.

대부분의 디지털 시스템은 조합 논리 회로와 순차 논리 회로로 나뉜다. 조합 회로의 출력은 현재 입력에만 의존하지만, 순차 회로는 과거 입력에도 영향을 받는다. 상태 기계는 순차 회로의 동작을 단순화하여 표현한다.

순차 시스템은 동기식 시스템과 비동기식 시스템으로 나뉜다. 동기식 시스템은 클럭 신호에 따라 상태가 변경되는 반면, 비동기식 시스템은 입력 변경에 따라 변경이 전파된다. 동기식 시스템은 플립플롭을 사용하여 클럭 변화 시 입력된 전압을 비트로 저장한다.

### 전압 레벨과 논리 상태

디지털 회로는 일반적으로 두 가지 전압 레벨을 사용하여 이진 논리 레벨 "0"과 "1"을 나타낸다.[45] 정논리(능동 하이)에서는 낮은 전압(Low)이 "0", 높은 전압(High)이 "1"을 나타내며, 부논리(능동 로우)에서는 반대로 사용된다.[45] 예를 들어, 시모스에서는 0V ~ 0.3Vcc를 '0', 0.7Vcc ~ Vcc를 '1'로, TTL에서는 0V ~ 0.8V를 '0', 2V ~ Vcc를 '1'로 정의한다.[70]

| 회로 소자 | Low의 전압 | High의 전압 |

|---|---|---|

| CMOS | 0 - 0.3Vdd | 0.7Vdd - Vdd |

| TTL | 0 - 0.8V | 2V - Vcc |

Vdd와 Vcc는 전원 전압을 의미한다. TTL의 전원 전압 허용 범위는 4.75~5.25V이다.

초기 논리 회로는 5V 기준이었으나, 고속 클럭 등에서 전력 및 속도 문제로 인해 점차 낮아져 3.3V가 많이 사용된다.[70]

1.5~3.5V 사이는 임계 레벨로, 논리 천이 시 외에는 금지된 전압 영역이다.[45] 이 구간에서는 High와 Low 입력 구분이 어려워 동작이 보장되지 않는다.[45] 논리 천이 기간은 과도 현상 때문에 발생하며, 대부분의 회로는 순수 저항 회로가 아니므로 전압 레벨이 즉시 변하지 않기 때문이다.

CMOS 디지털 회로에서는 이상 상태가 오래 지속되면 발열로 소자가 파손될 수 있으므로, 이상 상태 지속을 피하기 위한 회로 설계가 필요하다.[45] 히스테리시스(이력 현상)를 이용한 슈미트 트리거는 이상 상태를 회피하는 방법 중 하나이다.[45]

전원 전압이 같은 CMOS와 TTL이 혼재하는 경우, CMOS 출력을 TTL에 입력하는 것은 문제없지만, 반대의 경우 TTL의 H 레벨 출력 전압 하한이 CMOS의 H 레벨 입력 전압 하한을 만족하지 않아 오동작 가능성이 있다. 이 경우 TTL 출력을 풀업하는 등의 처리가 필요하다.[58]

초기 디지털 회로에서는 실리콘 기판 상 트랜지스터 형성 제한으로 PMOS 또는 NMOS로 회로 내부를 구성했다. 입력이 Low일 때와 High일 때 전력 소비 특성이 다르므로, 능동 하이 또는 능동 로우 설계 결정이 전력 소비 절감에 중요했다.[45]

### 슈미트 트리거

'''슈미트 트리거'''(Schmitt Trigger)는 히스테리시스(이력 현상) 특성을 이용하여 파형 상승/하강 시 논리 천이 값을 다르게 하여 이상 상태를 방지하는 회로이다.[58] 저항기 연결로 쉽게 구현 가능하며, 전용 범용 논리 IC도 있다.

디지털 회로에서 이진수 논리 레벨 "0"과 "1"은 두 전압 레벨로 나타낸다. 정논리(능동 하이)에서 0~1.5V는 논리 0, 3.5~5V는 논리 1이다. 1.5~3.5V는 임계 레벨로, 논리 천이 시 외에는 금지된 전압 영역이다. 이 영역에서는 High/Low 입력 구분이 어려워 동작이 보장되지 않는다. 전단 회로 천이에 시간이 걸리면 후단 회로에서 입력을 High 또는 Low로 해석하는 문제가 발생할 수 있다.

CMOS 디지털 회로에서는 이상 상태 지속 시 발열로 소자가 파손될 수 있어, 이를 방지하는 회로 설계가 필요하다.

74LS04는 LS 타입의 일반 전압 기준으로 동작하지만, 74LS14는 슈미트 트리거 특성을 갖는다. 슈미트 트리거 동작에서 LS와 HC 타입 동작 범위가 다르므로 선택적으로 사용해야 한다.

| 회로 소자 | Low의 전압 | High의 전압 |

|---|---|---|

| CMOS | 0 - 0.3Vdd | 0.7Vdd - Vdd |

| TTL | 0 - 0.8V | 2V - Vcc |

Vdd와 Vcc는 전원 전압을 의미한다. TTL의 전원 전압 허용 범위는 4.75~5.25V이다.

CMOS와 TTL 혼재 시, CMOS 출력을 TTL에 입력은 문제없지만, 반대는 TTL의 H 레벨 출력 전압 하한이 CMOS의 H 레벨 입력 전압 하한을 만족하지 않아 오동작 가능성이 있다. TTL 출력을 풀업하는 등의 처리가 필요하다.[58]

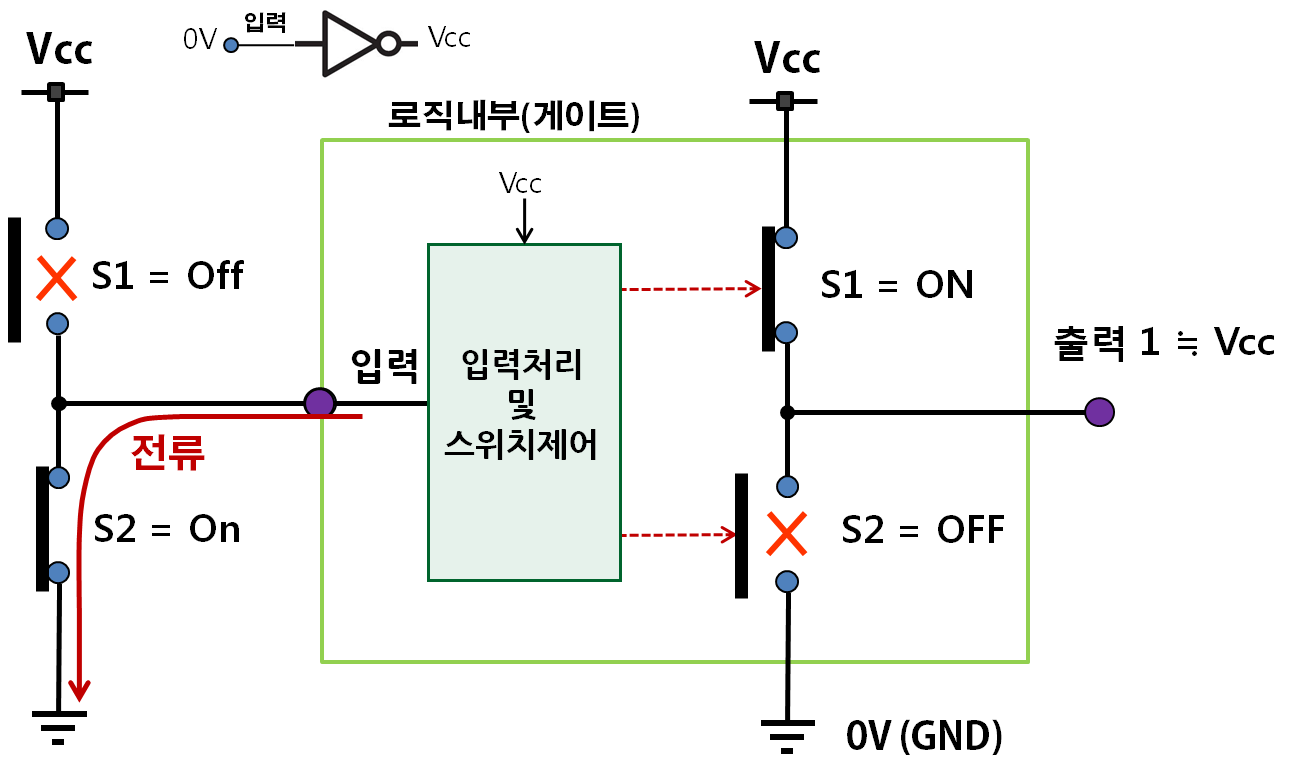

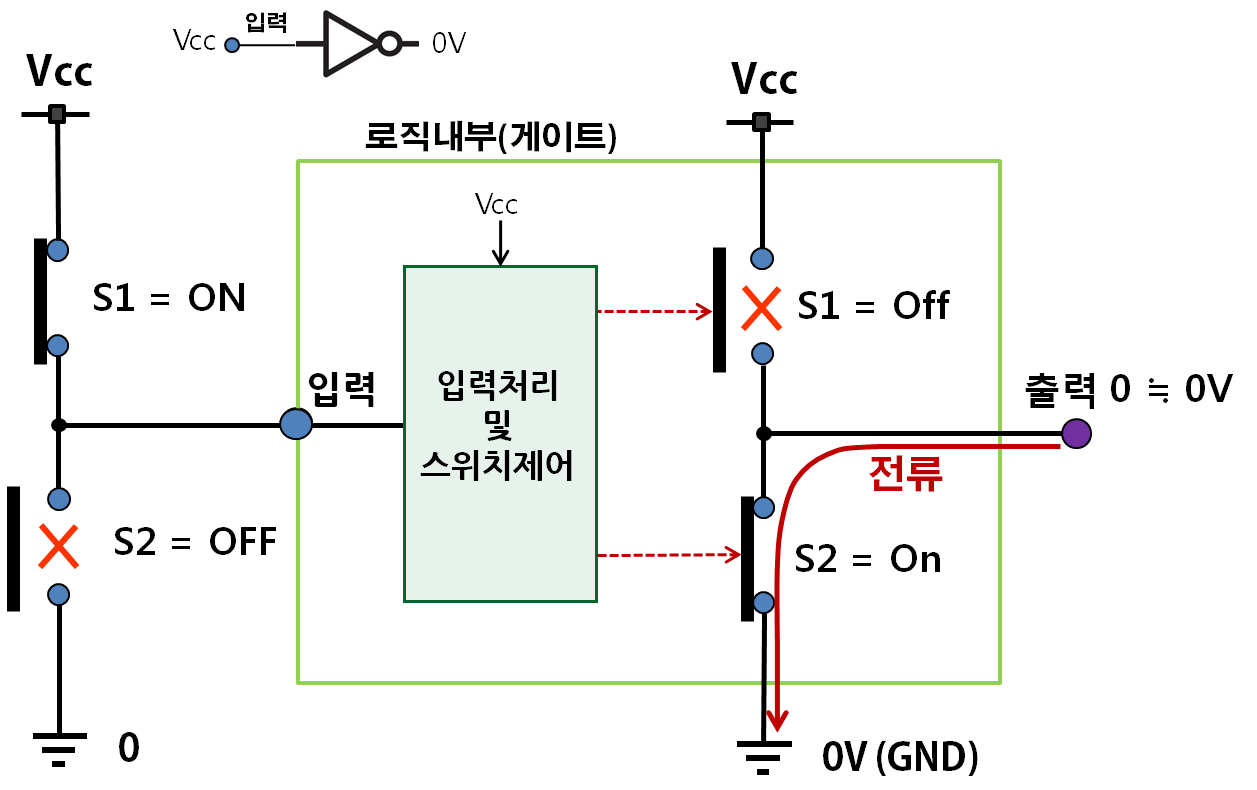

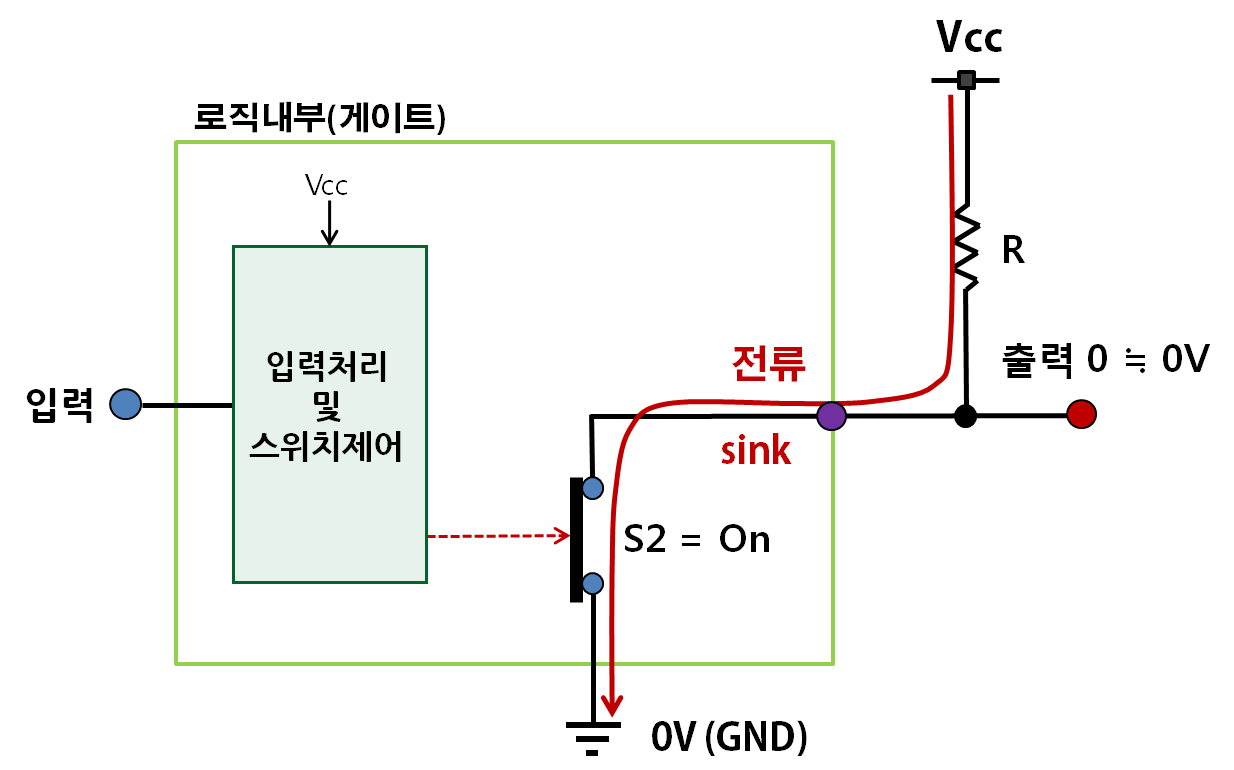

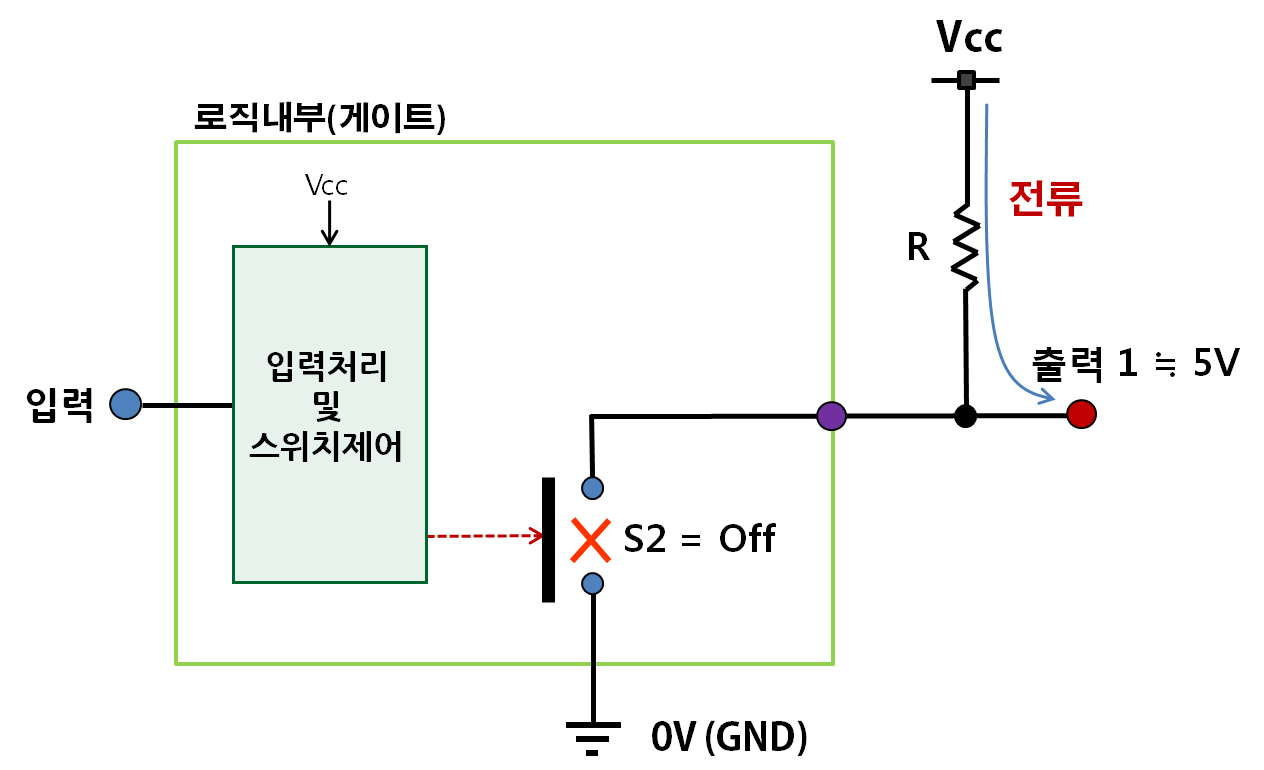

### 입력 및 출력

디지털 회로의 입력은 논리 전압 기준에 따라 특정 전압을 입력하여 이루어진다. 논리 1은 Vcc, 논리 0은 0V로 규정되어 해당 전압을 입력 노드에 유지함으로써 신호가 입력된다. 회로 구성에 따라 전류 및 전력 소모/공급 여부는 달라진다.

| 논리 0 | 논리 1 |

|---|---|

|  |

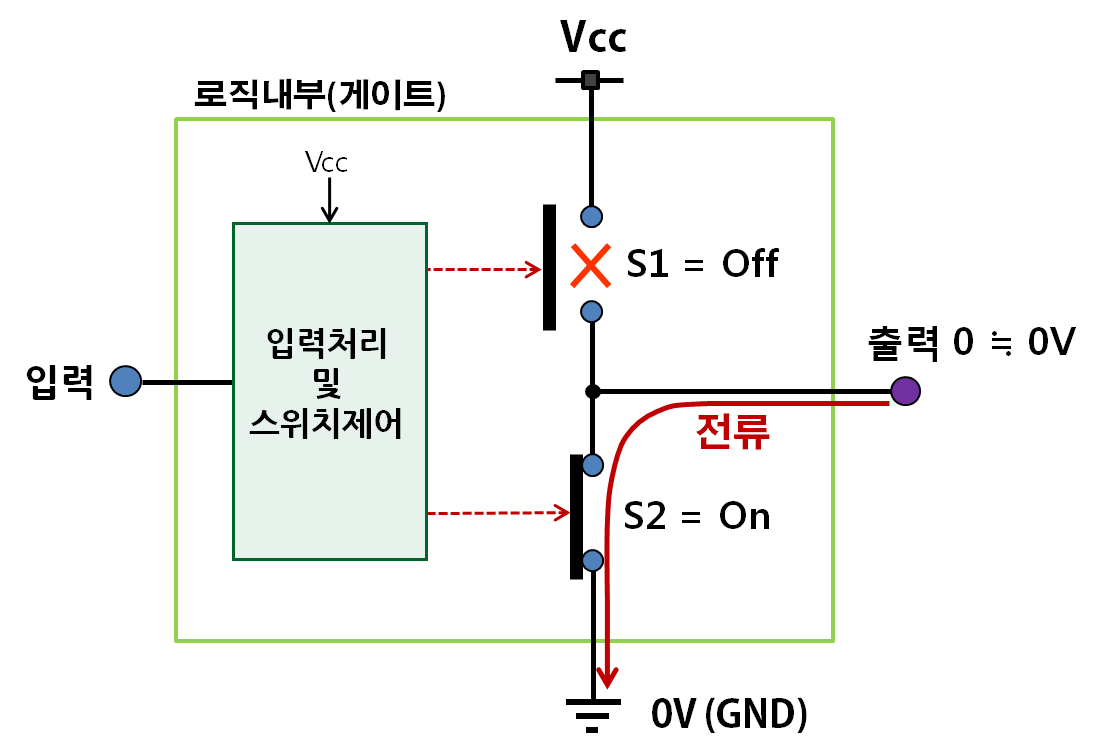

출력은 특정 노드에 Vcc(논리 1) 또는 0V(논리 0) 전압이 나타나는 방식이다. 출력 노드에서 전압이 나타난다고 해서 반드시 전력을 출력하는 것은 아니며, 회로 구성에 따라 전력 출력, 소모, 또는 전류가 흐르지 않는 경우가 존재한다.

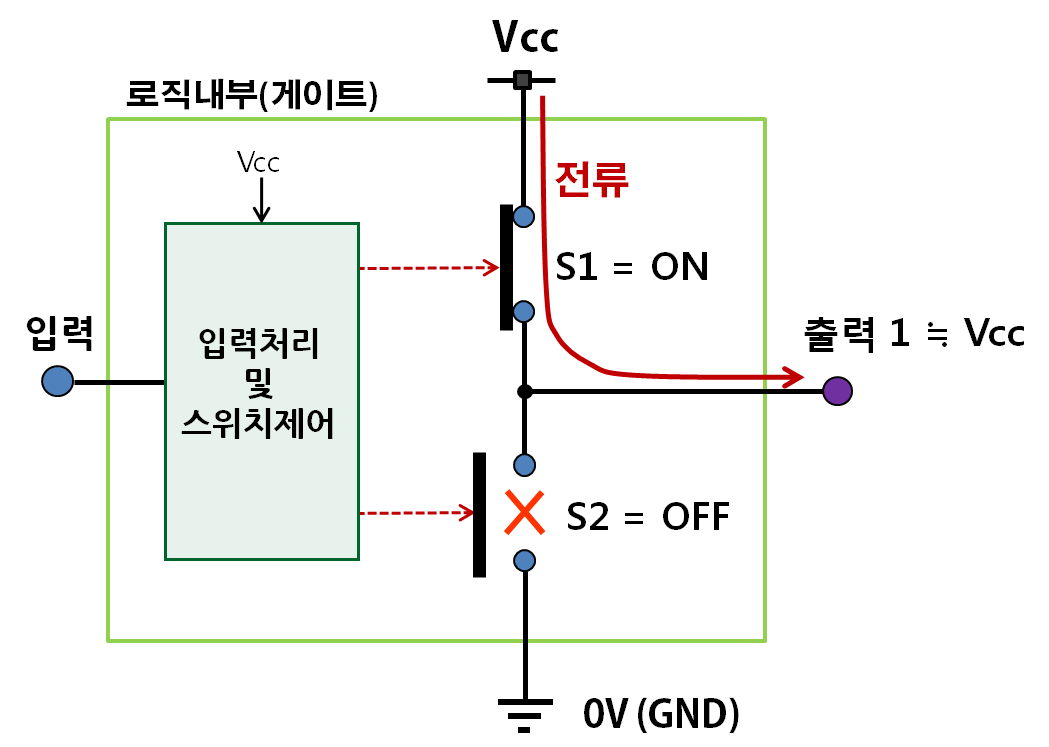

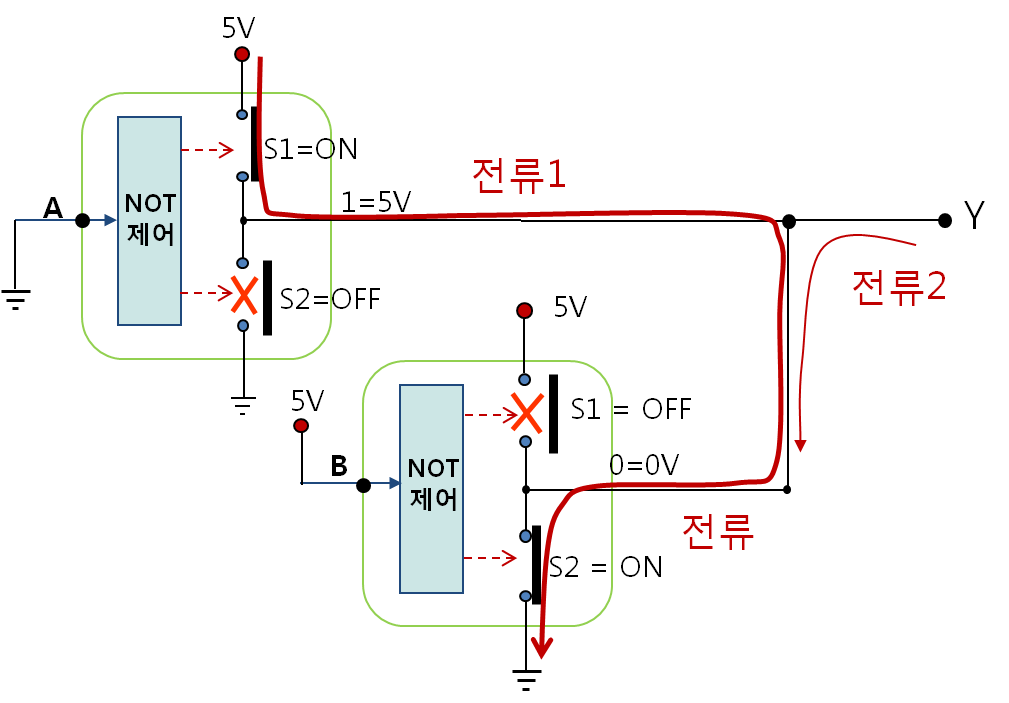

토템폴(Totem Pole) 출력은 두 스위치를 사용하여 논리 1일 때 Vcc, 논리 0일 때 GND를 출력 노드에 연결한다. 각 스위치는 BJT나 FET 같은 전자 스위치로 대체될 수 있다.

| 논리 0 | 논리 1 | 논리 Z |

|---|---|---|

|  |  |

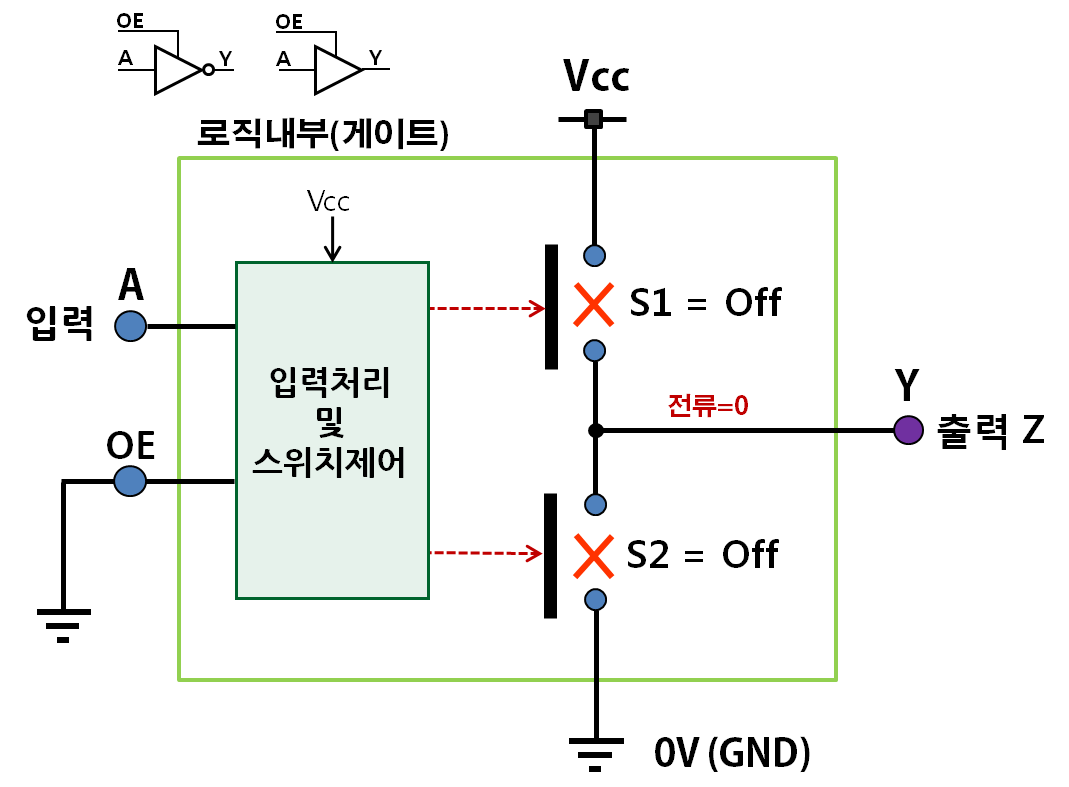

버스 구조에서는 신호 충돌 방지를 위해 하이 임피던스(High Impedance) 상태("Z")가 사용된다. 이는 출력 신호선을 전기적으로 절연하는 상태이다. 하이 임피던스 상태에서는 풀업/풀다운 저항을 연결하여 안정적인 논리 상태를 유지한다.[60]

| 출력의 충돌로 쇼트가 일어나는 예 |

|---|

|

|

오픈 컬렉터 출력은 논리 1일 때 하이 임피던스 상태가 되는 출력 방식이다. 여러 오픈 컬렉터 출력을 연결하고 풀업하면 와이어드 AND(Wired AND) 회로를 구현할 수 있다.

| 논리 0 | 논리 1 |

|---|---|

|  |

오픈 컬렉터는 단일 전원, 더 많은 전류 필요, 와이어드 AND 구현 등에 사용되며, 마이크로프로세서에서 다른 칩과의 통신(예: I2C)에 활용된다.

### 풀업 및 풀다운

디지털 회로는 High 또는 Low 전압 인가가 되어 있어야 한다. High와 Low 중간 전압은 내부 상태를 불안정하게 하거나 전력 소비를 증가시킨다. Low보다 낮거나 High보다 높은 전압은 회로를 파괴할 수 있다.[59]

일반적으로 디지털 회로 입력 단자는 내부 임피던스가 높아, 연결되지 않은 상태에서는 주변 정전기나 전자기 유도로 예상치 못한 전압이 인가될 수 있다. 이를 "플로팅"이라 한다.[59]

이를 해결하기 위해 수 kΩ ~ 수백 kΩ 저항을 전원선/접지선에 연결한다. 전원선 연결은 "풀업", 접지선 연결은 "풀다운"이다. 풀업/풀다운된 입력 단자는 출력 단자 미연결 시에도 전원/접지 전압이 유지된다.[59]

다른 디지털 회로 출력 단자 접속 시, 디지털 소자 출력 회로는 내부 임피던스가 매우 작아 풀업/풀다운 저항값은 무시된다. 풀업 저항값이 너무 크면 플로팅 상태와 비슷해져 전자 유도에 약해지고, 너무 작으면 연결된 출력 소자에 큰 전류가 흘러 소비 전력 증가/소자 파손될 수 있다.[59]

신호선이 길 경우, 전자 유도로 이상 전압 발생 가능하다. 풀업 저항에 병렬로 다이오드를 연결하여 이상 전압 전류를 전원선으로 흘려보내 소자를 보호할 수 있다. 이를 "클램프 다이오드"라 한다.[59]

디지털 회로 설계 시 미사용 회로 입력 단자는 반드시 풀업/풀다운해야 한다. 최근 CPU IC는 부품 수 절감을 위해 풀업 저항을 내장하며, 소프트웨어 제어 가능한 경우도 있다.[59]

4. 1. 전압 레벨과 논리 상태

일반적으로 디지털 회로에서는 두 가지 전압 레벨을 사용하여 이진수 또는 논리 레벨의 "0"과 "1"을 나타낸다.[45] 정논리(능동 하이)에서는 낮은 전압(Low)은 이진수 "0", 높은 전압(High)는 이진수 "1"을 나타내고, 부논리(능동 로우)에서는 그 반대로 사용된다.[45] 예를 들어, 시모스에서는 0V ~ 0.3Vcc를 '0', 0.7Vcc ~ Vcc를 '1'로, TTL에서는 0V ~ 0.8V를 '0', 2V ~ Vcc를 '1'로 정의한다.[70]| 회로 소자 | Low의 전압 | High의 전압 |

|---|---|---|

| CMOS | 0 - 0.3Vdd | 0.7Vdd - Vdd |

| TTL | 0 - 0.8V | 2V - Vcc |

Vdd와 Vcc는 전원 전압을 의미한다. TTL의 전원 전압 허용 범위는 4.75~5.25V이다.

초기의 논리회로는 5V 기준이었으나, 전압이 높으면 고속 클럭 등에서 전력 및 속도 면에서 불리하므로 점차 낮아지는 추세이다. 3.3V가 많이 사용되는 전압이다.[70]

1.5~3.5볼트 사이는 임계 레벨이라고 불리며, 논리 천이 시 이외에는 금지된 전압 영역이다.[45] 이 구간에서는 High와 Low 입력의 구분이 어려워 동작이 보장되지 않는다.[45] 논리 천이 기간은 일반적으로 과도 현상이며, 대부분의 회로는 순수한 저항 회로가 아니므로 전압 레벨이 즉시 변하지 않기 때문에 발생한다. 이러한 이상 상태를 감지할 수 있는 논리 회로도 있지만, 많은 경우 후단 회로에서는 전단 회로의 천이에 의해 출력을 변경하기 전에 전단의 천이가 종료되어 High 또는 Low로 안정된다. 하지만 전단 회로의 천이에 시간이 걸리면 후단 회로에서는 입력을 High 또는 Low 중 하나로 해석한다.

CMOS를 사용한 디지털 회로의 경우, 내부 구조상 이러한 이상 상태일 때 회로가 많은 전력을 소비한다. 따라서 이상 상태가 오래 지속되면 발열로 소자가 파손될 수 있으므로 이상 상태의 지속을 피하기 위한 회로상의 고안이 필요하다.[45] 한편, 파형의 상승과 하강에서 논리 천이의 값을 의도적으로 다른 값으로 하는 것(히스테리시스, 이력 현상)으로 이상 상태를 회피하는 방법이 있으며, 슈미트 트리거라고 한다. 저항기의 연결에 의해 쉽게 실현 가능하며, 전용 범용 논리 IC도 있다.[45]

전원 전압이 같은 CMOS와 TTL이 동일 회로 상에 혼재하는 경우, CMOS의 출력을 TTL에 입력하는 것은 문제 없지만, 그 반대의 경우 TTL의 H 레벨 출력 전압의 하한이 CMOS의 H 레벨 입력 전압의 하한을 만족시키지 않으므로 오동작할 가능성이 있다. 이러한 경우에는 TTL의 출력을 풀업하는 등의 처리가 필요하다.[58]

초기 디지털 회로에서는 실리콘 기판 상의 트랜지스터 형성의 제한으로 PMOS 또는 NMOS로 회로 내부를 구성했다. 이 경우, 입력이 Low일 때는 전력 소비가 적지만 입력이 High일 때는 전력 소비가 크거나 그 반대의 특성을 가지므로, 이에 맞춰 능동 하이로 논리 회로를 설계할지, 능동 로우로 논리 회로를 설계할지를 결정하는 것이 전력 소비 절감에 중요한 의미를 가졌다.[45]

4. 2. 슈미트 트리거

'''슈미트 트리거'''(Schmitt Trigger)는 히스테리시스(이력 현상) 특성을 이용하여 파형의 상승이나 하강 시 논리 천이 값을 다르게 함으로써 이상 상태를 방지하는 회로이다.[58] 저항기 연결을 통해 쉽게 구현 가능하며, 전용 범용 논리 IC도 있다.

디지털 회로에서 이진수 또는 논리 레벨의 "0"과 "1"은 두 개의 전압 레벨로 나타낸다. 예를 들어, 정논리(능동 하이)에서는 0~1.5볼트가 논리 0, 3.5~5볼트가 논리 1이 된다. 1.5~3.5볼트 사이는 임계 레벨로, 논리 천이 시 외에는 금지된 전압 영역이다. 이 영역에서는 High와 Low 입력 구분이 어려워 동작이 보장되지 않는다. 하지만 전단 회로의 천이에 시간이 걸리면 후단 회로에서 입력을 High 또는 Low 중 하나로 해석하는 문제가 발생할 수 있다.

CMOS 디지털 회로에서는 이상 상태가 오래 지속되면 발열로 소자가 파손될 수 있으므로, 이를 방지하기 위한 회로 설계가 필요하다.

74LS04는 LS 타입의 일반적인 전압 기준에 따라 동작하지만, 74LS14는 슈미트 트리거 특성을 갖는다. 슈미트 트리거의 동작에서 LS와 HC 타입의 동작 범위가 다르므로 선택적으로 사용해야 한다.

| 회로 소자 | Low의 전압 | High의 전압 |

|---|---|---|

| CMOS | 0 - 0.3Vdd | 0.7Vdd - Vdd |

| TTL | 0 - 0.8V | 2V - Vcc |

Vdd와 Vcc는 전원 전압을 의미한다. TTL의 전원 전압 허용 범위는 4.75~5.25V이다.

전원 전압이 같은 CMOS와 TTL이 동일 회로 상에 혼재하는 경우, CMOS의 출력을 TTL에 입력하는 것은 문제 없지만, 그 반대의 경우 TTL의 H 레벨 출력 전압의 하한이 CMOS의 H 레벨 입력 전압의 하한을 만족시키지 않으므로 오동작할 가능성이 있다. 이러한 경우에는 TTL의 출력을 풀업하는 등의 처리가 필요하다.[58]

4. 3. 입력 및 출력

디지털 회로의 입력은 논리 전압 기준에 따라 특정 전압을 입력하여 이루어진다. 논리 1은 Vcc, 논리 0은 0V로 규정되어 있어, 해당 전압을 입력 노드에 유지함으로써 신호가 입력된다. 이때, 회로 구성에 따라 전류 및 전력 소모/공급 여부는 달라진다.| 논리 0 | 논리 1 |

|---|---|

출력은 특정 노드에 Vcc(논리 1) 또는 0V(논리 0) 전압이 나타나는 방식으로 이루어진다. 출력 노드에서 전압이 나타난다고 해서 반드시 전력을 출력하는 것은 아니며, 회로 구성에 따라 전력 출력, 소모, 또는 전류가 흐르지 않는 경우가 존재한다.

대표적인 출력 방식으로는 토템폴(Totem Pole) 출력이 있다. 이는 두 개의 스위치를 사용하여 논리 1일 때는 Vcc, 논리 0일 때는 GND를 출력 노드에 연결하는 방식이다. 각 스위치는 BJT나 FET와 같은 전자 스위치로 대체될 수 있다.

| 논리 0 | 논리 1 | 논리 Z |

|---|---|---|

버스 구조에서는 신호 충돌을 방지하기 위해 하이 임피던스(High Impedance) 상태가 사용된다. 이는 출력 신호선을 전기적으로 절연하는 상태로, "Z"로 표기된다. 하이 임피던스 상태에서는 풀업 또는 풀다운 저항을 연결하여 안정적인 논리 상태를 유지하는 것이 일반적이다.[60]

| 출력의 충돌로 쇼트가 일어나는 예 |

|---|

오픈 컬렉터 출력은 논리 1일 때 하이 임피던스 상태가 되는 출력 방식이다. 여러 오픈 컬렉터 출력을 연결하고 풀업하면 와이어드 AND(Wired AND) 회로를 구현할 수 있다.

| 논리 0 | 논리 1 |

|---|---|

오픈 컬렉터는 단일 전원 사용, 더 많은 전류 필요, 와이어드 AND 구현 등의 경우에 사용되며, 마이크로프로세서에서 다른 칩과의 통신(예: I2C)에 활용된다.

4. 4. 풀업 및 풀다운

디지털 회로는 원칙적으로 High 또는 Low의 전압 인가가 되어 있어야 한다. High와 Low의 중간 전압은 내부 상태를 불안정하게 만들거나 전력 소비를 증가시킨다. Low보다 낮은 전압이나 High보다 높은 전압은 회로를 파괴할 수 있다.[59]일반적으로 디지털 회로의 입력 단자는 내부 임피던스가 높아, 연결되지 않은 상태에서는 주변의 정전기나 전자기 유도에 의해 예상치 못한 전압이 인가될 수 있다. 이러한 상태를 "플로팅"이라고 한다.[59]

이러한 문제를 해결하기 위해 수 kΩ ~ 수백 kΩ의 저항을 전원선이나 접지선에 연결한다. 전원선에 연결하는 것을 "풀업", 접지선에 연결하는 것을 "풀다운"이라고 한다. 풀업 또는 풀다운된 입력 단자는 출력 단자가 연결되지 않은 상태에서도 전원 전압이나 접지 전압이 유지된다.[59]

다른 디지털 회로의 출력 단자가 접속되면, 디지털 소자의 출력 회로는 내부 임피던스가 매우 작아 풀업 또는 풀다운에 사용된 저항값은 무시할 수 있게 된다. 풀업 저항값이 너무 크면 플로팅 상태와 비슷해져 전자 유도에 약해지고, 너무 작으면 연결된 출력 소자에 큰 전류가 흘러 소비 전력이 증가하거나 소자가 파손될 수 있다.[59]

신호선이 길 경우, 전자 유도로 인해 이상 전압이 발생할 수 있다. 이때 풀업 저항에 병렬로 다이오드를 연결하여 이상 전압에 의한 전류를 전원선 쪽으로 흘려보내 소자를 보호할 수 있다. 이 다이오드를 "클램프 다이오드"라고 한다.[59]

디지털 회로 설계 시 사용하지 않는 회로의 입력 단자는 반드시 풀업이나 풀다운해야 한다. 최근의 CPU IC는 부품 수를 줄이기 위해 풀업 저항을 내장하는 경우가 많으며, 소프트웨어로 제어 가능한 경우도 있다.[59]

5. 팬 아웃

디지털 회로에서는 하나의 출력 단자에 여러 개의 후단 회로 입력이 연결되는 것이 매우 일반적이다. 출력 단자에 연결된 입력 단자의 수를, 출력 단자를 부채살의 중심으로 비유하여 '''팬아웃'''이라고 한다.[51] 팬 아웃은 하나의 논리 게이트 출력이 구동할 수 있는 다른 논리 게이트 입력의 수를 나타내며, 사용하는 논리 소자 기술에 따라 제한된다.

디지털 회로에서는 전압 값에 따라 정보를 소자에서 소자로 전달하지만, 이때 전기 회로이므로 전류의 흐름이 수반된다. 출력 측 레벨을 L로 하려면 출력 단자가 후단 회로에서 전류를 흡입하고, 출력 측 레벨을 H로 하려면 출력 단자가 후단 회로에 전류를 방출한다.

TTL과 같이 입력 단자에 흘러 들어오거나 입력 단자에서 흘러나가는 전류가 비교적 큰 소자로 회로를 구성하는 경우, 전단의 출력 측 소자의 전류 구동 능력에 따라 팬아웃 수가 제한된다.[51] TTL의 경우, 표준 타입, LS 타입, ALS 타입 등 다양한 타입의 시리즈가 있지만, 그 시리즈 내의 규격에 따라 출력 단자의 구동 능력과 입력 단자가 흡입(또는 방출)하는 전류의 최대값이 규격화되어 있으므로, 같은 시리즈의 IC끼리라면 팬아웃의 제한값은 같아진다. 다른 타입의 시리즈를 조합하여 사용하는 경우에는 각 데이터 시트를 조사하여 연결할 수 있는 개수를 확인해야 한다.

많은 입력에 신호를 분배하기 위한 목적으로, 같은 논리 회로라도 팬아웃 값을 크게 한 회로 소자가 준비되어 있다. 그러한 회로 소자는 논리적으로는 아무것도 하지 않거나, 반전만 하는 단순한 것이 많으며, 버퍼, 버스 버퍼, 드라이버 등이라고 불린다.

CMOS영어형 로직의 경우, 입력 단자는 내부 임피던스가 높게 만들어져 있으므로 정상 상태에서의 전류값은 미미하지만, 많은 입력 단자를 연결하면 각 단자와 배선 부분의 정전용량이 병렬 연결됨에 따라 출력 측에서 본 용량성 부하가 증가한다. 따라서, 출력 측 소자의 구동 능력이 부족하면 H에서 L, L에서 H의 상태 천이에 시간이 걸리게 되어 회로 동작상의 제약이 되므로, 후단에 연결할 수 있는 입력 단자의 개수는 제한된다.

6. 버퍼

버퍼는 신호의 세기를 증폭하거나, 신호 전달 방향을 제어하는 데 사용되는 회로이다.

| G | X | Y |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Z |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| G | X | Y |

|---|---|---|

| 0 | 0(Out) | 0(In) |

| 0 | 1(Out) | 1(In) |

| 1 | 0(In) | 0(Out) |

| 1 | 1(In) | 1(Out) |

| S | X1 | X2 | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

트라이스테이트(tri-state)는 출력을 하이 임피던스(High Impedance)로 만들 수 있는 출력 회로이다.[61] 입력 신호를 그대로 출력하거나 하이 임피던스로 출력할 수 있는 회로를 트라이스테이트 버퍼(tri-state buffer)라고 한다. 회로 기호에서는 버퍼를 나타내는 삼각형 기호와 측면에 출력을 하이 임피던스로 할지 아니면 입력 신호로 할지 결정할 수 있는 신호선이 있는 기호로 표시한다.

출력을 하이 임피던스로 하지 않을 것을 결정하는 입력 신호선은 게이트(gate영어)의 의미로 'G'로 표기하거나, 작동(enable영어)의 의미로 'E', 'EN'으로 표기하기도 한다.[62][63] 또 데이터 버스에서 사용되는 경우 출력 작동(output enable영어)의 약자로 'OE'나 칩 선택(chip select영어)의 약어로 'CS'의 기호를 사용하는 경우도 많다.[64][65]

| G | X | Y |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Z |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

트라이스테이트는 내셔널 세미컨덕터(National Semiconductor)의 상품명으로, 미국에서는 "TRI-STATE"는 상표 등록되어 있다(등록 번호 0941335・2138646).

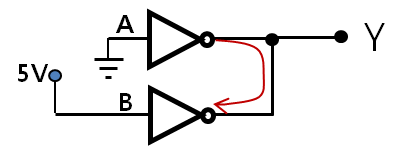

쌍방향 버퍼는 데이터 전송 방향을 제어할 수 있는 버퍼이다. 트라이스테이트 버퍼 2개를 조합하여 데이터 통신 방향을 변경할 수 있다. G가 L일 때는 Y에서 X방향으로, G가 H일 때는 X에서 Y방향으로 데이터가 전송된다.

트라이스테이트 버퍼나 쌍방향 버퍼는 많은 회로가 신호선을 공유하는 데이터 버스나 주소 버스에 널리 사용된다. 데이터 버스의 비트 단위가 되기 쉬운 8 채널 트라이스테이트 버퍼 IC가 대중화되어 자주 사용된다.

데이터 셀렉터(data selector영어)는 여러 입력 신호 중 하나를 선택하여 출력하는 회로이다. 와이어드 오어의 원리를 사용하여, 동일한 트라이스테이트 버퍼를 여러 개 조합하면 복수의 입력 신호 중 하나만 출력하도록 할 수 있다. 데이터 셀렉터는 일반 논리 소자를 이용해 구성하면 (Y ← (S AND X1) OR ((NOT S) AND X2))가 되지만, 트라이스테이트 버퍼를 이용하면 훨씬 간단한 내부 회로로 제작할 수 있다. 두 채널뿐만 아니라 네 채널, 여덟 채널의 데이터 셀렉터도 이 회로를 응용하면 쉽게 제작할 수 있다.

6. 1. 트라이스테이트 버퍼

트라이스테이트(tri-state)는 출력을 하이 임피던스(High Impedance)로 만들 수 있는 출력 회로이다.[61] 입력 신호를 그대로 출력하거나 하이 임피던스로 출력할 수 있는 회로를 트라이스테이트 버퍼(tri-state buffer)라고 한다. 회로 기호에서는 버퍼를 나타내는 삼각형 기호와 측면에 출력을 하이 임피던스로 할지 아니면 입력 신호로 할지 결정할 수 있는 신호선이 있는 기호로 표시한다.출력을 하이 임피던스로 하지 않을 것을 결정하는 입력 신호선은 게이트(gate영어)의 의미로 'G'로 표기하거나, 작동(enable영어)의 의미로 'E', 'EN'으로 표기하기도 한다.[62][63] 또 데이터 버스에서 사용되는 경우 출력 작동(output enable영어)의 약자로 'OE'나 칩 선택(chip select영어)의 약어로 'CS'의 기호를 사용하는 경우도 많다.[64][65]

| G | X | Y |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Z |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

트라이스테이트는 내셔널 세미컨덕터(National Semiconductor)의 상품명으로, 미국에서는 "TRI-STATE"는 상표 등록되어 있다(등록 번호 0941335・2138646).

6. 2. 쌍방향 버퍼

쌍방향 버퍼는 데이터 전송 방향을 제어할 수 있는 버퍼이다. 트라이스테이트 버퍼 2개를 조합하여 데이터 통신 방향을 변경할 수 있다. G가 L일 때는 Y에서 X방향으로, G가 H일 때는 X에서 Y방향으로 데이터가 전송된다.트라이스테이트 버퍼나 쌍방향 버퍼는 많은 회로가 신호선을 공유하는 데이터 버스나 주소 버스에 널리 사용된다. 데이터 버스의 비트 단위가 되기 쉬운 8 채널 트라이스테이트 버퍼 IC가 대중화되어 자주 사용된다.

6. 3. 데이터 셀렉터

데이터 셀렉터(data selector영어)는 여러 입력 신호 중 하나를 선택하여 출력하는 회로이다. 와이어드 오어의 원리를 사용하여, 동일한 트라이스테이트 버퍼를 여러 개 조합하면 복수의 입력 신호 중 하나만 출력하도록 할 수 있다. 데이터 셀렉터는 일반 논리 소자를 이용해 구성하면(Y ← (S AND X1) OR ((NOT S) AND X2))가 되지만, 트라이스테이트 버퍼를 이용하면 훨씬 간단한 내부 회로로 제작할 수 있다. 두 채널뿐만 아니라 네 채널, 여덟 채널의 데이터 셀렉터도 이 회로를 응용하면 쉽게 제작할 수 있다.7. 장점

디지털 회로는 아날로그 회로에 비해 여러 가지 장점을 가지고 있다.[44][56]

디지털 방식으로 표현된 신호는 잡음으로 인한 열화 없이 전송될 수 있다.[44] 예를 들어, 1과 0의 순서로 전송되는 연속적인 오디오 신호는, 전송 과정에서 발생하는 잡음이 1과 0을 식별하는 데 충분하지 않다면, 오류 없이 재구성될 수 있다. 아날로그로 저장된 LP 레코드가 지름 30cm로 재생 시간이 30분인 데 비해, 지름 12cm의 콤팩트 디스크에는 약 1시간 분량의 음악을 녹음할 수 있으며, 그 기록은 약 60억 개의 1과 0으로 구성되어 있다.[56]

디지털 시스템에서는 신호를 나타내는 데 사용되는 이진수의 자릿수를 늘림으로써 더욱 정확한 신호 표현을 얻을 수 있다. 이는 신호를 처리하는 데 더 많은 디지털 회로가 필요하지만, 각 자릿수는 동일한 종류의 하드웨어로 처리되므로 쉽게 확장 가능한 시스템이 된다. 아날로그 시스템에서는 해상도를 높이려면 신호 경로의 각 단계에서 선형성과 잡음 특성을 근본적으로 개선해야 한다.[44]

컴퓨터로 제어되는 디지털 시스템에서는 소프트웨어 수정을 통해 새로운 기능을 추가할 수 있으며, 하드웨어 변경이 필요하지 않다. 종종 이것은 공장 외부에서 제품의 소프트웨어를 업데이트하여 수행할 수 있다. 이러한 방식으로 제품의 설계 오류는 제품이 고객의 손에 들어간 후에도 수정될 수 있다.[44]

정보 저장은 아날로그 시스템보다 디지털 시스템에서 더 쉬울 수 있다. 디지털 시스템의 잡음 내성으로 인해 데이터는 열화 없이 저장하고 검색할 수 있다. 아날로그 시스템에서는 노화와 마모로 인한 잡음이 저장된 정보를 저하시킨다. 디지털 시스템에서는 총 잡음이 특정 수준 이하인 한 정보를 완벽하게 복구할 수 있다.[44] 더 큰 잡음이 존재하는 경우에도, 중복성을 사용하면 너무 많은 오류가 발생하지 않는 한 원래 데이터를 복구할 수 있다.

경우에 따라 디지털 회로는 동일한 작업을 수행하는 데 아날로그 회로보다 더 많은 에너지를 사용하여 더 많은 열을 발생시키므로 히트싱크를 포함하는 등 회로의 복잡성이 증가한다. 휴대용 또는 배터리로 작동되는 시스템에서는 이로 인해 디지털 시스템의 사용이 제한될 수 있다. 예를 들어, 배터리로 작동되는 휴대전화는 종종 저전력 아날로그 프런트 엔드를 사용하여 기지국으로부터의 무선 신호를 증폭하고 튜닝한다. 그러나 기지국은 전력망 전력을 사용하며 전력 소모가 많지만 매우 유연한 소프트웨어 무선을 사용할 수 있다. 이러한 기지국은 새로운 셀룰러 표준에 사용되는 신호를 처리하도록 쉽게 재프로그래밍할 수 있다.[44]

많은 유용한 디지털 시스템은 연속적인 아날로그 신호를 이산적인 디지털 신호로 변환해야 한다. 이로 인해 양자화 오류가 발생한다. 시스템이 원하는 정도의 충실도로 신호를 나타내는 데 충분한 디지털 데이터를 저장하면 양자화 오류를 줄일 수 있다. 나이키스트-섀넌 표본화 정리는 주어진 아날로그 신호를 정확하게 표현하는 데 필요한 디지털 데이터의 양에 대한 중요한 지침을 제공한다.[44]

절벽 효과 때문에 사용자가 특정 시스템이 고장 직전인지, 아니면 고장나기 전에 훨씬 더 많은 잡음을 허용할 수 있는지 알기 어려울 수 있다. 디지털 취약성은 강건성을 위해 디지털 시스템을 설계함으로써 줄일 수 있다. 예를 들어, 패리티 비트 또는 다른 오류 관리 방법을 신호 경로에 삽입할 수 있다. 이러한 방식은 시스템이 오류를 감지한 다음 오류를 수정하거나 데이터의 재전송을 요청하는 데 도움이 된다.[44]

8. 단점

디지털 회로는 아날로그 회로에 비해 다음과 같은 단점을 가질 수 있다.

경우에 따라 디지털 회로는 동일한 작업을 수행하는 아날로그 회로보다 더 많은 에너지를 소비하여 더 많은 열을 발생시킨다.[57] 이는 회로의 복잡성을 증가시키며, 히트싱크를 포함해야 할 수도 있다. 휴대용 또는 배터리로 작동되는 시스템에서는 이로 인해 디지털 시스템의 사용이 제한될 수 있다. 예를 들어, 배터리로 작동되는 휴대전화는 기지국으로부터의 무선 신호를 증폭하고 튜닝하기 위해 저전력 아날로그 프런트 엔드를 사용한다.[57] 반면 기지국은 전력망 전력을 사용하며 전력 소모가 많지만 유연한 소프트웨어 정의 무선을 사용할 수 있다.

대부분의 유용한 디지털 시스템은 연속적인 아날로그 신호를 이산적인 디지털 신호로 변환해야 한다. 이 과정에서 양자화 오차가 발생한다.[57] 표본화 정리는 주어진 아날로그 신호를 정확하게 표현하는 데 필요한 디지털 데이터의 양에 대한 중요한 지침을 제공한다.

일부 시스템에서는 단일 비트 오류가 큰 영향을 미칠 수 있다. 예를 들어, 선형 펄스 코드 변조로 저장된 오디오 데이터에서 단일 비트 오류는 작은 소음을 유발할 수 있지만, 오디오 압축을 사용하는 경우 단일 비트 오류는 훨씬 더 큰 중단을 유발할 수 있다. 절벽 효과로 인해 사용자는 시스템이 고장 직전인지, 아니면 더 많은 잡음을 허용할 수 있는지 알기 어려울 수 있다. 이러한 디지털 취약성은 강건성을 위해 패리티 비트 또는 오류 검출 및 정정과 같은 오류 관리 방법을 신호 경로에 삽입하여 줄일 수 있다.[57]

9. 설계 및 구현

디지털 회로는 일반적으로 논리 게이트라고 하는 작은 전자 회로로 구성되며, 이는 조합 논리를 만드는 데 사용할 수 있다. 각 논리 게이트는 논리 신호에 작용할 때 부울 논리의 함수를 수행하도록 설계된다. 논리 게이트는 일반적으로 하나 이상의 전기적으로 제어되는 스위치, 일반적으로 트랜지스터(하지만 역사적으로는 진공관이 사용되었다)로 만들어진다. 논리 게이트의 출력은 차례로 더 많은 논리 게이트를 제어하거나 공급할 수 있다.

또 다른 형태의 디지털 회로는 조회 테이블(많은 것이 "프로그래머블 논리 디바이스"로 판매되지만 다른 종류의 PLD도 존재한다)로 구성된다. 조회 테이블은 논리 게이트 기반 머신과 동일한 기능을 수행할 수 있지만 배선을 변경하지 않고도 쉽게 재프로그래밍할 수 있다. 즉, 설계자는 배선 배치를 변경하지 않고도 설계 오류를 수정할 수 있다. 따라서 소량 생산품의 경우 프로그래머블 논리 디바이스가 종종 선호되는 솔루션이다. 이러한 디바이스는 일반적으로 전자 설계 자동화 소프트웨어를 사용하는 엔지니어가 설계한다.

집적 회로는 하나의 실리콘 칩에 여러 개의 트랜지스터로 구성되며, 많은 수의 상호 연결된 논리 게이트를 만드는 가장 저렴한 방법이다. 집적 회로는 일반적으로 인쇄 회로 기판에 상호 연결되는데, 이는 전기 부품을 보유하고 구리 도선으로 서로 연결하는 기판이다.

최적의 성능이 필요하지 않은 복잡한 시스템의 디지털 논리를 구현하는 데는 종종 마이크로컨트롤러와 프로그래머블 로직 컨트롤러가 있는 임베디드 시스템이 사용된다. 이러한 시스템은 일반적으로 소프트웨어 엔지니어 또는 전기 기술자들이 래더 로직을 사용하여 프로그래밍한다.

9. 1. 설계 도구

설계자들은 회로의 복잡성을 줄이기 위해 논리적 중복을 최소화하는 여러 방법을 사용하는데, 복잡성이 줄어들면 부품 수와 잠재적 오류가 줄어들어 비용이 절감된다. 이진 결정 다이어그램, 부울 대수, 카르노 맵, 퀸-맥클러스키 알고리즘, 휴리스틱 컴퓨터 방법과 같은 기술을 통해 논리적 중복을 제거할 수 있으며, 이러한 작업은 일반적으로 컴퓨터 지원 설계 시스템 내에서 수행된다.최적의 성능이 필요하지 않은 복잡한 시스템의 디지털 논리를 구현하는 데는 종종 마이크로컨트롤러와 프로그래머블 로직 컨트롤러가 있는 임베디드 시스템이 사용된다. 이러한 시스템은 일반적으로 소프트웨어 엔지니어 또는 전기 기술자들이 래더 로직을 사용하여 프로그래밍한다.

대규모 논리 회로 설계 작업의 상당 부분은 전자 설계 자동화(EDA)의 적용을 통해 자동화되었다. EDA는 많은 경우 단순한 진리표와 같은 기술을 최적화하여 필요한 출력을 생성하는 논리 게이트 수를 줄인 시스템이나 더 작은 참조 테이블을 자동으로 생성한다. 그러한 소프트웨어의 가장 일반적인 예로 에스프레소 휴리스틱 논리 최소화기(Espresso Heuristic Logic Minimizer)가 있다. 대규모 논리 시스템의 최적화는 퀸-맥클러스키 알고리즘 또는 이진 결정 다이어그램을 사용하여 수행할 수 있다. 유전 알고리즘과 어닐링 최적화를 사용한 유망한 실험도 있다.

비용이 많이 드는 엔지니어링 프로세스를 자동화하기 위해 일부 EDA는 상태 머신을 설명하는 상태표를 사용하여 상태 머신의 조합 논리에 대한 진리표 또는 함수표를 자동으로 생성할 수 있다. 상태표는 각 상태와 함께 상태 간의 전이를 제어하는 조건과 관련 출력 신호를 나열하는 텍스트이다.

실제 논리 시스템은 종종 일련의 하위 프로젝트로 설계되며, 이는 ''툴 플로우''를 사용하여 결합된다. 툴 플로우는 일반적으로 스크립팅 언어(소프트웨어 설계 도구를 올바른 순서로 호출할 수 있는 간소화된 컴퓨터 언어)의 도움을 받아 제어된다. 마이크로프로세서와 같은 대규모 논리 시스템의 툴 플로우는 수천 개의 명령어로 구성될 수 있으며 수백 명의 엔지니어의 작업을 결합한다. 툴 플로우를 작성하고 디버깅하는 것은 디지털 설계를 생성하는 회사에서 확립된 엔지니어링 전문 분야이다. 툴 플로우는 일반적으로 논리의 물리적 구조를 설명하는 상세한 컴퓨터 파일 또는 파일 집합으로 끝납니다. 종종 집적 회로 또는 인쇄 회로 기판에 트랜지스터와 와이어를 그리는 방법에 대한 지침으로 구성된다.

툴 플로우의 일부는 시뮬레이션된 논리의 출력을 예상 입력과 비교하여 검증하여 디버깅된다. 테스트 도구는 입력과 출력 집합이 포함된 컴퓨터 파일을 사용하고 시뮬레이션된 동작과 예상 동작 간의 불일치를 강조 표시한다. 입력 데이터가 정확하다고 판단되면 설계 자체의 정확성을 확인해야 한다. 일부 툴 플로우는 먼저 설계를 생성한 다음 설계를 스캔하여 툴 플로우에 대한 호환 가능한 입력 데이터를 생성하여 설계를 확인한다. 스캔된 데이터가 입력 데이터와 일치하면 툴 플로우에서 오류가 발생하지 않았을 가능성이 높다.

기능적 검증 데이터는 일반적으로 ''테스트 벡터''라고 한다. 기능 테스트 벡터는 보존되어 공장에서 새로 구성된 논리가 제대로 작동하는지 테스트하는 데 사용될 수 있다. 그러나 기능 테스트 패턴은 모든 제작 결함을 발견하지 못한다. 생산 테스트는 종종 자동 테스트 패턴 생성 소프트웨어 도구에 의해 설계된다. 이러한 도구는 논리의 구조를 검사하고 특정 잠재적 결함을 대상으로 하는 테스트를 체계적으로 생성하여 테스트 벡터를 생성한다.

설계가 존재하고 검증되고 테스트 가능하게 되면 종종 제조 가능하도록 처리해야 한다. 최신 집적 회로는 감광제를 노출하는 데 사용되는 빛의 파장보다 작은 특징을 가지고 있다. 제조를 위한 설계된 소프트웨어는 개방 회로를 제거하고 마스크의 대비를 향상시키기 위해 간섭 패턴을 노출 마스크에 추가한다.

9. 2. 표현 방식

디지털 회로의 입력-출력 관계는 진리표로 나타낼 수 있으며, 이와 동등한 상위 레벨 회로는 논리 게이트를 사용하여 표현할 수 있다.[45] 하위 레벨에서는 전자 스위치(일반적으로 트랜지스터)의 등가 회로를 사용한다.[45]대부분의 디지털 시스템은 조합 논리 회로와 순차 시스템으로 나뉜다.[45] 조합 논리 회로의 출력은 현재 입력에만 의존하는 반면, 순차 논리 회로는 일부 출력이 입력으로 다시 공급되므로 현재 입력뿐만 아니라 과거 입력에도 의존한다.[45] 순차 회로는 유한 상태 기계로 설계하는 경우가 많다.[45]

순차 회로는 "동기식" 순차 시스템과 "비동기식" 순차 시스템의 두 가지 하위 범주로 나뉜다.[45] 동기식 시스템은 클럭 신호에 따라 상태가 변경되는 반면, 비동기식 시스템은 입력이 변경될 때마다 변경이 전파된다.[45] 동기 순차 시스템은 플립플롭을 사용하여 만들어진다.[45]

회로의 복잡성을 줄이기 위해 기능을 최소화하고 단순화하는 경우가 많으며, 이를 통해 오류를 줄이고 비용을 절감할 수 있다.[45] 회로 단순화 알고리즘으로는 CAD 시스템에 통합된 Espresso heuristic logic minimizer, 결정 트리, 자동화된 콰인-맥클러스키 방법, 진리표, 카르노 맵, 부울 대수 등이 사용된다.[45]

1980년대에는 FIFO 방식 동기 논리를 사용하여 대부분의 동기식 레지스터 전달 기계를 비동기 설계로 변환할 수 있다는 사실이 발견되었다. 많은 디지털 회로는 데이터 플로우 머신으로 볼 수 있으며, 이 경우 동기식 레지스터 전달 레벨로 설계할 수 있고, VHDL이나 Verilog와 같은 하드웨어 기술 언어를 사용할 수 있다.

9. 3. 동기식 및 비동기식 시스템

순차 논리 회로는 크게 두 가지로 분류할 수 있는데, 클럭 신호로 구동하여 상태가 동시에 변화하는 클럭 동기 시스템과 입력의 변화에 따라 변화가 전파되는 비동기 시스템이 있다. 동기 순차 회로는 플립플롭과 같은 비동기 회로로 구성되어 있으며, 클럭 신호에 맞춰 상태가 변화하도록 되어 있으므로 타이밍 마진 설계에 주의가 필요하다.

동기식 시스템은 클럭 신호에 맞춰 상태가 변경되는 반면, 비동기식 시스템은 입력 변화에 따라 상태가 변경된다. 동기식 순차 상태 기계를 구현하는 일반적인 방법은 조합 회로 부분과 "상태 레지스터"라고 불리는 플립플롭 그룹으로 나누는 것이다. 클럭 신호 펄스마다 상태 레지스터는 조합 회로의 이전 상태에서 생성된 피드백을 포착하고, 상태 기계의 조합 회로 부분에 대한 불변의 입력으로 피드백한다. 클럭 주파수를 얼마나 높일 수 있는지는 조합 회로에서 가장 시간이 오래 걸리는 경로에 따라 결정된다.

반면 비동기 시스템은 모든 가능한 타이밍을 고려해야 하며, 모든 상태를 고려해야 하므로 설계가 어렵다. 일반적인 방법으로는 각 상태가 존재할 수 있는 최단 시간과 최장 시간의 표를 작성하고, 그러한 상태의 수가 최소가 되도록 회로를 조정하여 전체가 주기적으로 "자기 재동기"라고 불리는 호환 상태에 들어가 대기하도록 한다. 그렇게 주의 깊게 설계하지 않으면 쉽게 불안정한 상태가 되고, 개별 전자 부품의 값의 허용 오차 등에 기인하는 지연이 누적되어 예측할 수 없는 결과가 된다. 어떤 종류의 회로는 본질적으로 비동기적이며(플립플롭으로 구성된 동기화기, 스위치 디바운서, 조정 회로, 외부에서 비동기적인 신호가 동기 순차 회로로 들어오는 회로 등), 이러한 설계가 필수적이다.

2005년 현재, 동기 설계가 설계 및 검증이 용이하기 때문에 디지털 시스템의 대부분이 동기 설계로 이루어져 있다. 설계/시뮬레이션 도구도 비동기 회로용은 거의 존재하지 않는다. 하지만 잘 설계하면 클럭 주파수에 제한되지 않는 만큼 비동기 방식이 더 우수하다고 알려져 있다. 초기 비동기식 디지털 컴퓨터의 예로는 1951년 Jacobs Instrument Company에서 제조한 Jaincomp-B1이 있다.[46]

9. 4. 레지스터 전달 시스템

레지스터 전달 시스템은 레지스터 간의 데이터 흐름을 기반으로 설계되는 시스템이다. 많은 디지털 시스템은 데이터 흐름 기계이며, 일반적으로 동기식 레지스터 전달 논리를 사용하여 설계된다. 이러한 시스템은 하드웨어 기술 언어(VHDL, Verilog 등)로 작성된다.레지스터 전달 논리에서 이진수는 플립플롭의 그룹인 레지스터에 저장된다. 순차 상태 머신은 각 레지스터가 입력으로부터 새로운 데이터를 수락하는 시기를 제어하며, 각 레지스터의 출력은 그 수를 다른 계산으로 전달하는 와이어 번들인 ''버스''이다. 계산은 조합 논리의 일부이며, 각 계산에는 출력 버스가 있고, 이러한 버스는 여러 레지스터의 입력에 연결될 수 있다. 레지스터는 입력에 멀티플렉서를 가지므로 여러 버스 중 하나의 수를 저장할 수 있다.

1980년대에 일부 연구자들은 거의 모든 동기식 레지스터 전달 머신을 선입선출 동기화 논리를 사용하여 비동기식 설계로 변환할 수 있음을 발견했다. 이 방식에서 디지털 머신은 데이터 흐름의 집합으로 특징지어지며, 흐름의 각 단계에서 동기화 회로는 해당 단계의 출력이 유효한 시기를 결정하고 다음 단계에 이러한 출력을 언제 사용할지 지시한다.

컴퓨터는 가장 범용적인 레지스터 전달 논리 기계이다. 컴퓨터의 제어 장치는 일반적으로 마이크로시퀀서에서 마이크로프로그램을 실행하도록 설계되어 있다. 마이크로프로그램은 피아노롤과 유사하며, 마이크로프로그램의 각 비트는 산술 논리 연산 장치나 메모리 또는 컴퓨터의 다른 부분을 제어한다.

9. 5. 컴퓨터 설계

컴퓨터는 가장 일반적인 레지스터 전달 논리 기계이다. 이것은 기본적으로 자동적인 2진수 주판이다. 컴퓨터의 제어 장치는 일반적으로 마이크로프로그램에 의해 실행되는 마이크로시퀀서로 설계된다. 마이크로프로그램은 플레이어 피아노 롤과 매우 유사하며, 각 테이블 항목은 컴퓨터를 제어하는 모든 비트의 상태를 명령한다. 그런 다음 시퀀서가 계산하고, 계산은 마이크로프로그램이 포함된 메모리 또는 조합 논리 기계의 주소를 지정한다. 마이크로프로그램의 비트는 산술 논리 장치, 메모리 및 마이크로시퀀서 자체를 포함한 컴퓨터의 다른 부분을 제어한다. 이러한 방식으로 컴퓨터 제어를 설계하는 복잡한 작업은 훨씬 더 단순한 논리 기계의 집합을 프로그래밍하는 더 간단한 작업으로 단순화된다.

거의 모든 컴퓨터는 동기식이다. 그러나 비동기식 컴퓨터도 제작되었다. 한 가지 예로 ASPIDA DLX 코어가 있다.[47] 또 다른 예는 ARM Holdings에서 제공되었다.[48]

10. 최근 개발 동향

2009년, 연구원들은 메모리스터(memristor)가 매우 적은 공간과 전력을 사용하여 익숙한 CMOS 반도체 공정을 이용하여 부울 상태 저장을 구현하고 완전한 논리 계열을 제공할 수 있다는 것을 발견했다.[52]

초전도성(superconductivity)의 발견은 트랜지스터 대신 조셉슨 접합(Josephson junction)을 사용하는 RSFQ(래피드 싱글 플럭스 퀀텀/Rapid Single Flux Quantum영어) 회로 기술의 개발을 가능하게 했다.[52] 최근에는 비선형 광학 요소(nonlinear optical elements)를 사용하여 디지털 정보를 처리할 수 있는 순수 광컴퓨팅(optical computing) 시스템을 구축하려는 시도가 이루어지고 있다.

참조

[1]

서적

The essentials of computer organization and architecture

https://archive.org/[...]

Jones & Bartlett Publishers

[2]

서적

Letter, Peirce to A. Marquand

https://books.google[...]

1886

[3]

웹사이트

Approximate Desktop & Notebook Power Usage

https://web.archive.[...]

University of Pennsylvania

2009-06-20

[4]

서적

The Industrialization of Intelligence: Mind and Machine in the Modern Age

https://books.google[...]

Routledge, Taylor & Francis Group

2018

[5]

웹사이트

Claude Shannon: The Father of Information Theory

https://www.historyo[...]

2021-06-05

[6]

뉴스

A Computer Pioneer Rediscovered, 50 Years On

https://www.nytimes.[...]

1994-04-20

[7]

서적

The Design of CMOS Radio-Frequency Integrated Circuits

https://web.stanford[...]

Cambridge University Press

2003

[8]

서적

Nanoelectronics: Materials, Devices, Applications, 2 Volumes

https://books.google[...]

John Wiley & Sons

2017

[9]

서적

A History of Manchester Computers

The British Computer Society

[10]

특허

Oxidation of semiconductive surfaces for controlled diffusion

https://patents.goog[...]

[11]

학술지

Surface Protection and Selective Masking during Diffusion in Silicon

https://iopscience.i[...]

1957

[12]

서적

Advanced Materials Innovation: Managing Global Technology in the 21st century

https://books.google[...]

John Wiley & Sons

2016

[13]

서적

Makers of the Microchip: A Documentary History of Fairchild Semiconductor

https://books.google[...]

MIT Press

2010

[14]

서적

ULSI Process Integration III: Proceedings of the International Symposium

https://books.google[...]

The Electrochemical Society

2003

[15]

서적

History of Semiconductor Engineering

Springer Science & Business Media

2007

[16]

특허

Method of Manufacturing Semiconductor Devices

1959-05-01

[17]

특허

Semiconductor device

1960-05-15

[18]

학술지

The mechanisms for silicon oxidation in steam and oxygen

https://linkinghub.e[...]

1960-07-01

[19]

서적

Silicon materials science and technology

The Electrochemical Society

1998

[20]

서적

History of Semiconductor Engineering

Springer Science & Business Media

2007

[21]

서적

To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology

https://books.google[...]

Johns Hopkins University Press

2007

[22]

학술지

Silicon-silicon dioxide field induced surface devices

1960

[23]

웹사이트

1960 – Metal Oxide Semiconductor (MOS) Transistor Demonstrated

https://www.computer[...]

Computer History Museum

[24]

학술지

Silicon-Silicon Dioxide Surface Device

https://doi.org/10.1[...]

1961

[25]

서적

History of Semiconductor Engineering

Springer-Verlag Berlin Heidelberg

2007

[26]

웹사이트

The Chip that Jack Built

http://www.ti.com/co[...]

Texas Instruments

2008

[27]

학술지

Through-Silicon Via (TSV)

2009

[28]

웹사이트

Tortoise of Transistors Wins the Race - CHM Revolution

https://www.computer[...]

[29]

뉴스

Transistors Keep Moore's Law Alive

https://www.eetimes.[...]

2018-12-12

[30]

잡지

Applying MOSFETs to Today's Power-Switching Designs

https://www.electron[...]

2016-05-23

[31]

서적

Digital electronics and logic design

PHI Learning Pvt. Ltd.

2002

[32]

서적

Computer Network Security

Springer Science & Business Media

2005

[33]

서적

2000 Solved Problems in Digital Electronics

https://books.google[...]

Tata McGraw-Hill Education

2005

[34]

서적

Studies of InAIAs/InGaAs and GaInP/GaAs heterostructure FET's for high speed applications

https://books.google[...]

University of Michigan

1992

[35]

서적

Power MOSFETS: theory and applications

https://books.google[...]

Wiley

1989

[36]

웹사이트

Who Invented the Transistor?

https://www.computer[...]

2019-07-20

[37]

서적

RF and Microwave Passive and Active Technologies

https://books.google[...]

CRC Press

2018

[38]

논문

Metal-Oxide-Semiconductor Technology

1973

[39]

잡지

Intel enters billion-transistor processor era

http://www.eetimes.c[...]

2005-10-14

[40]

웹사이트

13 Sextillion & Counting: The Long & Winding Road to the Most Frequently Manufactured Human Artifact in History

https://www.computer[...]

2020-10-12

[41]

서적

RF and Microwave Passive and Active Technologies

https://books.google[...]

CRC Press

2018

[42]

논문

The wireless revolution

1991-11

[43]

뉴스

The wireless revolution

https://www.economis[...]

1999-01-21

[44]

서적

The Art of Electronics 2nd Ed.

Cambridge University Press

[45]

서적

Digital Electronics Principles, Devices and Applications

John Wiley & Sons Ltd

2007

[46]

웹사이트

Pentagon symposium: Commercially Available General Purpose Electronic Digital Computers of Moderate Price

http://www.ed-thelen[...]

1952-05-14

[47]

웹사이트

ASODA sync/async DLX Core

http://opencores.org[...]

2014-09-05

[48]

웹사이트

ARM Offers First Clockless Processor Core

http://www.eetimes.c[...]

UBM Tech (Universal Business Media)

2014-09-05

[49]

서적

Fundamentals of Digital Logic with VHDL Design

Mc Graw Hill

2009

[50]

문서

MIL-HDBK-217F notice 2, section 5.3

[51]

서적

Digital and Microprocessor Fundamentals: Theory and Application

Pearson/Prentice Hall

2002

[52]

논문

Stateful implication logic with memristors

2009

[53]

웹사이트

디지털 회로

#E6.94.B9.E8.A8.82.E[...]

2024-03-10

[54]

문서

交流파에 대한 위상차, 전류 기반 등 다양한 가능성

[55]

문서

허용 범위와 준안정 상태의 가능성

[56]

서적

The Art of Electronics

Cambridge University Press

1989

[57]

문서

증폭과 동조의 순서 및 다양한 구성

[58]

문서

TTL과 CMOS 호환 로직 IC

[59]

문서

병렬 저항 연결과 전류 흐름

[60]

용어

high-impedance

[61]

용어

three-state

[62]

용어

gate

[63]

용어

enable

[64]

용어

output enable

[65]

용어

chip select

[66]

서적

Fundamentals of Digital Logic with VHDL Design

Mc Graw Hill

2009

[67]

문서

MIL-HDBK-217F notice 2, section 5.3 및 2010년 이후의 MTBF 향상

[68]

서적

Digital and Microprocessor Fundamentals: Theory and Application

Pearson/Prentice Hall

2002

[69]

서적

The essentials of computer organization and architecture

https://archive.org/[...]

Jones & Bartlett Publishers

2006

[70]

문서

Vcc 전원 전압 범위 (4.75V ~ 5.25V)

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com