직접 메모리 접근

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

직접 메모리 접근(DMA)은 CPU의 관여 없이 주변 장치가 시스템 메모리에 직접 접근하여 데이터를 전송하는 기술이다. DMA는 DMA 컨트롤러를 사용하거나 버스 마스터링을 통해 구현될 수 있으며, 버스트 모드, 사이클 도용 모드, 투명 모드 등 다양한 동작 모드를 지원한다. DMA는 오버런, 캐시 일관성 문제, 물리 메모리 페이지 경계 문제, 인터럽트 증가 등 사용 시 주의해야 할 사항이 있으며, ISA, PCI, I/OAT, DDIO, AHB, Cell 등 다양한 시스템에서 활용된다.

DMA(Direct Memory Access, 직접 메모리 접근)를 사용하면 고속 데이터 전송이 가능해져 컴퓨터의 성능을 종합적으로 향상시킬 수 있다.[20] DMA가 있으면 CPU는 데이터 전송 작업을 DMAC(DMA 컨트롤러)에 맡기고 그 시간을 CPU만이 할 수 있는 작업에 사용할 수 있다.[20][21]

DMA를 사용하면 고속 데이터 전송이 가능해져 컴퓨터의 성능을 종합적으로 향상시킬 수 있다[20]。 DMA가 있으면 CPU는 데이터 전송 작업을 DMAC에 맡기고 그 시간을 CPU만이 할 수 있는 작업에 사용할 수 있다[20][21]。

2. 이론

하지만, DMA는 하나뿐인 버스를 CPU와 나누어 사용하기 때문에 버스 사용 권한 조정이 필요하다.[20] 이 버스 사용 권한 조정은 영어로 "버스 아비트레이션(Bus Arbitration)"이라고 하며, "버스 권한 조정"으로 번역된다.[20]

DMA에서의 데이터 전송은 일반적으로 DMAC가 수행한다. CPU는 DMAC에 데이터의 전송원, 전송 대상, 전송 모드, 데이터 수 등을 지정하고, 그 후에 전송 시작 트리거를 보내기만 하면 된다.[22][20] 트리거를 보내면 CPU는 다른 작업을 시작할 수 있다.[22] DMAC는 데이터 전송 작업을 완료하면 CPU에 인터럽트를 걸어 전송 종료를 알린다.[20] 또한 데이터 전송에서 오류가 발생한 경우에도 CPU에 인터럽트를 걸어 알린다.[22]

과거의 ISA 버스 방식에서는 CPU가 마더보드의 칩셋에 내장된 DMAC에 명령을 보내는 방식이었다. 현대의 PCI 버스에서는 "Bus mastering DMA" 즉, I/O 기기 측에서 PCI 버스의 제어를 맡아 DMA 전송을 모두 관장하는 방식이 채택되고 있다. 한편, 임베디드 시스템에서는 SoC 내에서 버스에 직결된 DMAC가 SoC 내의 버스를 조작하여 DMA를 실현하는 경우가 있다. 또한, 필요한 전송 성능이나 허용 가능한 소비 전력 등의 사용 조건에 따라 여러 개의 버스를 상황에 맞게 사용하는 경우가 있는데, 이 경우 DMAC도 각 버스에 대응하는 것을 선택할 필요가 있다.

네트워크 패킷 전송이나 음악 재생, 비디오 배포 등과 같은 경우에는 지속적인 읽기가 필요하며, DMA는 전용 내장 칩으로 사용된다. 또한 DMA는 멀티 코어에서도 클러스터링에서도 효과를 발휘한다. 이 경우, DMA 통신의 상태 알림 핀으로 수신 상태를 나타내는 HOLD 핀과, 전송 상태를 나타내는 HLDA 핀이 존재한다.

DMA 사용을 전제로 하는 경우, 데이터 버스의 비트 폭을 반드시 CPU의 데이터 비트 폭에 맞출 필요는 없다. 특히 데이터 버스의 비트 폭을 CPU의 데이터 비트 폭보다 넓게 함으로써 CPU를 경유하는 것보다 더 광대역의 데이터 전송이 가능해진다. 예시로, AXI 버스는 2003년 릴리스된 초판부터 최대 1024비트 폭의 데이터 버스를 지원한다. 당시 CPU 데이터 폭은 32비트가 주류였으며, AXI 버스와 자주 조합되는 ARM 아키텍처에서 AArch64가 발표되기 8년 전의 일이었다.

2. 1. 서드파티 DMA (Third-party DMA)

표준 DMA (서드파티 DMA)는 DMA 컨트롤러를 사용한다. DMA 컨트롤러는 메모리 주소를 생성하고 메모리 읽기 또는 쓰기 사이클을 초기화할 수 있다. 여기에는 메모리 주소 레지스터, 바이트 카운트 레지스터와 하나 이상의 레지스터들을 포함하는 일부 하드웨어 레지스터들이 포함된다.[32] DMA 컨트롤러의 특징에 따라 컨트롤 레지스터들은 원본, 대상, 전송 방향, 전송 크기 단위, 버스트 당 전송 바이트 수의 조합을 지정할 수 있다.[1]

서드파티 DMA는 DMA 컨트롤러를 사용하며, 이는 메모리 주소를 생성하고 메모리 읽기 또는 쓰기 사이클을 시작할 수 있다. 여기에는 CPU가 쓰고 읽을 수 있는 여러 개의 하드웨어 레지스터가 포함되어 있으며, 여기에는 메모리 주소 레지스터, 바이트 수 레지스터, 하나 이상의 제어 레지스터가 포함된다. DMA 컨트롤러가 제공하는 기능에 따라 이러한 제어 레지스터는 소스, 대상, 전송 방향(I/O 장치에서 읽기 또는 I/O 장치에 쓰기), 전송 단위의 크기 및/또는 한 번의 버스트로 전송할 바이트 수를 조합하여 지정할 수 있다.[1]

입력, 출력 또는 메모리 간 작업을 수행하기 위해, 호스트 프로세서는 전송할 워드 수와 사용할 메모리 주소의 수를 사용하여 DMA 컨트롤러를 초기화한다. 그런 다음 CPU는 주변 장치에 데이터 전송을 시작하도록 명령한다. 그 후 DMA 컨트롤러는 시스템 메모리에 주소와 읽기/쓰기 제어 라인을 제공한다. 주변 장치와 메모리 간에 데이터 바이트를 전송할 준비가 될 때마다 DMA 컨트롤러는 전체 데이터 블록이 전송될 때까지 내부 주소 레지스터를 증가시킨다.

서드파티 DMA를 사용하는 버스의 몇 가지 예로는 PATA, USB (USB4 이전) 및 SATA가 있다. 그러나 해당 호스트 컨트롤러는 버스 마스터링을 사용한다.

DMA를 사용하면 고속 데이터 전송이 가능해져 컴퓨터의 성능을 종합적으로 향상시킬 수 있다.[20] DMA가 있으면 CPU는 데이터 전송 작업을 DMAC에 맡기고 그 시간을 CPU만이 할 수 있는 작업에 사용할 수 있다.[20][21]

단, DMA는 하나뿐인 버스를 CPU와 나누어 사용하기 때문에 버스 사용 권한 조정이 필요하다.[20] 이 버스 사용 권한 조정은 영어로 "버스 아비트레이션(Bus Arbitration)"이라고 하며, "버스 권한 조정"으로 번역된다.[20] →#버스 아비트레이션

DMA에서의 데이터 전송은 일반적으로 DMAC가 수행한다. CPU는 DMAC에 데이터의 전송원, 전송 대상, 전송 모드, 데이터 수 등을 지정하고, 그 후에 전송 시작 트리거를 보내기만 하면 된다.[22][20] 트리거를 보내면 CPU는 다른 작업을 시작할 수 있다.[22] DMAC 측은 데이터 전송 작업을 완료하면 CPU에 인터럽트를 걸어 전송 종료를 알린다.[20] 또한 데이터 전송에서 오류가 발생한 경우에도 CPU에 인터럽트를 걸어 알린다.[22]

과거의 ISA 버스 방식에서는 CPU가 마더보드의 칩셋에 내장된 DMAC에 명령을 보내는 방식이었다. 현대의 PCI 버스에서는 "Bus mastering DMA" 즉, I/O 기기 측에서 PCI 버스의 제어를 맡아 DMA 전송을 모두 관장하는 방식이 채택되고 있다. 한편, 임베디드 시스템에서는 SoC 내에서 버스에 직결된 DMAC가 SoC 내의 버스를 조작하여 DMA를 실현하는 경우가 있다. 또한, 필요한 전송 성능이나 허용 가능한 소비 전력 등의 사용 조건에 따라 여러 개의 버스를 상황에 맞게 사용하는 경우가 있는데, 이 경우 DMAC도 각 버스에 대응하는 것을 선택할 필요가 있다.

네트워크 패킷 전송이나 음악 재생, 비디오 배포 등과 같은 경우에는 지속적인 읽기가 필요하며, DMA는 전용 내장 칩으로 사용된다. 또한 DMA는 멀티 코어에서도 클러스터링에서도 효과를 발휘한다. 이 경우, DMA 통신의 상태 알림 핀으로 수신 상태를 나타내는 HOLD 핀과, 전송 상태를 나타내는 HLDA 핀이 존재한다.

DMA 사용을 전제로 하는 경우, 데이터 버스의 비트 폭을 반드시 CPU의 데이터 비트 폭에 맞출 필요는 없다. 특히 데이터 버스의 비트 폭을 CPU의 데이터 비트 폭보다 넓게 함으로써 CPU를 경유하는 것보다 더 광대역의 데이터 전송이 가능해진다. 예시로, AXI 버스는 2003년 릴리스된 초판부터 최대 1024비트 폭의 데이터 버스를 지원한다. 당시 CPU 데이터 폭은 32비트가 주류였으며, AXI 버스와 자주 조합되는 ARM 아키텍처에서 AArch64가 발표되기 8년 전의 일이었다.

2. 2. 버스 마스터링 DMA (First-party DMA)

버스 마스터링 시스템(First-party DMA System)에서 CPU와 주변 장치는 각각 메모리 버스 통제권을 얻을 수 있다. 버스 마스터가 될 수 있는 주변장치는 필요에 따라 메모리 주소와 제어 신호를 제공받아 CPU를 거치지 않고 시스템 메모리에 직접 쓸 수 있다.[20]

버스 마스터링 시스템은 제1자 DMA 시스템이라고도 하며, CPU와 주변 장치가 각각 메모리 버스 제어 권한을 가질 수 있다. 주변 장치가 버스 마스터가 될 수 있는 경우, CPU의 관여 없이 시스템 메모리에 직접 쓸 수 있으며, 필요한 메모리 주소와 제어 신호를 제공한다. 버스 충돌이 발생하지 않도록 프로세서를 홀드 상태로 만드는 몇 가지 조치가 제공되어야 한다.

DMA를 사용하면 고속 데이터 전송이 가능해져 컴퓨터의 성능을 종합적으로 향상시킬 수 있다.[20]。 DMA가 있으면 CPU는 데이터 전송 작업을 DMAC에 맡기고 그 시간을 CPU만이 할 수 있는 작업에 사용할 수 있다.[20][21]。

단, DMA는 하나뿐인 버스를 CPU와 나누어 사용하기 때문에 버스 사용 권한 조정이 필요하다.[20]。 이 버스 사용 권한 조정은 영어로 "버스 아비트레이션(Bus Arbitration)"이라고 하며, "버스 권한 조정"으로 번역된다.[20]。

과거의 ISA 버스 방식에서는 CPU가 마더보드의 칩셋에 내장된 DMAC에 명령을 보내는 방식이었다. 현대의 PCI 버스에서는 "Bus mastering DMA" 즉, I/O 기기 측에서 PCI 버스의 제어를 맡아 DMA 전송을 모두 관장하는 방식이 채택되고 있다. 한편, 임베디드 시스템에서는 SoC 내에서 버스에 직결된 DMAC가 SoC 내의 버스를 조작하여 DMA를 실현하는 경우가 있다.

3. 동작 모드

DMA는 하나뿐인 버스를 CPU와 나누어 사용하기 때문에 버스 사용 권한 조정이 필요하다[20]。 이 버스 사용 권한 조정을 "버스 아비트레이션(Bus Arbitration)"이라고 한다[20]。

DMA에서의 데이터 전송은 일반적으로 DMAC가 수행한다. CPU는 DMAC에 데이터의 전송원, 전송 대상, 전송 모드, 데이터 수 등을 지정하고, 그 후에 전송 시작 트리거를 보내기만 하면 된다[22][20]。 DMAC 측은 데이터 전송 작업을 완료하면 CPU에 인터럽트를 걸어 전송 종료를 알린다[20]。

과거의 ISA 버스 방식에서는 CPU가 마더보드의 칩셋에 내장된 DMAC에 명령을 보내는 방식이었다. 현대의 PCI 버스에서는 "Bus mastering DMA" 즉, I/O 기기 측에서 PCI 버스의 제어를 맡아 DMA 전송을 모두 관장하는 방식이 채택되고 있다.

네트워크 패킷 전송이나 음악 재생, 비디오 배포 등과 같은 경우에는 지속적인 읽기가 필요하며, DMA는 전용 내장 칩으로 사용된다. 또한 DMA는 멀티 코어에서도 클러스터링에서도 효과를 발휘한다.

DMA 사용을 전제로 하는 경우, 데이터 버스의 비트 폭을 반드시 CPU의 데이터 비트 폭에 맞출 필요는 없다. 특히 데이터 버스의 비트 폭을 CPU의 데이터 비트 폭보다 넓게 함으로써 CPU를 경유하는 것보다 더 광대역의 데이터 전송이 가능해진다.

DMA의 버스 아비트레이션 방식에는 '''라운드 로빈'''이 있다. 라운드 로빈은 버스 제어권을 순서대로 양도하는 방식이다.

; 투명 모드 (Transparent mode)

: 투명 모드는 데이터 블록을 전송하는 데 가장 많은 시간이 소요되지만, 전반적인 시스템 성능 측면에서 가장 효율적인 모드이다. 투명 모드에서 DMA 컨트롤러는 CPU가 시스템 버스를 사용하지 않는 연산을 수행할 때만 데이터를 전송한다.

3. 1. 버스트 모드 (Burst mode)

버스트 모드에서는 전체 데이터 블록이 하나의 연속된 시퀀스로 전송된다. DMA 컨트롤러가 CPU로부터 시스템 버스 접근을 허락받으면, CPU에게 시스템 버스 제어권을 다시 넘겨주기 전에 데이터 블록의 모든 데이터를 전송한다.[23] 이 모드는 "블록 전송 모드"라고도 불린다.[24]

CPU로부터 메모리 버스 제어를 넘겨받아 데이터를 일시에 전송하는 방법으로,[24] CPU는 비교적 오랜 기간 동안 비활성화된다.

3. 2. 사이클 도용 모드 (Cycle stealing mode)

사이클 도용 모드는 CPU가 비활성화되어서는 안 되는 시스템에서 사용된다. 사이클 도용 모드에서 DMA 컨트롤러는 버스 요청(BR) 신호와 버스 허가(BG) 신호를 이용하여 시스템 버스 접근을 얻는다. 이 두 신호는 CPU와 DMA 컨트롤러 사이의 인터페이스를 제어한다. 사이클 도용 모드에서는 1바이트의 데이터를 전송한 뒤 BG 신호를 통해 CPU로부터 얻은 시스템 버스 제어권이 해제된다. 전체 블록이 전송될 때까지 BR을 통하여 시스템 버스 제어권을 요청하며 요청당 1바이트의 데이터를 전송한다.[2]

DMA 컨트롤러는 지속적으로 시스템 제어권을 얻고 해제하면서 실질적으로 명령과 데이터 전송을 교차 배치한다. CPU가 명령을 처리하면 DMA 컨트롤러는 하나의 데이터 값을 전송하는 방식이다. 사이클 도용 모드의 데이터 블록 전송 속도는 버스트 모드만큼 빠르지 않지만, CPU가 버스트 모드만큼 길게 대기하지 않는다. 사이클 도용 모드는 데이터를 실시간으로 모니터링해야 하는 컨트롤러에 유용하다.[2]

사이클 스틸 모드 DMA는 CPU로부터 메모리 버스 제어를 넘겨받아 1~2 워드씩 전송하는 방법이다.[24] CPU는 틈 없이 메모리 버스를 이용한다고 할 수 없으므로, CPU가 처리를 진행하는 것과 병행하여 데이터 전송이 가능하다.

3. 3. 투명 모드 (Transparent mode)

투명 모드는 데이터 블록을 전송하는 데 가장 많은 시간이 소요되지만, 전반적인 시스템 성능 측면에서 가장 효율적인 모드이다. 투명 모드에서 DMA 컨트롤러는 CPU가 시스템 버스를 사용하지 않는 연산을 수행할 때만 데이터를 전송한다. 투명 모드의 주요 장점은 CPU가 프로그램 실행을 중단하지 않고 DMA 전송이 시간 측면에서 자유롭다는 것이며, 단점은 하드웨어가 CPU가 시스템 버스를 사용하지 않을 때를 결정해야 하므로 복잡할 수 있다는 것이다. 이는 "은닉 DMA 데이터 전송 모드"라고도 한다.

4. 버스 중재 (Bus Arbitration)

DMA는 하나뿐인 버스를 CPU와 나누어 사용하기 때문에 버스 사용 권한 조정이 필요하다[20]。 이 버스 사용 권한 조정을 "버스 아비트레이션(Bus Arbitration)"이라고 하며, "버스 권한 조정"으로 번역된다[20]。

DMA의 버스 중재 방식에는 '''라운드 로빈''', '''사이클 스틸''', '''버스트''' 방식이 있다.[23]

- '''라운드 로빈'''은 버스 제어권을 순서대로 양도하는 방식이다.

- '''사이클 스틸''' 방식에서는 CPU가 메모리에 접근하지 않는 버스 사이클 동안 DMA가 버스를 사용한다.

- '''버스트''' 방식은 일정 시간 동안 하나의 버스 마스터가 버스 제어권을 점유하는 방식으로, 우선순위가 높은 데이터를 빠르게 전송할 때 사용한다.

과거의 ISA 버스 방식에서는 CPU가 마더보드의 칩셋에 내장된 DMAC에 명령을 보내는 방식이었다. 현대의 PCI 버스에서는 "Bus mastering DMA" 즉, I/O 기기 측에서 PCI 버스의 제어를 맡아 DMA 전송을 모두 관장하는 방식이 채택되고 있다. 한편, 임베디드 시스템에서는 SoC 내에서 버스에 직결된 DMAC가 SoC 내의 버스를 조작하여 DMA를 실현하는 경우가 있다.

4. 1. 라운드 로빈 (Round Robin)

DMA(직접 메모리 접근)의 버스 아비트레이션 방식 중 하나인 '''라운드 로빈'''은 버스 제어권을 순서대로 양도하는 방식이다.[23]4. 2. 사이클 스틸 (Cycle Stealing)

'''사이클 스틸'''(Cycle Stealing) 모드는 CPU가 한 번에 많은 데이터를 전송하는 데 필요한 시간 동안 비활성화되면 안 되는 시스템에서 사용된다. 사이클 스틸 모드에서 DMA 컨트롤러는 CPU와 DMA 컨트롤러 간의 인터페이스를 제어하는 신호인 ''BR''(버스 요청) 및 ''BG''(버스 허가) 신호를 사용하여 시스템 버스에 접근한다.[2]사이클 스틸 모드에서는 한 단위의 데이터가 전송된 후, BG 신호를 통해 시스템 버스 제어가 CPU로 다시 넘어간다. 그 후, BR 신호를 통해 지속적으로 버스를 다시 요청하여 한 번에 한 단위의 데이터를 전송하고, 전체 데이터 블록이 전송될 때까지 이 과정을 반복한다.[2] DMA 컨트롤러는 시스템 버스 제어를 계속해서 얻고 해제함으로써, 명령어와 데이터 전송을 번갈아 가며 처리(인터리빙)한다. CPU가 명령을 처리하면, DMA 컨트롤러가 하나의 데이터 값을 전송하는 방식이다.[2]

데이터가 빠르게 전송되지는 않지만, CPU는 버스트 모드에서처럼 오랫동안 대기 상태가 되지 않는다. 사이클 스틸 모드는 데이터를 실시간으로 감시하는 컨트롤러에 유용하다.[2]

사이클 스틸 방식에서는 CPU가 메모리에 접근하지 않는 버스 사이클 동안 DMA가 버스를 사용한다.[23] CPU는 메모리 버스를 계속 사용한다고 할 수는 없으므로, CPU가 처리를 진행하는 것과 동시에 데이터 전송이 가능하다.[24]

CPU로부터 메모리 버스 제어를 넘겨받아 1~2 워드씩 전송하는 방법을 사이클 스틸 모드 DMA라고 한다.[24]

4. 3. 버스트 (Burst)

버스트 모드에서는 전체 데이터 블록이 하나의 연속된 시퀀스로 전송된다. DMA 컨트롤러가 CPU에 의해 시스템 버스에 대한 접근 권한을 부여받으면, CPU에 시스템 버스 제어를 다시 넘겨주기 전에 데이터 블록의 모든 바이트를 전송하지만, CPU는 비교적 오랜 기간 동안 비활성화된다. 이 모드는 "블록 전송 모드"라고도 한다.[23]DMA의 버스 중재(Bus Arbitration) 방식에는 '''라운드 로빈''', '''사이클 스틸''', '''버스트'''가 있다. 라운드 로빈은 버스 제어권을 순서대로 양도하는 방식이다. 사이클 스틸 방식에서는 CPU가 메모리에 접근하지 않는 버스 사이클 동안 DMA가 버스를 사용한다. 버스트 방식은 일정 시간 동안 하나의 버스 마스터가 버스 제어권을 점유하는 방식으로, 우선순위가 높은 데이터를 급하게 전송하고 싶을 때 사용한다.[23]

버스트 모드 DMA는 CPU로부터 메모리 버스 제어를 넘겨받아 데이터를 일시에 전송하는 방법으로,[24] 블록 전송이라고 부르기도 한다.[24]

5. 사용 시 주의사항

DMA 사용 시 주의해야 할 주요 사항은 다음과 같다.

- 데이터 버스 폭: DMA 사용을 전제로 할 때, 데이터 버스의 비트 폭을 CPU의 데이터 비트 폭과 반드시 맞출 필요는 없다. 데이터 버스 폭을 CPU보다 넓게 하면 CPU를 거치는 것보다 더 넓은 대역폭으로 데이터를 전송할 수 있다. 예를 들어, AXI 버스는 2003년 초판부터 최대 1024비트 폭의 데이터 버스를 지원했다. 당시 CPU 데이터 폭은 32비트가 주류였고, AArch64가 발표되기 8년 전이었다.

- 인터럽트 증가: DMAC는 전송 종료를 CPU에 인터럽트로 알리는 것 외에, 데이터 전송의 종단 장치가 자체 인터럽트로 CPU에 알릴 수 있다. 이 경우 DMAC와 종단 장치 양쪽에서 거의 동시에 전송 종료 인터럽트가 발생하거나, 인터럽트 처리에서 같은 데이터에 접근해야 해 상호 배제가 필요하므로 CPU와 소프트웨어 부하가 증가한다.

- 오버런: 통신 기능을 사용할 때, 수신 버퍼에 저장된 데이터를 CPU나 DMA가 읽기 전에 다음 데이터를 받아 이전 수신 데이터가 손실되는 현상이다.

- 캐시 일관성: DMA는 CPU에 캐시가 있고 장치가 DMA를 사용하여 직접 접근할 수 있는 외부 메모리가 있을 때 캐시 일관성 문제를 일으킬 수 있다.

- 가상 메모리 환경에서의 물리 메모리 페이지 경계: 물리 메모리 주소를 메모리 어드레싱에 사용하는 DMAC를 사용하여 DMA를 실행하는 경우, 물리 메모리 페이지 경계를 넘지 않도록 해야 한다.

5. 1. 오버런 (Overrun)

오버런은 통신 기능을 사용할 때, 수신 버퍼에 저장된 데이터를 CPU나 DMA가 읽기 전에 다음 데이터를 받아 이전 수신 데이터가 손실되는 현상이다. 특히 사이클 스틸 또는 버스트 방식에서는 CPU나 DMA가 버스 사용권을 기다리는 시간이 길어져 오버런이 발생할 수 있다. 라운드 로빈 방식에서는 버스 사용권 대기 시간이 짧아 오버런이 발생하기 어렵다.[25]5. 2. 캐시 일관성 (Cache Coherency)

DMA는 CPU에 캐시가 있고 장치가 DMA를 사용하여 직접 접근할 수 있는 외부 메모리가 있을 때 캐시 일관성 문제를 일으킬 수 있다. CPU가 메모리의 특정 위치(X)에 접근하면 그 값은 캐시에 저장된다. 이후 CPU가 X를 업데이트하면 캐시된 사본은 업데이트되지만, Write-back 캐시의 경우 외부 메모리의 X는 업데이트되지 않는다. 장치가 다음에 X에 접근하기 전에 캐시가 메모리로 플러시되지 않으면, 장치는 X의 오래된 값을 받게 된다.[1]마찬가지로, 장치가 메모리에 새 값을 쓰면 X의 캐시된 사본이 무효화되지 않을 경우 CPU는 X의 오래된 값으로 작동한다.[1]

이 문제는 시스템 설계에서 두 가지 방법으로 해결할 수 있다.[1]

- 캐시 일관성 시스템: 버스 스누핑이라는 하드웨어를 통해 외부 쓰기를 캐시 컨트롤러에 알리고, 캐시 컨트롤러는 DMA 쓰기에 대해 캐시 무효화를 수행하거나 DMA 읽기에 대해 캐시 플러시를 수행한다.

- 비일관성 시스템: 소프트웨어(OS)가 발신 DMA 전송 전에 캐시 라인을 플러시하고, 수신 DMA 전송의 영향을 받는 메모리 범위에 접근하기 전에 무효화한다. OS는 스레드가 해당 메모리 범위에 접근하지 않도록 해야 한다. 이 방식은 DMA 작업에 오버헤드를 발생시킨다.

L2 캐시는 일관성이 유지되는 반면, L1 캐시(일반적으로 CPU 내장)는 소프트웨어에서 관리하는 하이브리드 방식도 존재한다.[1]

캐시를 사용하는 시스템에서는 캐시와 메인 메모리의 데이터 일관성이 손실될 수 있으므로, 이를 관리하는 방법이 필요하다.[25]

5. 3. 가상 메모리 환경에서의 물리 메모리 페이지 경계

물리 메모리 주소를 메모리 어드레싱에 사용하는 DMAC를 사용하여 DMA를 실행하는 경우, 물리 메모리 페이지 경계를 넘지 않도록 해야 한다. 경계를 넘는 경우, 후속 논리 주소 페이지에 해당하는 물리 주소 페이지가 마찬가지로 연속적인 후속 영역에 확보된다는 보장이 없기 때문이다.[26] DMAC가 Vectored I/O영어를 지원하는 경우, 각 물리 주소 페이지마다 DMA 전송을 설정하고 이를 연속 실행함으로써 물리 메모리 페이지 경계를 넘는 DMA 전송이 가능해진다.5. 4. 인터럽트 증가

DMAC는 보통 전송이 끝나면 CPU에게 인터럽트를 통해 알린다. 하지만 이와 별도로 데이터 전송의 종단 장치가 자체 인터럽트를 통해 CPU에게 전송 종료를 알리는 경우도 있다.[26] 이 경우, DMAC와 종단 장치 양쪽에서 거의 동시에 전송 종료 인터럽트가 발생하거나, 어느 한쪽의 인터럽트 처리 과정에서 같은 데이터에 접근해야 할 수 있다. 이는 상호 배제를 필요로 하여 CPU와 소프트웨어에 부담을 준다. 인터럽트 부하를 줄이려면 DMAC나 종단 장치 중 하나의 인터럽트를 억제해야 한다. 어떤 인터럽트를 억제할 수 있는지, 그리고 어느 쪽을 억제하는 것이 좋은지는 종단 장치의 사양과 DMA 전송 절차에 따라 결정된다.6. 역사

DMA를 사용하면 컴퓨터의 전반적인 성능을 향상시킬 수 있다[20]。 DMA가 있으면 CPU는 데이터 전송 작업을 DMAC에 맡기고 다른 작업을 할 수 있기 때문이다[20][21]。 DMA는 CPU와 버스를 공유하기 때문에 버스 사용 권한 조정이 필요한데[20], 이를 "버스 아비트레이션(Bus Arbitration)"이라고 한다[20]。

DMAC는 CPU로부터 데이터 전송원, 전송 대상, 전송 모드, 데이터 크기 등을 지정받고 전송 시작 트리거를 받으면 데이터 전송을 수행한다[22][20]。 전송이 완료되거나 오류가 발생하면 DMAC는 CPU에 인터럽트를 걸어 알린다[20]。

과거에는 CPU가 마더보드 칩셋에 내장된 DMAC에 명령을 보내는 방식(ISA 버스)을 사용했다. 현대에는 I/O 기기가 직접 PCI 버스를 제어하는 방식(Bus mastering DMA)이 사용된다. 임베디드 시스템에서는 SoC 내 DMAC가 SoC 내 버스를 조작하여 DMA를 구현하기도 한다.

네트워크 패킷 전송, 음악 재생, 비디오 배포 등에는 DMA가 전용 내장 칩으로 사용되며, 멀티 코어 및 클러스터링 환경에서도 효과적이다.

데이터 버스 폭은 CPU 데이터 폭보다 넓게 설정하여 CPU를 거치지 않고 더 넓은 대역폭으로 데이터를 전송할 수 있다. 예를 들어 AXI 버스는 2003년부터 최대 1024비트 폭의 데이터 버스를 지원했다.

6. 1. 초기 (1970년대)

DMA는 PDP 시리즈에서 채택되었다.1970년대에 출시된 수 MHz로 동작하는 마이크로프로세서에서는, CPU에 의한 데이터 전송으로 하드 디스크 등의 10MB/초 정도의 전송 속도를 발휘하는 것은 곤란하여, 전용 컨트롤러로 데이터 전송을 할 필요가 있었다. 이 컨트롤러는 데이터 전송을 고속으로 수행하는 기능에 특화된 CPU라고도 할 수 있다. 예를 들어 Z80에는 Z80DMA, MC68000에는 MC68450 등의 DMA 컨트롤러(DMAC)가 준비되어 있었다.[27]

6. 2. 1980년대

1970년대에 출시된 수 MHz로 동작하는 마이크로프로세서에서는 CPU에 의한 데이터 전송으로 하드 디스크 등의 10MB/초 정도의 전송 속도를 내는 것이 어려웠기 때문에, 전용 컨트롤러로 데이터 전송을 할 필요가 있었다. 이 컨트롤러는 데이터 전송을 고속으로 수행하는 기능에 특화된 CPU라고도 할 수 있다. 예를 들어 Z80에는 Z80DMA, MC68000에는 MC68450 등의 DMA 컨트롤러(DMAC)가 있었다.[27]1982년 2월에 발표된 인텔 80286(APX286) 등에서는 당시 통상적인 I/O를 제어하기에 충분한 동작 속도였고, 주류 개인용 컴퓨터에 i8249 등 저속 DMAC만 탑재되어 있었으며, 다른 적당한 DMAC가 존재하지 않았던 점 등으로 인해 DMA는 그다지 사용되지 않게 되었다.

6. 3. 1990년대 이후

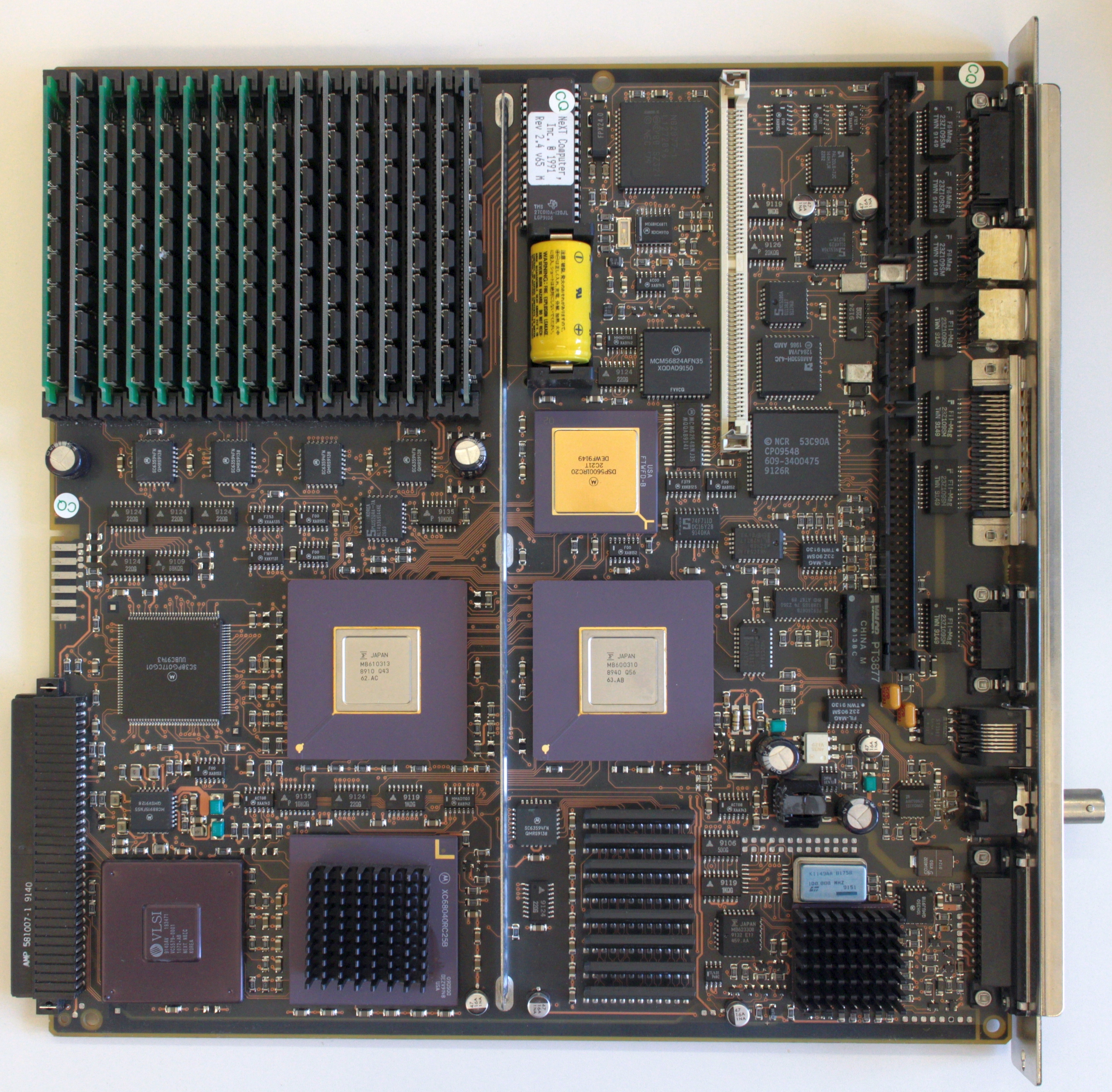

1990년대에 CPU가 펜티엄 세대로 발전하면서 충분히 고속화되자, 저속 I/O 관리가 병목 현상이 되었다. 이에 따라, 이른바 칩셋에 I/O 전용의 고속 DMAC가 탑재되거나, 주변 기기 제어 LSI가 간단한 DMA 기능을 가지게 되면서 DMA가 다시 활용되기 시작했다. 펜티엄 이후 주류가 된 PCI 버스에서는 버스 마스터링으로 DMA가 구현되었다.초기 DMAC는 단순히 지정된 주소 범위의 데이터를 지정된 메모리 또는 포트로 입출력하는 기능만 가지고 있었다. 그러나 운영 체제가 보급되고, 하드 디스크에 대한 I/O에 DMAC를 사용하게 되면서, DMAC에는 "데이터 블록을 분할하는(스캐터링)", "데이터 블록을 집약하는(개더링)" 기능을 수행하는 것이 요구되었다. MC63450 DMAC 등에는 DMAC가 링크 리스트를 읽어 들여 전송 내용을 분할하거나 집약하는 기능이 탑재되어 있다. PC/AT 호환기용 SCSI 호스트 어댑터 카드 등에서는, 컨트롤러 칩에 집적된 DMAC가 이 기능을 담당했다. 스캐터링·개더링 기능이 없는 경우 CPU는 최소한 1 섹터씩 메모리 간 전송을 수행해야 했고, 또한 DMAC에 읽어 들일 메모리 영역을 전송 완료까지 사용할 수 없기 때문에, I/O 시 CPU 부하 상승과 I/O 대기 시간이 발생하여 시스템 성능에 악영향을 미쳤다.[27]

6. 4. 고기능 DMAC의 등장

초기 DMAC는 지정된 주소 범위의 데이터를 지정된 메모리 또는 포트로 입출력하는 기능만 갖추고 있었다. 그러나 운영 체제가 보급되고, 하드 디스크에 대한 I/O에 DMAC를 사용하게 되면서, DMAC에는 "데이터 블록을 분할하는(스캐터링)", "데이터 블록을 집약하는(개더링)" 기능을 수행하는 것이 요구되었다. MC63450 DMAC 등에는 DMAC가 링크 리스트를 읽어 들여 전송 내용을 분할하거나 집약하는 기능이 탑재되어 있다.[27] PC/AT 호환기용 SCSI 호스트 어댑터 카드 등에서는 컨트롤러 칩에 집적된 DMAC가 이 기능을 담당했다. 스캐터링·개더링 기능이 없는 경우 CPU는 최소한 1 섹터씩 메모리 간 전송을 수행해야 했고, 또한 DMAC에 읽어 들일 메모리 영역을 전송 완료까지 사용할 수 없었기 때문에, I/O 시 CPU 부하 상승과 I/O 대기 시간이 발생하여 시스템 성능에 악영향을 미쳤다.7. 현대적 응용

DMA는 컴퓨터의 전반적인 성능 향상에 기여한다. DMA를 이용하면 CPU는 데이터 전송 작업을 DMAC에 맡기고, 그동안 CPU만이 할 수 있는 다른 작업에 집중할 수 있다.[20][21] 이는 외부 입출력 장치와 주변 장치의 데이터 전송 속도가 RAM보다 훨씬 느리기 때문에, DMA가 없으면 CPU가 데이터 전송을 기다리는 데 많은 시간을 소비해야 하기 때문이다.

하지만 DMA는 하나뿐인 버스를 CPU와 공유하기 때문에 버스 사용 권한 조정, 즉 "버스 아비트레이션"이 필요하다.[20]

일반적으로 DMAC가 DMA 데이터 전송을 수행한다. CPU는 DMAC에 데이터 전송원, 전송 대상, 전송 모드, 데이터 크기 등을 설정하고 전송 시작 신호를 보낸다.[22][20] 이후 CPU는 다른 작업을 시작할 수 있으며, DMAC는 데이터 전송이 완료되면 CPU에 인터럽트를 걸어 완료를 알린다.[20] 오류 발생 시에도 CPU에 인터럽트를 통해 알린다.[22]

과거에는 ISA 버스 방식을 통해 CPU가 마더보드 칩셋에 내장된 DMAC에 명령을 보냈다. 현대 PCI 버스에서는 I/O 장치가 PCI 버스 제어를 맡아 DMA 전송을 관리하는 "버스 마스터링 DMA" 방식을 사용한다. 임베디드 시스템에서는 SoC 내 버스에 직접 연결된 DMAC가 SoC 내 버스를 조작하여 DMA를 구현하기도 한다. 필요한 전송 성능이나 허용되는 소비 전력 등에 따라 여러 버스를 선택적으로 사용하며, 이때 DMAC도 각 버스에 맞는 것을 선택해야 한다.

네트워크 패킷 전송, 음악 재생, 비디오 배포 등 지속적인 읽기가 필요한 경우 DMA는 전용 내장 칩으로 사용된다. DMA는 멀티 코어 및 클러스터링 환경에서도 효과적이다. DMA 통신 상태를 알리는 HOLD 핀(수신 상태)과 HLDA 핀(전송 상태)이 있다.

DMA 사용 시 데이터 버스 비트 폭을 CPU 데이터 비트 폭과 반드시 맞출 필요는 없다. 데이터 버스 비트 폭을 CPU보다 넓게 하면 CPU를 거치는 것보다 더 넓은 대역폭으로 데이터를 전송할 수 있다. 예를 들어 AXI 버스는 2003년 초판부터 최대 1024비트 폭의 데이터 버스를 지원했는데, 이는 당시 주류였던 32비트 CPU 데이터 폭보다 훨씬 넓은 것이었다.

7. 1. ISA

ISA 버스 표준에서는 DMA를 위해 메모리를 최대 16MB까지 지정할 수 있었다.[1]IBM PC (그리고 후속 모델인 PC/XT) 초창기에는 4개의 DMA 채널(0~3번)을 제공하는 하나의 인텔 8237 DMA 컨트롤러만 있었다. 이 DMA 채널은 8비트 전송을 수행했으며, 첫 번째 메가바이트의 RAM만 주소 지정할 수 있었다. 또한, 컨트롤러는 확장 버스 I/O 장치 간의 전송에만 사용할 수 있었다. 8237은 채널 0과 1을 사용하여 메모리 간 전송만 수행할 수 있었으며, PC(& XT)의 채널 0은 DRAM 갱신에 전용으로 사용되었기 때문에 범용 "블리터"로 사용할 수 없게 했다. 결과적으로 CPU의 일반적인 PIO 속도에 의해 제한된 PC의 블록 메모리 이동 속도는 매우 느렸다.

IBM PC/AT에서 향상된 AT 버스 (더 친숙하게 ISA로 리트로님화)는 두 번째 8237 DMA 컨트롤러를 추가하여 3개의 추가 채널(5–7; 채널 4는 첫 번째 8237에 대한 캐스케이드로 사용됨)을 제공했다. 페이지 레지스터는 또한 80286 CPU의 전체 16MB 메모리 주소 공간을 주소 지정하도록 재구성되었다. 이 두 번째 컨트롤러는 또한 I/O 장치가 데이터 소스 및/또는 대상으로 사용될 때 16비트 전송을 수행할 수 있는 방식으로 통합되었다. 이로 인해 상위 3개 채널을 사용할 때 데이터 처리량이 두 배로 증가했다. 호환성을 위해 하위 4개의 DMA 채널은 여전히 8비트 전송으로만 제한되었다. 64 kB 세그먼트 경계 문제는 남아 있었으며, 개별 전송은 16비트 모드에서도 세그먼트를 넘을 수 없었다.

뒤떨어진 성능과 80386 프로세서의 등장, 그리고 자체적인 DMA 서브시스템을 갖춘 "ISA" 버스의 추가 발전 또는 대체로 인해, 원래의 DMA 컨트롤러는 성능 저해 요인처럼 보였다. 이러한 컨트롤러는 이후 컴퓨터에서 내장된 레거시 PC 하드웨어를 지원하는 데 필요한 만큼 지원되었다. 32비트 확장 버스가 일반화된 후에도 ISA DMA를 계속 사용한 레거시 하드웨어는 Sound Blaster 카드와, Super I/O 장치였다. 원래 8237 또는 직접 호환 장치가 여전히 사용되는 경우, 이러한 장치와의 전송은 시스템의 실제 주소 공간 또는 설치된 메모리 양에 관계없이 메인 RAM의 처음 16 MB로 제한될 수 있다.

각 DMA 채널에는 16비트 주소 레지스터와 16비트 카운트 레지스터가 연관되어 있다. 데이터 전송을 시작하기 위해 장치 드라이버는 DMA 채널의 주소 및 카운트 레지스터를 데이터 전송 방향(읽기 또는 쓰기)과 함께 설정한다. 그런 다음 DMA 하드웨어에 전송을 시작하도록 지시한다. 전송이 완료되면 장치는 CPU를 인터럽트한다.

산포-수집(Scatter-gather) 또는 벡터화된 I/O DMA는 단일 DMA 트랜잭션에서 여러 메모리 영역 간의 데이터 전송을 허용한다. 이는 여러 간단한 DMA 요청을 함께 연결하는 것과 같다. 그 동기는 CPU에서 여러 입력/출력 인터럽트 및 데이터 복사 작업을 오프로드하는 것이다.

DRQ는 ''Data request'(데이터 요청)를 나타내고, DACK는 ''Data acknowledge'(데이터 승인)를 나타낸다. 이러한 기호는 DMA 기능을 갖춘 컴퓨터 시스템의 하드웨어 회로도에서 볼 수 있으며, CPU와 DMA 컨트롤러 간의 전자 신호 라인을 나타낸다. 각 DMA 채널에는 하나의 요청 라인과 하나의 승인 라인이 있다. DMA를 사용하는 장치는 할당된 DMA 채널의 두 라인을 모두 사용하도록 구성해야 한다.

16비트 ISA는 버스 마스터링을 허용했다.[5]

표준 ISA DMA 할당은 다음과 같다.

7. 2. PCI

버스 마스터링 시스템에서 CPU와 주변 장치는 각각 메모리 버스 제어 권한을 가질 수 있다. PCI 아키텍처는 ISA와 달리 중앙 DMA 컨트롤러가 없다. 대신, PCI 장치는 버스 제어를 요청("버스 마스터"가 됨)하고 시스템 메모리에서 읽고 쓰기를 요청할 수 있다.[6] PCI 구성 요소는 PCI 버스 컨트롤러(일반적으로 PCI 호스트 브리지 및 PCI-PCI 브리지)에 버스 소유권을 요청하며, 여러 장치가 동시에 버스 소유권을 요청할 경우 중재한다. 한 번에 하나의 버스 마스터만 존재할 수 있기 때문이다. 구성 요소가 소유권을 부여받으면 PCI 버스에서 일반적인 읽기 및 쓰기 명령을 발행하며, PCI 버스 컨트롤러가 이를 처리한다.예를 들어, 인텔 코어 기반 PC에서 사우스브리지는 DMI를 사용하여 트랜잭션을 메모리 컨트롤러(CPU 다이에 통합되어 있음)로 전달하며, 메모리 컨트롤러는 이를 DDR 작업으로 변환하여 메모리 버스를 통해 전송한다. PCI DMA 전송에는 여러 단계가 관여하지만, PCI 장치나 PCI 버스 자체가 나머지 구성 요소보다 속도가 훨씬 느리기 때문에(list of device bandwidths 참조) 큰 문제가 되지 않는다.

최신 x86 CPU는 x86-64 CPU의 네이티브 64비트 모드 또는 PAE (36비트 주소 지정 모드)를 활용하여 4GB 이상의 메모리를 사용할 수 있다. 이러한 경우 32비트 주소 버스를 사용하는 DMA를 가진 장치는 4GB 라인 위의 메모리를 주소 지정할 수 없다. 새로운 DAC 메커니즘은 PCI 버스와 장치 자체 모두에 구현된 경우[7] 64비트 DMA 주소 지정을 가능하게 한다. 그렇지 않으면 운영 체제는 비용이 많이 드는 이중 버퍼 (DOS/Windows 명명법) (일명 bounce buffers (FreeBSD/Linux))를 사용하거나, IOMMU가 있는 경우 IOMMU를 사용하여 주소 변환 서비스를 제공하는 방식으로 문제를 해결해야 한다.

7. 3. I/OAT (I/O Acceleration Technology)

일부 인텔 제온 칩셋에 포함된 I/O 가속 기술(I/OAT)은 DMA 엔진의 한 예시이다. I/OAT는 주 CPU에서 메모리 복사 작업을 오프로드하여 CPU가 다른 작업을 수행할 수 있도록 한다.[8] 2006년 인텔의 리눅스 커널 개발자 앤드류 그로버는 I/OAT를 사용하여 네트워크 트래픽 복사를 오프로드하는 벤치마크를 수행하였고, 수신 작업 부하에서 CPU 사용률이 10% 향상된 것을 발견했다.[9]7. 4. DDIO (Data Direct I/O)

인텔 제온 E5 프로세서에는 '''데이터 직접 I/O''' ('''DDIO''') 기능이 도입되어 DMA 메커니즘의 성능이 향상되었다. DDIO는 DMA "창"이 시스템 RAM 대신 CPU 캐시 내에 존재할 수 있게 한다. 결과적으로 CPU 캐시는 I/O의 주 소스 및 대상이 되어 네트워크 인터페이스 컨트롤러(NIC)가 로컬 CPU의 마지막 레벨 캐시(L3 캐시)로 직접 DMA를 수행하고 시스템 RAM에서 I/O 데이터를 가져오는 비용을 절감할 수 있다. DDIO는 전체 I/O 처리 대기 시간을 줄이고, I/O 처리를 캐시 내에서 수행할 수 있게 하며, 사용 가능한 RAM 대역폭/대기 시간이 성능 병목 현상이 되는 것을 방지하고, RAM이 저전력 상태로 더 오래 유지될 수 있도록 하여 전력 소비를 줄일 수 있다.7. 5. AHB (AMBA High-performance Bus)

시스템 온 칩 및 임베디드 시스템에서 일반적인 시스템 버스 인프라는 AMBA 고성능 버스와 같은 복잡한 온칩 버스이다. AMBA는 AHB 구성 요소의 두 가지 종류, 즉 마스터와 슬레이브를 정의한다. 슬레이브 인터페이스는 ARM과 같은 임베디드 CPU에서 실행되는 소프트웨어가 장치 내부의 I/O 레지스터를 쓰거나 읽거나 (덜 일반적이지만) 로컬 메모리 블록에 접근할 수 있는 프로그래밍된 I/O와 유사하다. 마스터 인터페이스는 장치가 CPU에 과도한 부하를 주지 않고 시스템 메모리에서/로 DMA 트랜잭션을 수행하는 데 사용할 수 있다.[1]따라서 대량의 데이터를 시스템 메모리로/에서 전송해야 하는 네트워크 컨트롤러와 같은 고대역폭 장치는 AHB에 대한 두 개의 인터페이스 어댑터, 즉 마스터 및 슬레이브 인터페이스를 갖게 된다. 이는 AHB와 같은 온칩 버스가 버스의 트리 스테이트 또는 버스에서 임의의 라인의 방향 교환을 지원하지 않기 때문이다. PCI와 마찬가지로 DMA는 버스 마스터링이므로 중앙 DMA 컨트롤러가 필요하지 않지만, 시스템에 여러 마스터가 있는 경우 아비터가 필요하다.[1]

내부적으로는 일반적으로 소프트웨어에 의해 프로그래밍된 여러 개의 동시 산포-수집 작업을 수행하기 위해 장치에 멀티채널 DMA 엔진이 존재한다.[1]

7. 6. Cell

멀티프로세서 시스템 온 칩에서 DMA 사용 예시로, IBM/소니/도시바의 Cell은 하나의 Power 프로세서 요소(PPE)와 8개의 시너지 프로세서 요소(SPE)를 포함한 9개의 처리 요소 각각에 DMA 엔진을 통합한다. SPE의 로드/저장 명령은 자체 로컬 메모리만 읽고 쓸 수 있으므로, SPE는 주 메모리 및 다른 SPE의 로컬 메모리와 데이터를 전송하기 위해 DMA에 전적으로 의존한다. 따라서 DMA는 이 CPU 내부 코어 간 데이터 전송의 주요 수단으로 작용한다(인텔의 취소된 범용 GPU, Larrabee와 같은 캐시 일관 CMP 아키텍처와 대조적).Cell의 DMA는 완전히 캐시 일관성을 갖는다(하지만 DMA에 의해 작동되는 SPE의 로컬 저장은 표준 의미에서 전역적으로 일관된 캐시로 작용하지 않는다). 읽기("get")와 쓰기("put") 모두에서 DMA 명령은 최대 16KB 크기의 단일 블록 영역 또는 2개에서 2048개의 블록 목록을 전송할 수 있다. DMA 명령은 로컬 주소와 원격 주소의 쌍을 지정하여 실행된다. 예를 들어 SPE 프로그램이 put DMA 명령을 실행할 때, 소스로는 자체 로컬 메모리의 주소를, 대상으로는 가상 메모리 주소(주 메모리 또는 다른 SPE의 로컬 메모리를 가리킴)를 블록 크기와 함께 지정한다. 실험에 따르면, Cell의 DMA의 효과적인 피크 성능(3 GHz, 균일한 트래픽 하에서)은 초당 200GB에 도달한다.[14]

8. DMA 컨트롤러 (DMAC)

표준 DMA, 즉 서드파티 DMA는 DMA 컨트롤러를 사용한다. DMA 컨트롤러는 메모리 주소를 생성하고 메모리 읽기 또는 쓰기 사이클을 시작할 수 있다. 여기에는 CPU가 쓰고 읽을 수 있는 여러 개의 하드웨어 레지스터가 포함되어 있는데, 메모리 주소 레지스터, 바이트 수 레지스터, 하나 이상의 제어 레지스터 등이 그것이다.[1] DMA 컨트롤러가 제공하는 기능에 따라 이러한 제어 레지스터는 소스, 대상, 전송 방향(I/O 장치에서 읽기 또는 I/O 장치에 쓰기), 전송 단위의 크기 및/또는 한 번의 버스트로 전송할 바이트 수를 조합하여 지정할 수 있다.[1]

입력, 출력 또는 메모리 간 작업을 수행하기 위해 호스트 프로세서는 전송할 워드 수와 사용할 메모리 주소의 수를 사용하여 DMA 컨트롤러를 초기화한다. 그런 다음 CPU는 주변 장치에 데이터 전송을 시작하도록 명령한다. 이후 DMA 컨트롤러는 시스템 메모리에 주소와 읽기/쓰기 제어 라인을 제공한다. 주변 장치와 메모리 간에 데이터 바이트를 전송할 준비가 될 때마다 DMA 컨트롤러는 전체 데이터 블록이 전송될 때까지 내부 주소 레지스터를 증가시킨다.

DMA에서의 데이터 전송은 일반적으로 DMAC가 수행한다. CPU는 DMAC에 데이터의 전송원, 전송 대상, 전송 모드, 데이터 수 등을 지정하고, 그 후에 전송 시작 트리거를 보내기만 하면 된다.[22][20] 트리거를 보내면 CPU는 다른 작업을 시작할 수 있다.[22] DMAC는 데이터 전송 작업을 완료하면 CPU에 인터럽트를 걸어 전송 종료를 알린다.[20] 또한 데이터 전송에서 오류가 발생한 경우에도 CPU에 인터럽트를 걸어 알린다.[22]

과거의 ISA 버스 방식에서는 CPU가 마더보드의 칩셋에 내장된 DMAC에 명령을 보내는 방식이었다. 현대의 PCI 버스에서는 "Bus mastering DMA" 즉, I/O 기기 측에서 PCI 버스의 제어를 맡아 DMA 전송을 모두 관장하는 방식이 채택되고 있다. 한편, 임베디드 시스템에서는 SoC 내에서 버스에 직결된 DMAC가 SoC 내의 버스를 조작하여 DMA를 실현하는 경우가 있다. 또한, 필요한 전송 성능이나 허용 가능한 소비 전력 등의 사용 조건에 따라 여러 개의 버스를 상황에 맞게 사용하는 경우가 있는데, 이 경우 DMAC도 각 버스에 대응하는 것을 선택할 필요가 있다.

네트워크 패킷 전송이나 음악 재생, 비디오 배포 등과 같은 경우에는 지속적인 읽기가 필요하며, DMA는 전용 내장 칩으로 사용된다. 또한 DMA는 멀티 코어에서도 클러스터링에서도 효과를 발휘한다. 이 경우, DMA 통신의 상태 알림 핀으로 수신 상태를 나타내는 HOLD 핀과, 전송 상태를 나타내는 HLDA 핀이 존재한다.

DMA 사용을 전제로 하는 경우, 데이터 버스의 비트 폭을 반드시 CPU의 데이터 비트 폭에 맞출 필요는 없다. 특히 데이터 버스의 비트 폭을 CPU의 데이터 비트 폭보다 넓게 함으로써 CPU를 경유하는 것보다 더 광대역의 데이터 전송이 가능해진다.

대표적인 DMA 컨트롤러는 다음과 같다.

- Z80DMA

- μPD8237AC-5 ([i8237](https://en.wikipedia.org/wiki/Intel_8237) -5 호환)[28]

- MC68450

- i430 등, 펜티엄 CPU 이후 지원하는 칩셋

- μPD71037[29]

- μPD71071[30]

- CoreLink DMA-330[31] (마이크로 프로그램이 필요하며, 그 구현에 따라 커스터마이즈가 가능하다.)

- 인텔 8257

- Am9517[15]

- 인텔 8237

- Z80 DMA[16]

- LH0083[17] (Z80 DMA 호환)

- μPD71037[18] (64KB 메모리 어드레싱 가능)

- μPD71071[19] (16MB 메모리 어드레싱 가능)

9. 파이프라이닝 (Pipelining)

스크래치패드 메모리와 DMA (디지털 신호 프로세서 및 Cell 프로세서 등)를 갖춘 프로세서는 이중 버퍼링 또는 멀티 버퍼링을 통해 처리와 DMA 메모리 작업을 소프트웨어적으로 겹치게 하여 이점을 얻을 수 있다. 예를 들어, 온칩 메모리는 두 개의 버퍼로 분할된다. 프로세서가 한 버퍼의 데이터를 처리하는 동안 DMA 엔진은 다른 버퍼에 데이터를 로드하고 저장할 수 있다. 이를 통해 시스템은 예측 가능한 메모리 접근 패턴을 필요로 하는 대신 메모리 지연 시간을 피하고 버스트 전송을 활용할 수 있다.

참조

[1]

서적

An Introduction to Microcomputers: Volume 1: Basic Concepts

https://archive.org/[...]

Osborne McGraw Hill

[2]

서적

Computer Architecture and Organization

McGraw-Hill International Book Company

[3]

웹사이트

Intel 8237 & 8237-2 Datasheet

http://www.jbox.dk/r[...]

2019-04-20

[4]

웹사이트

DMA Fundamentals on various PC platforms, National Instruments, pages 6 & 7

https://www.ing.unlp[...]

2019-04-20

[5]

간행물

PC Architecture for Technicians: Level 1

2003-04-25

[6]

웹사이트

Bus Specifics - Writing Device Drivers for Oracle® Solaris 11.3

https://docs.oracle.[...]

2020-12-18

[7]

웹사이트

Physical Address Extension — PAE Memory and Windows

http://www.microsoft[...]

Microsoft Windows Hardware Development Central

2008-04-07

[8]

웹사이트

Memory copies in hardware

https://lwn.net/Arti[...]

2005-12-08

[9]

웹사이트

I/OAT on LinuxNet wiki

http://www.linuxfoun[...]

2006-12-12

[10]

웹사이트

Intel Data Direct I/O (Intel DDIO): Frequently Asked Questions

http://www.intel.com[...]

Intel

2015-10-11

[11]

웹사이트

Pushing the Limits of Kernel Networking

http://rhelblog.redh[...]

2015-10-11

[12]

웹사이트

Achieving Lowest Latencies at Highest Message Rates with Intel Xeon Processor E5-2600 and Solarflare SFN6122F 10 GbE Server Adapter

http://www.solarflar[...]

2015-10-11

[13]

웹사이트

Pushing the Limits of Kernel Networking

https://events.stati[...]

2015-10-11

[14]

논문

Cell Multiprocessor Communication Network: Built for Speed

http://portal.acm.or[...]

2006-05-01

[15]

웹사이트

Am9517A Multimode DMA Controller

http://www.bitsavers[...]

2024-01-06

[16]

웹사이트

Z80® DMA Direct Memory Access Controller

http://www.bitsavers[...]

2024-01-07

[17]

웹사이트

Sharp 1986 Semiconductor Data Book

http://www.bitsavers[...]

2024-01-13

[18]

웹사이트

pPD71037 Direct Memory Access (DMA) Controller

http://bitsavers.inf[...]

2024-01-06

[19]

웹사이트

µPD71071 DMA Controller

http://bitsavers.inf[...]

2024-01-05

[20]

뉴스

DMAのメリットって何?

https://edn.itmedia.[...]

EDN, 菅井賢

[21]

웹사이트

Direct Memory Access

https://www.techtarg[...]

Tech Target

[22]

문서

The Essentials of Computer Organization and Architecture

[23]

뉴스

DMAって何 p.2

https://edn.itmedia.[...]

[24]

서적

Computer Architecture and Organization

MCGRAW-HILL INTERNATIONAL BOOK COMPANY

[25]

웹사이트

https://edn.itmedia.[...]

[26]

서적

Computer Organization and Design: The Hardware/Software Interface

Morgan Kaufmann Publishers

[27]

웹사이트

H8-MPUを知る

https://www.cqpub.co[...]

CQ

[28]

서적

PC-9801解析マニュアル[第0巻]

秀和システムトレーディング株式会社

1983-06-30

[29]

웹사이트

pPD71037 Direct Memory Access (DMA) Controller

http://bitsavers.inf[...]

2024-01-07

[30]

웹사이트

µPD71071 DMA Controller

http://bitsavers.inf[...]

2024-04-26

[31]

웹사이트

CoreLink DMA-330 DMA Controller Technical Reference Manual

https://developer.ar[...]

ARM

2024-08-12

[32]

서적

An Introduction to Microcomputers: Volume 1: Basic Concepts

https://archive.org/[...]

Osborne McGraw Hill

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com