원자층 증착

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

원자층 증착(ALD)은 기판 표면에 기체 상태의 전구체를 순차적으로 공급하여 자기 제한적인 표면 반응을 통해 박막을 형성하는 기술이다. 1960년대 소련에서 분자층 증착(ML)으로, 1974년 핀란드에서 원자층 에피택시(ALE)로 각각 개발되었으며, 1990년대 헬싱키 대학교에서 현재 명칭인 ALD로 통합되었다. ALD는 마이크로일렉트로닉스, 태양광 발전, 바이오메디컬 등 다양한 분야에 응용되며, 특히 마이크로전자 제품 제작에 유용하다. ALD는 정확한 두께 제어, 다층 구조 성장 용이성 등의 장점을 가지지만, 공정 속도가 느리고 기판의 높은 순도가 요구된다는 한계가 있다. ALD와 유사한 기술로는 분자층 증착(MLD)과 순차 침투 합성(SIS)이 있다.

더 읽어볼만한 페이지

- 박막 퇴적물 - 에피택시

에피택시는 원자층 단위 박막 성장 기술로, 재료와 결정 구조에 따라 여러 종류로 나뉘며, 다양한 성장 방식과 메커니즘을 통해 반도체 소자 제작, 나노기술 및 표면과학 분야에 활용된다. - 박막 퇴적물 - 음극 아크 퇴적물

음극 아크 퇴적은 1960년대 소련에서 개발되어 1980년대 서방 세계로 확산된 기술로, 고전류 아크 방전을 이용하여 금속 박막과 합금 코팅을 제조하며, 재료 과학, 반도체, 우주 항공, 의료 기기 등 다양한 산업 분야에서 활용된다. - 핀란드의 발명품 - 사우나

사우나는 핀란드에서 유래한 뜨거운 방에서 증기욕을 즐기는 시설 또는 행위로, 건식과 습식으로 나뉘며 혈액 순환 촉진, 스트레스 해소 등의 효과가 있어 전 세계적으로 이용되고 핀란드 문화의 중요한 요소이다. - 핀란드의 발명품 - 단문 메시지 서비스

단문 메시지 서비스(SMS)는 휴대전화로 짧은 텍스트 메시지를 주고받는 서비스이며, 1980년대 초에 시작되어 2세대 이동 통신 시스템에서 표준으로 채택되었고, 개인 간 통신 및 다양한 분야에서 활용되지만 스팸, 스미싱 등의 문제점도 존재한다. - 반도체 제조 - 웨이퍼

웨이퍼는 단결정 실리콘 잉곳을 가공하여 만든 얇고 둥근 반도체 재료 조각으로, 반도체 산업의 핵심 재료이며, 다양한 결정 성장 방법과 가공 과정을 거쳐 생산되고, 현재는 300mm 웨이퍼가 주류이지만 450mm 웨이퍼 개발 경쟁이 진행 중이며, 실리콘 외 다양한 재료가 사용되고, 일본 기업들이 시장을 주도하고 한국 기업들도 경쟁력을 확보하고 있다. - 반도체 제조 - 이온 주입

이온 주입은 원하는 원소를 이온화하여 고체 표면에 주입하는 기술로, 반도체 도핑, 금속 표면 처리 등 다양한 분야에 활용되며, 결정학적 손상, 스퍼터링, 안전 문제 등의 문제점을 야기한다.

| 원자층 증착 | |

|---|---|

| 개요 | |

| 기술 분야 | 박막 증착 기술 |

| 증착 방식 | 화학 기상 증착 |

| 특징 | 원자 수준 두께 제어 우수한 균일도 뛰어난 단차 피복성 |

| 적용 분야 | 반도체 소자 제조 태양 전지 디스플레이 촉매 에너지 저장 장치 바이오 센서 보호 코팅 |

| 역사 | |

| 개발 시기 | 1970년대 초 |

| 초기 연구자 | 툰티 술라, 카르 스탠더 |

| 초기 연구 목적 | EL 디스플레이용 박막 제조 |

| 주요 발전 | 반도체 산업 적용 |

| 증착 과정 | |

| 기본 원리 | 기판 표면에 화학 반응을 이용한 박막 성장 반응물(전구체) 주입과 퍼징의 반복 자기 제한적 표면 반응 |

| 주요 과정 단계 | 전구체 1 주입: 기판 표면에 1개 원자층 흡착 퍼징: 과량의 전구체 및 부산물 제거 전구체 2 주입: 흡착된 전구체와 반응하여 새로운 원자층 형성 퍼징: 과량의 전구체 및 부산물 제거 |

| 증착층 두께 조절 | 반응 사이클 수 조절 |

| 장점 | |

| 박막 제어 | 원자층 단위 정밀 제어 |

| 균일도 | 우수한 박막 균일도 |

| 단차 피복성 | 복잡한 구조에 대한 뛰어난 단차 피복성 |

| 저온 증착 | 비교적 낮은 온도에서 증착 가능 |

| 단점 | |

| 증착 속도 | 비교적 느린 증착 속도 |

| 생산 비용 | 높은 생산 비용 |

| 복잡한 장비 | 복잡한 장비 필요 |

| 응용 분야 | |

| 반도체 산업 | 게이트 절연막 캐패시터 절연막 금속 배선 산화막 |

| 광전 소자 | 태양 전지 박막 트랜지스터 |

| 나노 기술 | 나노 물질 합성 |

| 에너지 분야 | 연료 전지 배터리 |

| 기타 분야 | 디스플레이 코팅 촉매 센서 |

| 증착 방법 | |

| 열적 원자층 증착 | 열 에너지 이용 |

| 플라즈마 원자층 증착 | 플라즈마 이용 |

| 광화학적 원자층 증착 | 광에너지 이용 |

| 공간적 원자층 증착 | 기판 이동 및 가스 분사 |

| 원자층 에칭 | 원자층 단위의 식각 과정 |

| 전구체 | |

| 금속 전구체 | 금속 염화물, 유기 금속 화합물 |

| 산화물 전구체 | 금속 알콕사이드, 산소 가스 |

| 질화물 전구체 | 금속 아미드, 질소 가스 |

| 관련 기술 | |

| 화학 기상 증착 | 원자층 증착의 기본 원리 기술 CVD 기술 |

| 물리 기상 증착 | 원자층 증착과 다른 기술 PVD 기술 |

2. 역사

원자층 증착(Atomic Layer Deposition, ALD) 기술은 1960년대 소련과 1970년대 핀란드에서 서로 독립적으로 개발되었다.[14]

소련에서는 1960년대 레닌그라드 공과대학(LTI, 현 상트페테르부르크 국립기술대학교)의 스타니슬라프 이바노비치 콜초프(Stanislav Koltsov)와 발렌틴 보리소비치 알레스크프스키(Valentin Aleskovsky) 등이 실험을 통해 ALD의 기본 원리를 개발하고, 1965년 이 기술을 "분자층 증착(Molecular Layering, ML)"이라고 명명했다.[8] 이 연구는 기초 화학 연구부터 마이크로일렉트로닉스 응용까지 다양한 분야로 확장되었다.[8][9]

핀란드에서는 1974년 투오모 순톨라(Tuomo Suntola)가 박막 전계 발광 디스플레이(TFEL) 개발 과정에서 ALD 기술을 고안하고 "원자층 에피택시(Atomic Layer Epitaxy, ALE)"라고 이름 붙였다.[10][11] ALE 기술은 TFEL 디스플레이 생산에 처음 적용되었으며,[10] 이후 반도체 산업으로 응용 분야가 확장되면서 무어의 법칙을 지속시키는 핵심 기술 중 하나로 자리 잡았다.[10] 순톨라는 이 공로로 2018년 밀레니엄 기술상을 수상했다.[13]

두 기술의 개발자들은 1990년 핀란드에서 열린 제1회 국제 ALE 컨퍼런스에서 처음 만났으며,[10][8] 이후 헬싱키 대학교의 마르쿠 레스켈라(Markku Leskelä) 교수가 제안한 "원자층 증착(Atomic Layer Deposition, ALD)"이라는 명칭이 미국 진공 학회(American Vacuum Society)의 국제 컨퍼런스 시리즈를 통해 점차 국제적으로 통용되기 시작했다.[16]

2000년대 들어 ALD 기술은 마이크론 테크놀로지, 인텔 등 주요 반도체 기업들이 DRAM 메모리나 CMOS 공정에 필수적인 고유전율 박막을 증착하는 데 활용하면서 더욱 중요성이 커졌다.[17][18][19] 2010년에는 ALD 관련 기술인 순차 침투 합성법(SIS)이 보고되기도 했다. ALD 기술의 초기 역사를 명확히 하기 위해 2013년 'ALD 역사에 관한 가상 프로젝트'(Virtual Project on the History of ALD, VPHA)가 시작되어 관련 연구 결과를 발표하고 있다.[20][14][10][8][15]

2. 1. 소련 (분자층 증착, Molecular Layering, ML)

1960년대 소련(Soviet Union)의 레닌그라드 공과대학(Leningrad Technological Institute, LTI, 현 상트페테르부르크 국립기술대학교)에서 스타니슬라프 이바노비치 콜초프(Stanislav Koltsov)는 발렌틴 보리소비치 알레스크프스키(Valentin Aleskovsky) 등 동료들과 함께 원자층 증착(ALD)의 기본 원리를 실험적으로 개발했다.[8] 이 연구는 알레스코프스키가 1952년 그의 교수 자격 논문(habilitation thesis)에서 제안한 "틀 가설(framework hypothesis)"을 실험적으로 증명하려는 목적에서 시작되었다.[8]초기 실험은 금속 염화물과 다공성 실리카를 이용한 물 반응으로 시작되었으며, 곧 다양한 기판 재료와 평면 박막 형성 연구로 확장되었다.[8] 1965년, 알레스코프스키와 콜초프는 이 새로운 박막 증착 기술에 대해 "분자층 증착(Molecular Layering, ML)"이라는 이름을 제안했다.[8] 분자층 증착의 원리는 1971년 콜초프의 박사 학위 논문(교수 학위 논문)에 상세히 요약되어 있다.[8] 분자층 증착 연구는 기초 화학 연구뿐만 아니라 다공성 촉매, 흡착제, 마이크로일렉트로닉스 분야의 충전제 등 다양한 응용 연구까지 포괄했다.[8][9]

소련의 분자층 증착(ML)과 핀란드에서 개발된 원자층 에피택시(Atomic Layer Epitaxy, ALE)는 서로 독립적으로 발전했지만, 두 기술의 개발자들은 1990년 핀란드 에스포(Espoo)에서 열린 제1회 국제 원자층 에피택시 컨퍼런스 "ALE-1"에서 처음으로 교류했다.[10][8] 분자층 증착 연구의 중요성과 범위는 2005년 발표된 과학적 ALD 검토 논문[2]과 이후 ALD 역사에 관한 가상 프로젝트(Virtual Project on the History of ALD, VPHA) 관련 출판물들을 통해 더 널리 알려지게 되었다.[14][8][15]

2. 2. 핀란드 (원자층 에피택시, Atomic Layer Epitaxy, ALE)

1974년 핀란드의 Instrumentarium Oy에서 박막 전계 발광 디스플레이(thin-film electroluminescent displays, TFEL) 개발을 시작하면서 투오모 순톨라(Tuomo Suntola)는 원자층 증착(ALD) 기술을 고안했다.[10][11] 순톨라는 이 기술을 그리스어로 "위에 배열하다"라는 의미를 가진 에피택시(epitaxy)에서 착안하여 "원자층 에피택시(atomic layer epitaxy, ALE)"라고 명명했다.[10][11] 초기 실험은 원소 아연(Zn)과 황(S)을 사용하여 황화아연(ZnS) 박막을 성장시키는 방식으로 이루어졌다.[10][11] 박막 성장 기술로서 ALE는 20개국 이상에서 국제 특허를 받았다.[10]순톨라와 동료들은 고진공 반응기 대신 불활성 가스를 사용하는 반응기로 전환하면서 기술적인 돌파구를 마련했다. 이를 통해 금속 염화물, 황화수소, 수증기와 같은 화합물 전구체를 ALE 공정에 사용할 수 있게 되었다.[10][12] 이 기술은 1980년 SID 컨퍼런스에서 처음으로 공개되었다.[10] 당시 발표된 TFEL 디스플레이 시제품은 두 개의 산화 알루미늄 유전체 층 사이에 황화아연(ZnS) 층이 있는 구조였으며, 모든 층은 염화 아연(ZnCl2)과 황화수소(H2S), 그리고 염화 알루미늄(AlCl3)과 물(H2O)을 각각 반응물로 사용하는 ALE 공정으로 제작되었다.[10] ALE 기술이 적용된 EL 디스플레이의 최초 대규모 개념 증명 사례는 1983년 헬싱키반타 국제공항에 설치된 항공편 정보 게시판이었다.[10] TFEL 평판 디스플레이 생산은 1980년대 중반 롤야 Oy(Lohja Oy)의 올라린루오마(Olarinluoma) 공장에서 시작되었다.[10]

ALE에 대한 학문적 연구는 1970년대 순톨라가 전자 물리학을 강의했던 탐페레 공과대학교에서 시작되었고, 1980년대에는 헬싱키 공과대학교에서도 연구가 이루어졌다.[10] 1990년대까지 ALE 기술의 유일한 산업적 응용 분야는 TFEL 디스플레이 제조였다. 1987년, 순톨라는 핀란드 국영 석유 회사인 네스테(Neste Oy)가 설립한 Microchemistry Ltd.에서 광전 변환 장치(photovoltaic device) 및 불균일 촉매(heterogeneous catalyst)와 같은 새로운 응용 분야를 위한 ALE 기술 개발을 시작했다.[10] 1990년대에 Microchemistry Ltd.는 반도체 응용 분야와 실리콘 웨이퍼 가공에 적합한 ALE 반응기 개발에 집중했다.[10]

1999년 Microchemistry Ltd.와 ALE 기술은 반도체 제조 장비의 주요 공급업체인 네덜란드의 ASM 인터내셔널(ASM International)에 매각되었고, 회사는 ASM의 핀란드 자회사인 ASM Microchemistry Oy가 되었다. Microchemistry Ltd./ASM Microchemistry Oy는 1990년대 상업용 ALD 반응기의 유일한 제조업체였다.[10] 2000년대 초, 핀란드에서 축적된 ALD 반응기 관련 전문 지식은 Beneq Oy와 Picosun Oy라는 두 개의 새로운 제조업체의 탄생으로 이어졌다. Picosun Oy는 1975년부터 순톨라의 가까운 동료였던 스벤 린드포스(Sven Lindfors)가 설립했다.[10] 이후 반응기 제조업체의 수는 급격히 증가했고, 반도체 응용 분야가 ALD 기술의 산업적 돌파구가 되면서 ALD는 무어의 법칙(Moore's law)의 지속을 가능하게 하는 핵심 기술 중 하나로 자리 잡았다.[10]

투오모 순톨라는 반도체 응용 분야 ALD 기술 개발에 대한 공로로 2004년 반도체 장비 재료 국제 협회(SEMI) 유럽 어워드를 수상했으며,[10] 2018년에는 핀란드의 밀레니엄 기술상(Millennium Technology Prize)을 수상했다.[13]

한편, 1990년 핀란드 에스푸(Espoo)에서 열린 제1회 국제 원자층 에피택시 컨퍼런스 "ALE-1"에서 소련의 분자층 증착(ML) 개발자들과 핀란드의 ALE 개발자들이 처음으로 만났다.[10][8] 이 컨퍼런스에서 헬싱키 대학교의 마르쿠 레스켈라(Markku Leskelä) 교수는 화학 기상 증착(Chemical vapor deposition, CVD)과의 유사성을 고려하여 ALE 대신 "원자층 증착(atomic layer deposition, ALD)"이라는 명칭을 제안했다. 이 명칭은 약 10년 후 미국 진공 학회(American Vacuum Society)가 주관하는 국제 ALD 컨퍼런스 시리즈가 시작되면서 널리 받아들여지게 되었다.[16]

2. 3. 명칭 논쟁 및 통합

원자층 증착(ALD) 기술은 초기에 두 개의 다른 이름으로 독립적으로 개발되었다. 핀란드에서는 투오모 순톨라(Tuomo Suntola)가 고안한 원자층 에피택시(Atomic Layer Epitaxy, ALE)로,[10][11] 소련에서는 스타니슬라프 이바노비치 콜초프(Stanislav Koltsov)와 발렌틴 보리소비치 알레스크프스키(Valentin Aleskovsky) 등이 개발한 분자층 증착(Molecular Layering, ML)으로 알려졌다.[8][14]두 기술의 개발자들은 1990년 핀란드 에스포에서 열린 제1회 국제 원자층 에피택시 컨퍼런스 "ALE-1"에서 처음으로 만났다.[10][8] 이 만남에도 불구하고, 영어권 사용자가 주도하는 ALD 커뮤니티 내에서는 소련의 분자층 증착(ML) 연구가 오랫동안 주변적인 지식으로 취급되었다. 2005년에 발표된 한 과학 총설 논문에서 ML 연구의 광범위함이 소개되면서 비로소 주목받기 시작했다.[2]

'원자층 증착(Atomic Layer Deposition, ALD)'이라는 명칭은 기존의 ALE 대신 화학 기상 증착(Chemical Vapor Deposition, CVD)과의 유사성을 고려하여 제안되었다. 이 명칭은 1990년 ALE-1 컨퍼런스에서 헬싱키 대학교의 마르쿠 레스켈라(Markku Leskelä) 교수가 처음 제안한 것으로 기록되어 있다. 그러나 이 명칭이 국제적으로 널리 받아들여지기까지는 약 10년의 시간이 걸렸으며, 미국 진공 학회(American Vacuum Society)가 주관하는 국제 ALD 컨퍼런스 시리즈가 시작되면서 보편화되었다.[16]

ALD 기술의 초기 역사를 명확히 하기 위해 2013년 여름, 'ALD 역사에 관한 가상 프로젝트'(Virtual Project on the History of ALD, VPHA)가 설립되었다.[20] 이 프로젝트는 ALE와 ML이라는 이름으로 진행된 ALD의 역사적 발전을 검토하는 여러 연구 결과물을 발표했다.[14][10][8][15]

2. 4. 2000년대 이후 발전

2000년, 마이크론 테크놀로지(Micron Technology)의 구르테지 싱 산두(Gurtej Singh Sandhu)와 중 트엉 도안(Trung T. Doan)은 DRAM(Dynamic random-access memory) 메모리 장치를 위한 고유전율(high-κ dielectric) 박막의 원자층 증착(ALD) 개발을 시작했다. 이는 90nm 노드(Semiconductor node) DRAM을 시작으로 비용 효율적인 반도체 메모리(semiconductor memory) 구현을 촉진하는 데 기여했다.[17][18] 이후 인텔(Intel Corporation)은 45nm CMOS 기술(45 nm CMOS technology)에 게이트 유전체 증착을 위해 원자층 증착(ALD)을 사용했다고 보고했다.[19]2010년에는 아르곤 국립연구소 연구원들이 순차 침투 합성법(Sequential Infiltration Synthesis, SIS) 기술을 처음 보고했으며, 이는 원자층 증착(ALD) 관련 기술군에 추가되었다.

3. 원리 및 반응 메커니즘

원자층 증착(Atomic Layer Deposition, ALD)은 박막을 성장시키는 기술로, 기판 표면에 두 종류 이상의 기체 상태 전구체를 번갈아 순차적으로 공급하는 방식이다.[71][2] 이는 반응기 내에 전구체들이 동시에 존재하는 화학 기상 증착(CVD)과는 구별된다. ALD의 가장 큰 특징은 자기 제한적 반응(self-limiting reaction)으로, 각 단계에서 전구체 분자가 표면의 반응 가능한 자리에 모두 결합하고 나면 더 이상 반응이 진행되지 않아 스스로 멈춘다.[71][2] 이 원리 덕분에 한 번의 공정 주기(사이클)마다 증착되는 물질의 양이 일정하게 제어되며, 사이클 수를 조절하여 원자 수준의 정밀도로 박막 두께와 조성을 제어할 수 있다.[71][2][21] 실제 반응 메커니즘은 사용되는 물질과 공정 조건에 따라 매우 다양하며, 산화물, 금속, 질화물 등 다양한 재료 증착에 활용되고 있다.[4][24]

3. 1. 기본 원리

원자층 증착(ALD) 공정에서는 기판 표면에 두 종류 이상의 기체 상태 전구체(반응물)를 번갈아 순차적으로 노출시켜 박막을 성장시킨다.[71][2] 이는 반응기 내에 전구체들이 동시에 존재하는 화학기상증착(CVD) 방식과는 다르다. ALD에서는 각 전구체가 서로 겹치지 않는 별도의 단계(펄스)로 주입된다.ALD의 핵심 원리는 자기 제한적 반응(self-limiting reaction)이다. 각 단계에서 주입된 전구체 분자는 기판 표면에 있는 유한한 수의 반응성 부위와만 반응한다. 일단 표면의 모든 반응 가능한 자리가 전구체 분자로 채워지면(포화 상태), 더 이상 반응이 일어나지 않고 성장이 스스로 멈춘다.[71][2] 이 때문에 한 번의 전구체 노출(펄스)로 증착되는 물질의 양은 표면 상태와 전구체의 화학적 특성에 따라 결정되며, 일정량을 넘지 않는다.

전형적인 2원(binary) ALD 공정은 다음과 같은 순서로 진행된다.

1. 첫 번째 전구체(A)를 반응기 내로 주입한다. 전구체 A는 기판 표면의 반응성 부위와 결합한다.

2. 표면이 전구체 A로 포화되면, 반응기 내에 남아있는 과잉 전구체 A 분자와 반응 부산물을 배출(퍼지, purge)한다.

3. 두 번째 전구체(B)를 반응기 내로 주입한다. 전구체 B는 표면에 흡착된 전구체 A와 반응하여 박막의 한 층을 형성한다.

4. 표면 반응이 완료되면, 반응기 내에 남아있는 과잉 전구체 B 분자와 반응 부산물을 배출(퍼지)한다.

이러한 '주입-퍼지-주입-퍼지' 순서를 ALD 사이클이라고 부른다.[21] ALD 공정을 설명할 때는 각 전구체의 주입 시간과 퍼지 시간을 명시하며, 박막의 두께는 성장 속도보다는 사이클당 성장률(growth per cycle, GPC)로 표현한다.[21] 원하는 두께의 박막을 얻기 위해 이 사이클을 반복하며, 사이클 수를 조절함으로써 원자 수준의 정밀도로 박막 두께를 제어할 수 있다.[71][2]

각 반응 단계에서 자기 제한적 반응이 제대로 일어나려면 충분한 시간을 주어 표면이 전구체로 완전히 덮이도록(포화 상태) 해야 한다. 포화에 도달하는 데 필요한 시간은 전구체의 압력과 표면에서의 부착 확률(sticking probability)에 따라 달라진다.[22] 단위 면적당 흡착 속도()는 다음과 같이 표현할 수 있다.[23]

:

여기서 는 부착 확률이고, 는 단위 면적당 시간당 표면에 도달하는 전구체 분자의 수(입사 몰 유량 또는 플럭스)이다. ALD 공정의 중요한 특징은 부착 확률 가 시간에 따라 변한다는 점이다. 반응 초기에는 부착 확률이 높지만, 표면에 분자가 흡착될수록 반응할 자리가 줄어들어 부착 확률이 점차 감소하고, 표면이 완전히 포화되면 0이 된다.[23]

실제 반응 메커니즘의 구체적인 세부 사항은 사용되는 전구체와 기판의 종류에 따라 매우 다양하다. 산화물, 금속, 질화물, 황화물, 칼코겐화물, 플루오르화물 등 다양한 종류의 재료를 증착하기 위한 수백 가지의 ALD 공정이 개발되었으며,[4] 이러한 공정들의 메커니즘을 밝히는 것은 활발한 연구 분야이다.[24]

3. 2. 반응 메커니즘

전형적인 원자층 증착(ALD) 공정에서는 기판이 두 종류의 기체 반응물(일반적으로 전구체라 불림) A와 B에 순차적이고 중복되지 않게 노출된다. 박막 성장이 정상 상태로 진행되는 화학기상증착(CVD)과 달리, ALD에서는 각 반응물이 표면과 자기 제한적인 방식으로 반응한다. 이는 반응물 분자가 표면에 있는 유한한 수의 반응성 부위와만 반응할 수 있기 때문이다.[71][2]표면의 모든 반응성 부위가 반응물 A로 채워지면 성장은 멈춘다. 반응하지 않고 남아있는 A 분자는 반응기 밖으로 배출(퍼지)시킨 후, 반응물 B를 반응기로 주입한다. A와 B에 대한 노출과 퍼지를 번갈아 반복하며 박막을 한 층씩 증착시킨다. 이처럼 ALD 공정을 설명할 때는 각 전구체에 대한 주입 시간(표면 노출 시간)과 퍼지 시간(과잉 전구체 배출 시간)을 모두 명시한다. 두 반응물 A와 B에 대한 '주입-퍼지-주입-퍼지' 순서가 하나의 ALD 사이클을 구성한다. 따라서 ALD 공정은 성장 속도보다는 사이클당 성장률로 기술된다.[21]

ALD 공정에서는 각 반응 단계마다 충분한 시간을 확보하여 표면 반응 부위가 전구체 분자로 완전히 덮이는, 즉 포화 상태에 도달하도록 하는 것이 중요하다. 포화에 도달하는 시간은 주로 전구체의 압력과 표면에서의 부착 확률(sticking probability)이라는 두 요소에 의해 결정된다.[22] 단위 면적당 흡착 속도()는 다음과 같이 표현할 수 있다.

:

여기서 는 흡착 속도, 는 부착 확률, 는 기체 분자의 입사 유량(incident molar flux)이다.[23] ALD의 핵심 특징 중 하나는 이 부착 확률 가 시간에 따라 변한다는 점이다. 반응이 진행되어 표면에 더 많은 분자가 흡착함에 따라 부착 확률은 점차 감소하며, 표면이 완전히 포화되면 0이 된다.

구체적인 반응 메커니즘은 특정 ALD 공정에 따라 매우 다양하다. 현재까지 산화물, 금속, 질화물, 황화물, 칼코겐화물, 플루오르화물 등 다양한 재료를 증착하기 위한 수백 가지의 공정이 개발되었으며,[4] 이러한 ALD 공정들의 세부적인 반응 메커니즘을 밝히는 것은 여전히 활발한 연구 분야이다.[24]

3. 2. 1. 열 ALD

열 ALD(Atomic Layer Deposition)는 리간드 교환 또는 연소형 표면 반응을 이용하며, 상온(약 20°C)에서 350°C까지의 온도 범위에서 진행된다.[25] 이 방식은 표면 반응을 통해 이루어지므로, 기판의 형태(종횡비)나 반응기 설계에 크게 영향을 받지 않고 박막의 두께를 정밀하게 제어할 수 있다는 장점이 있다.[71]

가장 잘 알려진 열 ALD 공정 중 하나는 트리메틸알루미늄(TMA)과 물(수증기, H₂O)을 이용하여 Al₂O₃ 박막을 만드는 과정이다. 이 공정은 다음과 같은 단계로 진행된다.[71]

1. TMA 노출: TMA가 기판 표면에 해리 흡착하여 화학적으로 결합한다. 이 과정에서 표면은 AlCH₃ 그룹으로 덮이게 된다. 반응에 참여하지 않고 남아있는 TMA 분자는 반응기 밖으로 배출시킨다.

2. H₂O 노출: 기판 표면을 H₂O 증기에 노출시킨다. H₂O 분자는 표면의 –CH₃ 그룹과 반응하여 부산물로 메탄(CH₄)을 생성한다. 이 반응 결과, 표면에는 히드록실화된 Al₂O₃가 남게 된다.

이 두 단계를 반복하여 원하는 두께의 Al₂O₃ 박막을 증착할 수 있다.

3. 2. 2. 플라즈마 ALD (PEALD)

플라스마-강화 원자층 증착(Plasma Enhanced ALD, PEALD)은 증착 과정에 플라스마를 활용하는 원자층 증착(ALD) 방식이다.[71] 플라스마는 반응성이 매우 높기 때문에, 박막의 품질을 저하시키지 않으면서도 증착 온도를 낮출 수 있다는 장점이 있다. 또한, 일반적인 열 ALD 방식에 비해 더 넓은 범위의 전구체를 사용할 수 있어, 결과적으로 더 다양한 종류의 재료를 증착하는 것이 가능하다.[71] 플라스마를 이용한 원자층 증착(Plasma-Assisted ALD, PA-ALD)이라고도 한다.3. 2. 3. 공간 ALD (Spatial ALD)

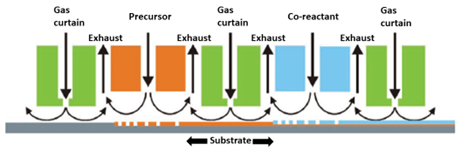

기존의 시간 분리 원자층 증착(temporal ALD) 방식은 전구체와 반응물을 퍼지 단계를 통해 시간적으로 분리하여 공급한다. 이와 달리, 공간 분리 원자층 증착(spatial ALD, s-ALD)은 전구체와 반응물을 서로 다른 위치에서 동시에 공급하여 공간적으로 분리하는 방식이다.

공간 ALD 공정에서는 일반적으로 대기압 하에서 전구체와 반응물이 연속적으로 공급된다. 이때 기체 상태의 전구체와 반응물이 직접 섞여 원하지 않는 화학 기상 증착(CVD)과 같은 기상 반응이 일어나는 것을 막기 위해, 두 기체 흐름 사이에 질소와 같은 비활성 기체를 이용한 '기체 커튼'을 형성한다. 이러한 기체 커튼은 일반적으로 질소 주입 및 배출 위치로 구성된다(그림 참조). 증착 대상인 기판은 이 서로 다른 기체 영역 사이를 이동하게 되며, 기판 표면에서 각 전구체/반응물과의 자기 제한 반응이 순차적으로 일어나면서 박막이 형성된다.

이 방식은 전구체와 반응물을 교대로 주입하고 퍼지하는 시간을 기다릴 필요가 없어 공정 속도를 크게 높일 수 있다. 예를 들어, Al₂O₃ 증착의 경우, 기존 ALD의 증착 속도가 시간당 100nm에서 300nm 수준인 반면, 공간 ALD로는 분당 60nm까지 속도를 높일 수 있다.[5]

공간 ALD는 기판이 연속적으로 이동하며 증착이 이루어지는 인라인(in-line) 공정이 가능하므로, 대량 생산 라인이나 롤투롤 공정에 매우 적합하다. 이러한 장점 덕분에 수분이나 산소의 투과를 막는 차단막, 실리콘 태양 전지의 효율을 높이는 패시베이션 층, 배터리의 성능을 개선하는 기능성 층 증착 등에 널리 활용되고 있다.

공간 ALD 공정의 화학 반응 메커니즘은 기본적으로 시간 분리 ALD와 유사하며, 연구된 재료에는 Al₂O₃, 알루미늄(Al) 또는 갈륨(Ga)이 도핑된 ZnO, SiO₂, In₂O₃, InZnO, LIPON, Zn(O,S), SnOₓ, TiOₓ과 같은 다양한 무기 금속 산화물이 포함된다. 또한, Pt, Ir, Ru과 같은 PMG 금속 증착도 가능하다. 더 나아가 무기 원자와 유기 분자를 번갈아 반응시켜 유기 박막을 형성하는 분자층 증착(MLD) 공정에도 응용될 수 있다.

한편, 플라즈마나 오존을 반응물로 사용하여 공정 온도를 낮출 수 있는 플라즈마 증강 공간 ALD(PE-sALD) 또는 오존 증강 공간 ALD(O₃-sALD) 기술도 시연되었다.

3. 2. 4. 광 보조 ALD

광 보조 원자층 증착은 자외선을 이용하여 기판 표면의 반응 속도를 높이는 방식이다.[71] 플라즈마 보조 원자층 증착(PEALD)처럼 반응 온도를 낮출 수 있다는 장점이 있다.[71] 플라즈마를 이용하는 방식과 비교하면 활성화 정도는 약하지만, 빛의 파장, 세기, 조사 시간을 조절하여 반응을 더 쉽게 제어할 수 있다는 특징이 있다.[71]3. 2. 5. 금속 ALD

구리 금속 ALD는 집적회로 상호연결 재료로서 구리의 중요성 때문에 많은 관심을 받고 있다.[26] 구리는 양(+)의 표준 전극 전위를 가지고 있어[27] 1주기 전이 금속 중 가장 쉽게 환원될 수 있다. 이 때문에 수소 기체를 공반응물로 사용하는 등 다양한 ALD 공정이 개발되었다.[26][28] 낮은 표면 거칠기를 가진 연속적인 박막을 얻기 위해서는 구리 금속 ALD를 100°C 이하에서 수행하는 것이 이상적인데,[29] 더 높은 온도에서는 증착된 구리가 응집될 수 있기 때문이다.[30]일부 금속은 금속 할라이드와 실리콘 전구체(예: 실란(SiH4), 디실란(Si2H6))를 반응물로 사용하는 플루오로실란 제거 반응을 통해 ALD 방식으로 성장시킬 수 있다. 이 반응들은 안정한 Si–F 결합이 형성되면서 매우 큰 열을 방출(발열 반응)하는 특징이 있다.[24] 플루오로실란 제거 반응으로 증착되는 금속에는 텅스텐(W)[31]과 몰리브덴(Mo)[32] 등이 있다. 예를 들어, 육플루오린화 텅스텐(WF6)과 디실란(Si2H6)을 반응물로 사용하는 텅스텐 금속 ALD의 표면 반응은 다음과 같이 나타낼 수 있다.[31][33]

WSiF2H* + WF6 → WWF5* + SiF3H

WF5* + Si2H6 → WSiF2H* + SiF3H + 2 H2

전체 ALD 반응은 다음과 같다.[24]

WF6 + Si2H6 → W + SiF3H + 2 H2, ∆H = –181 kcal

텅스텐 ALD의 사이클당 성장 속도는 증착 온도(177°C~325°C)와 Si2H6 반응물 노출량(~104~106 L)에 따라 4~7 Å/cycle 범위에서 다양하다. 이러한 요인들은 Si–H 결합에 대한 Si2H6 삽입 반응에 영향을 미치며,[34][35] 텅스텐 ALD 성장 과정에서 실리콘 CVD가 부수적으로 기여할 수도 있다.[24]

다른 많은 금속들은 매우 음(-)의 전기화학적 전위를 가지기 때문에 열 ALD 방식으로는 증착이 어렵거나 현재로서는 불가능하다. 하지만 최근 새로운 강력한 환원제들이 개발되면서, 여러 전기 양성 금속들에 대한 저온 열 ALD 공정이 처음으로 보고되었다. 크롬(Cr) 금속은 크롬 알콕사이드 전구체와 BH3(NHMe2)를 사용하여 증착되었고,[36] 티타늄(Ti)과 주석(Sn) 금속은 각각의 금속 염화물(MCl4, M = Ti, Sn)과 비스(트리메틸실릴) 6원환 화합물을 이용하여 성장시켰다.[37][38] 알루미늄(Al) 금속은 알루미늄 디하이드라이드 전구체와 염화알루미늄(AlCl3)를 사용하여 증착되었다.[39]

금속 ALD 기술 개발의 주요 동기는 다음과 같다.

- 구리 배선 및 텅스텐 플러그 제작, 또는 구리 전기도금을 위한 구리 시드층[49] 및 텅스텐 CVD를 위한 텅스텐 시드층 형성

- 구리 배선의 확산 방지막 역할을 하는 전이 금속 질화물(예: TiN, TaN, WN) 증착

- 강유전체 RAM(FRAM) 및 DRAM 커패시터 전극용 귀금속 증착

- 듀얼 게이트 MOSFET 제작을 위한 고일함수 또는 저일함수 금속 증착

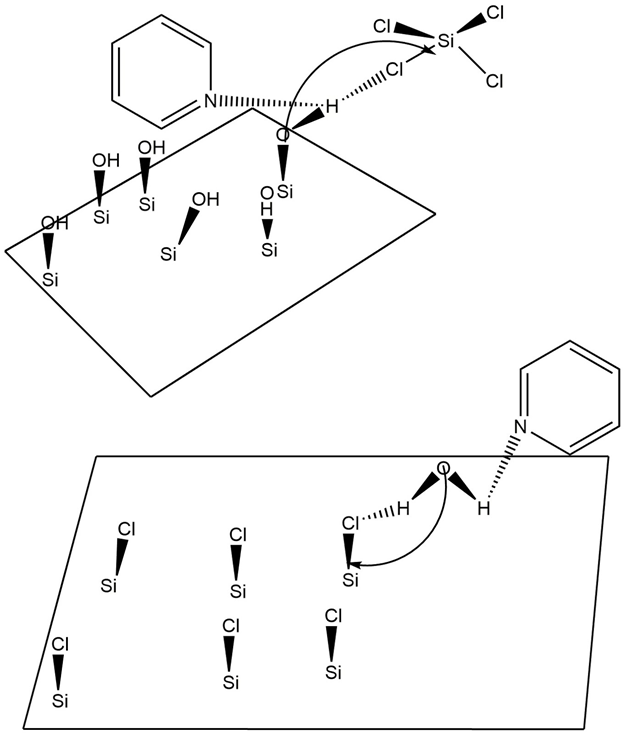

3. 2. 6. 촉매 SiO₂ ALD

SiO₂ 원자층 증착(ALD) 공정에서 촉매의 사용은 신뢰할 수 있는 박막 증착에 매우 중요하다.[24] 촉매가 없으면 SiO₂ 형성을 위한 표면 반응 속도가 매우 느리고, 반응을 진행시키기 위해 매우 높은 온도가 필요하다. SiO₂ ALD에는 주로 NH₃나 피리딘과 같은 루이스 염기가 촉매로 사용된다. 이러한 루이스 염기는 테트라에톡시실란(TEOS)과 같은 다른 실리콘 전구체와 함께 사용될 수도 있다.[24]촉매 작용 원리는 루이스 염기가 표면의 SiOH* 그룹이나 반응물인 물(H₂O) 분자와 수소 결합을 형성하는 것으로 여겨진다. 루이스 염기가 SiOH* 그룹과 수소 결합을 형성하면, Si-O-H 결합 중 산소와 수소 사이의 결합이 약해지면서 산소 원자가 더 강한 친핵체로 작용하게 된다. 이로 인해 SiCl₄ 분자 내에서 양전하를 띠는 실리콘(Si) 원자가 이 산소의 공격을 받기 쉬워진다. 마찬가지로, 루이스 염기가 물 분자와 수소 결합을 형성하면 물 분자의 산소 원자 역시 강한 친핵체가 되어, 표면에 있는 SiCl* 그룹의 실리콘 원자를 효과적으로 공격할 수 있다.[40]

이처럼 루이스 염기 촉매는 SiO₂ ALD 공정에서 거의 필수적이다. 촉매를 사용하지 않을 경우, 반응 온도는 325°C를 초과해야 하며 압력도 10³ torr 이상이 필요하다. 반면, 루이스 염기 촉매를 사용하면 일반적으로 32°C 정도의 상대적으로 낮은 온도에서도 공정이 가능하며, 이때 일반적인 증착 속도는 사이클당 1.35 옹스트롬이다.

SiO₂ ALD의 주요 표면 반응과 전체 반응식은 다음과 같다.

:'''표면 반응'''

:: SiOH* + SiCl₄ → SiOSiCl₃* + HCl

:: SiCl* + H₂O → SiOH* + HCl

:'''전체 반응'''

:: SiCl₄ + 2H₂O → SiO₂ + 4 HCl

4. 응용 분야

ALD(Atomic Layer Deposition)는 원자층 수준에서 박막 두께와 재질을 정밀하게 제어할 수 있으며, 매우 얇고 균일하며 치밀한 박막 형성이 가능하다는 특징을 가진다.[3] 이러한 장점 덕분에, 특히 무어의 법칙에 따른 반도체 소자 미세화 요구가 커지면서 ALD 기술에 대한 연구 개발이 매우 활발하게 이루어지고 있다. 수백 가지의 서로 다른 공정이 발표되었지만, 그중에는 표준적인 ALD 공정과는 거리가 먼 것도 있다.

ALD 기술은 다양한 산업 분야에서 응용되고 있으며, 특히 마이크로일렉트로닉스 분야에서의 활용이 두드러진다. 금속 ALD에 대한 관심은 다음과 같은 필요성에 의해 주도되고 있다.

- 구리 배선 형성 시 필요한 구리 시드층[49] 및 텅스텐 플러그 형성을 위한 텅스텐 시드층

- 구리 배선의 확산을 막기 위한 전이 금속 질화물(예: TiN, TaN, WN) 장벽층

- 강유전체 랜덤 액세스 메모리(FRAM) 및 DRAM 커패시터 전극용 귀금속

- 듀얼 게이트 MOSFET을 위한 고/저일함수 금속

이 외에도 ALD는 태양광 발전, 바이오메디컬 코팅, 광학 코팅, 에너지 저장 등 다양한 분야에서 그 응용 가능성을 넓혀가고 있다. 각 응용 분야에 대한 자세한 내용은 아래 하위 섹션에서 다룬다.

4. 1. 마이크로일렉트로닉스

ALD(Atomic Layer Deposition)는 박막의 두께를 원자 수준에서 정밀하게 제어하고, 복잡한 구조에도 매우 균일하게 증착할 수 있으며, 고품질의 박막을 만들 수 있다는 장점 때문에 마이크로일렉트로닉스 제조 공정에서 핵심 기술로 활용된다.[3] 마이크로일렉트로닉스 분야에서 ALD는 특히 다음과 같은 다양한 영역에서 중요한 역할을 수행하고 있다.- 고유전율(high-k) 게이트 산화물: 반도체 소자가 미세화됨에 따라 발생하는 누설 전류 문제를 해결하기 위해, 기존의 SiO₂ 대신 유전율이 높은 물질(high-k)을 게이트 절연막으로 사용한다. ALD는 이러한 고유전율 물질을 원자층 수준의 정밀도로 얇고 균일하게 증착하는 데 필수적이다. 초박막 두께 제어가 중요한 이 분야에서 ALD는 45nm 이하 공정 세대부터 그 중요성이 더욱 커지고 있다.[3]

- 금속 배선 및 배리어 금속: 현대 집적 회로의 구리 배선은 주변 물질로 확산되거나 오염되는 것을 막기 위해 배리어 금속 층으로 둘러싸여야 한다. ALD는 TiN[48], TaN[48]과 같은 배리어 물질을 매우 얇고 균일하게, 복잡한 3차원 구조에도 빈틈없이 증착할 수 있어 이 목적에 매우 적합하다. 금속화 공정에서 균일한 박막 형성이 중요하며, 65nm 공정 세대부터 ALD가 주류 생산에 사용될 것으로 예상된다.[3]

- DRAM 커패시터: 메모리 집적도를 높이기 위해 점점 더 작고 복잡한 3차원 구조(스택형 또는 트렌치형)로 제작되는 DRAM 커패시터에 필요한 유전체 박막을 증착하는 데 ALD가 핵심적인 역할을 한다. ALD의 뛰어난 균일성과 단차 피복성(conformality)은 특히 100nm 이하 크기의 미세 구조 제작에 필수적인 기술로 여겨진다.[3][53]

- 자기 기록 헤드: 하드 디스크 등에서 데이터를 기록하는 자기 기록 헤드 제작에도 ALD 기술이 응용된다. Al₂O₃을 ALD로 증착하여 매우 얇고 균일한 절연층을 형성하는데,[51] 이는 자화 패턴을 더욱 정밀하게 제어하여 기록 품질을 향상시키는 데 기여한다.[50]

- 기타 응용: 이 외에도 ALD는 MOSFET 게이트 스택, 비휘발성 강유전체 메모리 등 다양한 마이크로일렉트로닉스 소자 제작 공정에 활용되고 있다.[3]

4. 1. 1. 고유전율 게이트 산화막

고유전율(high-k) 산화물인 Al₂O₃, ZrO₂, HfO₂ 증착은 ALD 분야에서 가장 광범위하게 연구된 영역 중 하나이다.[1][2] 고유전율 산화물에 대한 연구는 MOSFET에서 일반적으로 사용되는 SiO₂ 게이트 유전체가 이하로 미세화될 때 발생하는 높은 터널링 전류 문제에서 비롯된다.[1][2] 게이트 절연막이 너무 얇으면 전자가 누설되는 현상이 심해져 소자의 성능이 저하되고 전력 소모가 커지기 때문이다.이러한 문제를 해결하기 위해 SiO₂보다 유전율이 높은 물질, 즉 고유전율 산화물을 사용하면 필요한 커패시턴스 밀도를 얻기 위해 더 두꺼운 게이트 절연막을 만들 수 있으므로, 구조를 통과하는 터널링 전류를 줄일 수 있다.[1][2]

ALD는 이러한 고유전율 산화물 박막을 원자층 수준에서 정밀하게 제어하며 증착할 수 있는 핵심 기술로 주목받고 있다. ALD는 뛰어난 두께 균일성과 표면 평탄도를 가진 고품질 박막을 형성할 수 있어, 초미세 반도체 공정의 요구 조건을 만족시킨다.[3] 특히 초박막 제어가 필수적인 고유전율 게이트 산화물의 경우, ALD는 45 nm 기술에서 더 널리 사용될 가능성이 높다.[3] 실제로 인텔(Intel)은 45nm CMOS 기술에서 고유전율 게이트 절연막 형성에 ALD를 사용하고 있다고 보고하고 있다.[2]

4. 1. 2. 금속 배선

현대 집적 회로에서는 구리 배선이 널리 사용된다. 하지만 구리는 주변 물질(절연체, 실리콘 기판 등)로 쉽게 확산되어 회로 성능을 저하시키거나, 반대로 주변 물질의 원소가 구리 배선으로 확산되어 오염을 일으킬 수 있다.[48] 이러한 문제를 방지하기 위해 각 구리 배선 주위를 배리어 금속(barrier metal) 층으로 감싸야 한다. 이 배리어 금속은 구리의 확산을 막는 동시에, 외부 물질로부터 구리를 보호하는 역할을 한다.[48]배리어 금속으로 사용되기 위해서는 다음과 같은 엄격한 요구 조건을 만족해야 한다:[48]

- 고순도 및 치밀성: 불순물이 적고 조직이 촘촘해야 확산 방지 효과가 크다.

- 전도성: 배선 자체의 전기적 특성을 해치지 않아야 한다.

- 균일성 및 박막: 매우 얇으면서도 전체 표면에 걸쳐 두께가 일정해야 한다.

- 우수한 접착력: 금속 배선 및 절연체와 잘 붙어 있어야 한다.

ALD(Atomic Layer Deposition) 기술은 원자층 단위로 박막을 쌓아 올리는 방식으로, 위에서 언급된 배리어 금속의 요구 조건을 충족시키는 데 매우 효과적이다. 특히 매우 얇고 균일하며 복잡한 3차원 구조에도 빈틈없이(conformal) 증착할 수 있다는 장점이 있다.[48]

따라서 ALD는 TiN[48], TaN[48], WN 등과 같은 전이 금속 질화물을 구리 배선의 배리어 층으로 증착하는 데 유용하게 사용된다. 이들 전이 금속 질화물은 우수한 확산 방지 특성과 전기적 특성을 가지고 있어 배리어 금속으로 주목받고 있다.[48] 가장 많이 연구된 것은 TiCl4과 NH3를 이용한 TiN 증착이다.[48]

금속 배선 공정에서 ALD 기술이 주목받는 구체적인 이유는 다음과 같다:

- 구리 배선 및 텅스텐 플러그 형성을 위한 시드층(seed layer) 증착: 구리 전기도금[49]이나 텅스텐 화학기상증착(CVD) 공정 전에 ALD로 얇고 균일한 시드층을 형성하여 후속 공정의 효율과 품질을 높인다.

- 구리 배선의 확산 방지막(배리어) 증착: 앞서 설명한 TiN, TaN, WN 등의 전이 금속 질화물을 증착한다.

- FRAM 및 DRAM 커패시터 전극용 귀금속 증착.

- 듀얼 게이트 MOSFET용 고/저일함수 금속 증착.

4. 1. 3. DRAM 커패시터

동적 랜덤 액세스 메모리(DRAM) 커패시터 제작은 원자층 증착(ALD) 기술의 주요 응용 분야 중 하나이다.[52] 각각의 DRAM 셀은 1비트의 데이터를 저장하며, 하나의 MOS 트랜지스터와 하나의 커패시터로 구성된다. 메모리 집적도를 높이기 위해서는 커패시터의 크기를 줄이는 것이 필수적이다.하지만 단순히 크기만 줄이면 커패시턴스(정전 용량)가 감소하여 데이터 저장 능력이 떨어질 수 있다. 이를 해결하기 위해 커패시턴스를 유지하면서 크기를 줄일 수 있는 스택형(stacked) 또는 트렌치형(trench)과 같은 3차원 구조의 커패시터가 개발되었다.[52] 특히 반도체 공정이 미세화되면서 트렌치형 커패시터를 제작하는 데 어려움이 따랐다.

원자층 증착(ALD) 기술은 이러한 문제를 해결하는 데 중요한 역할을 한다. ALD는 원자층 단위로 박막을 쌓아 올리기 때문에, 복잡한 3차원 구조에서도 매우 균일하고 얇은 박막을 형성할 수 있다. 이를 통해 트렌치 구조를 100nm 이하의 크기로 미세화하는 것이 가능해졌다.[53] ALD는 단일 재료 층을 정밀하게 증착할 수 있어 재료 선택과 제어가 용이하며, 유전체나 배리어(barrier)와 같은 박막을 효과적으로 형성할 수 있다.[53] 다만, 기판의 반응 사이트 부족이나 낮은 공정 온도 등으로 인해 불완전한 박막 성장이 발생할 수 있다는 점은 고려해야 할 부분이다.[53]

4. 2. 태양광 발전

원자층 증착(ALD) 기술은 태양전지 분야에서 그 중요성이 점차 커지고 있다. 과거에는 결정질 실리콘(c-Si) 태양전지의 표면 패시베이션 층, 구리 인듐 갈륨 셀레나이드(CIGS) 태양전지의 완충 층, 그리고 염료감응 태양전지(DSSC)의 장벽층 증착 등에 주로 활용되었다.[54] 예를 들어, Schmidt 연구팀은 태양전지 응용 분야에서 원자층 증착 방식으로 성장시킨 Al2O3의 유용성을 입증했으며, 이는 PERC(Passivated Emitter and Rear Cell, 패시베이션 에미터 및 후면 전지) 태양전지 개발에서 표면 패시베이션 층으로 사용되었다.[55]최근에는 페로브스카이트 태양전지의 전하 수송층(Charge Transport Layer, CTL) 증착을 위해 ALD 기술을 활용하는 연구가 활발히 진행되고 있다. ALD는 박막의 두께를 정밀하게 제어하면서도 고품질의 균일한 막을 형성할 수 있다는 장점이 있다. 이를 통해 전하 수송층과 페로브스카이트 층 사이의 계면을 효과적으로 조절할 수 있으며, 넓은 면적에 걸쳐 핀홀(작은 구멍) 없이 균일한 박막을 얻는 데 유리하다. 이러한 특성 덕분에 ALD는 페로브스카이트 태양전지의 성능을 높이고 안정성을 확보하는 데 유망한 기술로 평가받고 있다.[56]

4. 3. 바이오메디컬

생체의료 기기, 특히 체내 이식 장치의 표면 특성을 이해하고 명확히 하는 것은 생체의료 산업에서 매우 중요하다. 재료는 표면에서 생체 환경과 상호작용하므로, 표면 특성이 재료와 생체 환경 간의 상호작용, 즉 생체 적합성을 크게 좌우한다. 표면의 화학적 성질과 형태는 단백질 흡착, 세포와의 상호작용, 면역 반응 등에 영향을 미친다.[58]현재 바이오메디컬 응용 분야에서 원자층 증착(ALD) 기술은 유연 센서 제작, 나노다공성 막의 표면 개질, 고분자 ALD 및 얇은 생체 적합성 코팅 생성 등에 활용된다. 예를 들어, 진단 도구인 광 도파관 센서를 제작하기 위해 TiO2 박막을 증착하는 데 사용되었다.[59] 또한 운동선수의 의류에 통합되어 움직임이나 심박수를 감지하는 유연 센서 장치를 만드는 데에도 유용하다. ALD는 저온 증착이 가능하므로 유연한 유기 전계 효과 트랜지스터(OFET) 제조 공정에도 적용될 수 있다.[60]

나노다공성 재료는 약물 전달, 이식물, 조직 공학 등 생체의료 산업 전반에서 활용이 증가하고 있다. 나노다공성 재료의 표면 개질에 ALD를 사용하는 장점은, 다른 많은 방법과 달리 반응의 포화 및 자기 제한적 특성 덕분에 깊이 들어간 표면이나 계면까지도 균일하게 코팅할 수 있다는 점이다.[71] ALD 공정의 높은 등각성(conformality) 코팅은 기공 내부를 완전히 덮을 수 있어, 나노다공성 표면의 기공 크기를 더욱 정밀하게 제어(감소)할 수 있으며, 이는 특정 응용 분야에서 유리하게 작용할 수 있다.[61]

4. 4. 기타 응용 분야

광 집적 회로(PICs) 분야에서도 원자층 증착(ALD) 기술이 활용된다. 전자 집적 회로와 유사하게 광 집적 회로가 발전하면서 다양한 온칩 광소자 구조가 필요해졌는데, 그 예로 나노포토닉 커플러가 있다. 이는 광 도파관의 교차 지점에서 마이크로미터 크기의 빔 스플리터 역할을 한다.[57] 나노포토닉 커플러 제작 시, 먼저 식각 공정을 통해 높은 종횡비(가로세로비)를 가진 트렌치(약 100nm 폭 x 4μm 깊이)를 만든 후, ALD를 이용해 산화알루미늄(Al2O3)으로 채워 광학적으로 우수한 품질의 계면을 형성한다.또한, ALD는 플라스틱의 투과 방지막으로도 사용될 수 있다.[62] 대표적인 예로 플라스틱 기판 위에 제작된 유기 발광 다이오드(OLED)를 습기나 산소로부터 보호하기 위해 봉지(encapsulation)하는 데 널리 쓰인다.[65][66] 더 나아가, 3D 프린팅으로 제작된 플라스틱 부품 표면에 ALD를 적용하여 기체 방출(outgassing)을 줄임으로써 진공 환경에서의 사용 적합성을 높일 수 있다. 이는 반도체 공정이나 우주 응용 분야에서 저렴하게 맞춤형 도구를 제작하는 길을 열어준다.[67] 롤투롤(Roll-to-roll) 공정에서도 플라스틱 필름 위에 장벽층(barrier layer)을 형성하는 데 ALD 기술이 활용될 수 있다.[68]

5. 장점 및 한계

원자층 증착(ALD) 기술은 원자 수준에서 박막 두께를 정밀하게 제어하고 복잡한 3차원 구조에도 매우 균일한 코팅을 가능하게 하는 등 여러 장점을 가진다.[71][24] 특히 비교적 낮은 온도에서 공정이 가능하여 열에 민감한 기판에도 적용할 수 있다는 점은 마이크로일렉트로닉스 및 나노기술 분야에서 큰 이점으로 작용한다.[71][24]

그러나 ALD 공정은 증착 속도가 매우 느리고,[2][69] 사용할 수 있는 전구체와 기판의 종류가 제한적이며,[69][70] 초기 장비 투자 비용 및 공정 개발 비용이 높다는[70][69] 한계점도 가지고 있다. 또한, 최종 박막에 미량의 불순물이 남을 수 있다는 점도 고려해야 할 사항이다.[69]

5. 1. 장점

원자층 증착(ALD)은 원자 수준에서 박막 두께를 매우 정밀하게 제어할 수 있는 방법을 제공한다.[71][24] 이를 통해 서로 다른 재료로 이루어진 다층 구조도 비교적 쉽게 증착할 수 있다. ALD 공정은 각 전구체가 기판 표면과 자기 제어적 반응을 하기 때문에, 기판의 크기나 복잡한 구조에 상관없이 매우 균일하고 고정밀도의 박막을 형성할 수 있다. 또한, 매우 얇으면서도 치밀한 박막을 만드는 것이 가능하다.ALD는 접근성이 뛰어나 분말 형태나 복잡한 3차원 구조를 가진 물체의 표면에도 균일하게 박막을 코팅하는 데 유리하다.

일반적으로 ALD 공정은 비교적 낮은 온도에서 진행된다.[71][24] 이는 열에 약한 유기물이나 생체 샘플과 같이 부드럽거나 취약한 기판을 사용할 때 장점이 된다. 또한, 열적으로 불안정한 전구체 재료를 사용하는 경우에도 유리하다.

이러한 정밀성, 균일성, 그리고 낮은 공정 온도 등의 장점 덕분에 ALD는 마이크로일렉트로닉스 및 나노기술 분야에서 작고 효율적인 반도체 소자를 생산하는 데 매우 유용하다.[71][24]

5. 2. 한계

원자층 증착(ALD) 공정의 주요 한계점은 다음과 같다.1. 느린 증착 속도ALD 공정의 가장 큰 단점은 증착 속도가 매우 느리다는 점이다. 예를 들어, Al₂O₃는 한 사이클당 약 0.11nm 정도만 증착되며,[2] 이는 시간당 평균 100nm~300nm 수준에 해당한다.[69] 따라서 마이크로미터(μm) 단위의 두꺼운 박막을 형성해야 하는 경우에는 증착 시간이 매우 길어져 비효율적이다. 다만, 마이크로일렉트로닉스나 나노기술 분야에서는 일반적으로 매우 얇은 박막이 필요하므로 큰 문제가 되지 않을 수도 있다.

느린 증착 속도 문제는 기판을 이동시키면서 전구체 기체를 분리하여 연속적으로 공급하는 공간 원자층 증착(Spatial ALD) 기술을 통해 일부 개선될 수 있다. 이 방식을 사용하면 분당 60nm 수준의 증착 속도를 달성할 수 있다.[69]

2. 재료의 제한

- 전구체: 사용할 수 있는 전구체(Precursor)의 종류가 제한적이다. 전구체는 휘발성이 있어야 하지만, 동시에 공기나 산소에 민감하게 반응하여 쉽게 분해되지 않아야 한다.[69] 이러한 조건을 만족하는 물질이 많지 않다.

- 기판: 증착 과정 중 가해지는 열을 견딜 수 있어야 하므로, 열에 민감한 기판(예: 일부 생물학적 기판)은 사용하기 어렵다.[69] 또한 기판의 높은 순도가 요구되며, 일부 특수 기판(예: 마이크로전자 산업용 다성분 산화물, 특정 금속)은 구하기 어렵고 가격이 비싸다.[70][69]

3. 높은 비용

- 장비 비용: ALD 장비는 일반적으로 고가이며, 장비의 사양과 성능에 따라 가격은 20만달러에서 80만달러에 이른다.[70]

- 공정 개발 비용: 원하는 박막 품질을 얻기 위한 최적의 공정 조건을 찾는 데 많은 시간과 노력이 소요된다. 여러 차례의 시험 증착이 필요할 수 있으며, 이는 공정 개발 비용 증가로 이어진다.[69]

- 운영 비용: 사용되는 기판의 종류와 순도, 공정 온도 및 시간 등 다양한 요인에 따라 운영 비용이 달라진다.[70] 특히 고순도 기판이나 특수 조건이 필요한 기판은 비용을 상승시킨다.

4. 기타 문제

6. ALD 관련 파생 기술

원자층 증착(ALD)은 전구체와 반응물을 공급하는 방식에 따라 시간 분리 방식과 공간 분리 방식으로 나눌 수 있다.

일반적인 ALD 공정은 시간 분리 원자층 증착(Temporal ALD영어) 방식을 사용한다. 이 방식에서는 각기 다른 전구체와 반응물을 시간 간격을 두고 번갈아 반응기에 주입하며, 각 단계 사이에 반응하지 않은 물질이나 부산물을 제거하기 위한 퍼지(purge) 단계를 둔다.[5] 이를 통해 기판 표면에서 자기 제한적인 반응이 순차적으로 일어나 박막이 한 층씩 성장하게 된다.

반면, 공간 분리 원자층 증착(Spatial ALD영어, s-ALD)은 전구체와 반응물을 공간적으로 분리하는 방식이다. 대기압 하에서 작동하는 공간 분리 ALD의 경우, 전구체와 반응물이 서로 다른 위치에서 지속적으로 공급되며, 이들 사이에 질소와 같은 비활성 기체를 이용한 기체 커튼(gas curtain)을 형성하여 기체 상태에서의 직접적인 반응을 막는다.[5] 기판이 이 분리된 공간들을 연속적으로 지나가면서 표면에서 자기 제한 반응이 일어나 박막이 증착된다.

공간 분리 방식은 전구체와 반응물을 연속적으로 공급하고 기판을 이동시키므로, 시간 분리 방식의 퍼지 단계가 필요 없어 증착 속도를 획기적으로 높일 수 있다. 예를 들어, Al₂O₃ 증착의 경우, 시간 분리 ALD의 증착 속도가 시간당 100~300 nm 수준인 반면, 공간 분리 ALD는 분당 60 nm까지 속도를 높일 수 있다.[5] 이러한 빠른 속도와 인라인(in-line) 공정 특성 덕분에 공간 분리 ALD는 대량 생산 라인이나 롤투롤(roll-to-roll) 생산에 적합하다.[5]

주요 응용 분야로는 유연 디스플레이나 OLED의 수분 및 산소 투과를 막는 박막 봉지층, 실리콘 태양 전지의 표면 패시베이션층, 배터리 전극 코팅 등이 있다.[5] 공간 분리 ALD를 통해 증착 가능한 재료는 Al₂O₃, ZnO(Al 또는 Ga 도핑 포함), SiO₂, In₂O₃, InZnO, LIPON, Zn(O,S), SnOₓ, TiOₓ와 같은 다양한 무기 금속 산화물뿐만 아니라, Pt, Ir, Ru과 같은 귀금속도 포함된다.[5] 또한, 플라즈마나 오존을 이용하여 반응성을 높이는 플라즈마 강화(plasma-enhanced) 또는 오존 강화 공간 분리 ALD 기술도 개발되어, 공정 온도를 낮추는 데 활용되고 있다.[5]

ALD 공정에서는 일반적으로 높은 순도의 기판이 요구되며, 이는 공정 비용에 영향을 미칠 수 있다.[69]

6. 1. 분자층 증착 (MLD)

분자층 증착(MLD, Molecular Layer Deposition영어)은 원자층 증착(ALD)과 유사한 기술로, 유기 전구체인 유기물 폴리머를 사용하여 고분자 박막을 형성하는 방법이다. 이 기술은 ALD 공정을 기반으로 하며, 초격자 제작 등 다양한 분야에 활용된다. 또한, ALD와 MLD 기술을 결합하면 매우 균일하고 순수한 하이브리드 박막을 제작할 수 있다.6. 2. 순차 침투 합성 (SIS)

순차 침투 합성(Sequential Infiltration Synthesis, SIS)은 원자층 증착(ALD)과 관련된 기술 중 하나이다. 이 기술은 교대로 전구체 증기를 노출시켜 고분자 내부에 침투시키고 이를 변형시키는 방식으로 작동한다. SIS는 기상 침투(Vapor Phase Infiltration, VPI) 또는 순차 기상 침투(Sequential Vapor Infiltration, SVI)라고도 불린다.2010년 아르곤 국립연구소의 연구원들이 순차 침투 합성을 처음으로 보고하였으며, 이는 원자층 증착(ALD) 관련 기술군에 포함되었다. 기상 침투법(VPI)이라고도 하는 이 방법은 유기 고분자나 섬유의 내부까지 전구체를 침투시켜 유무기 하이브리드 재료를 만드는 데 사용된다.

7. 품질 관리

원자층 증착(ALD) 공정의 품질은 공정이 원활하게 진행되고 표면에 균일한 박막이 형성되는지 확인하기 위해 다양한 분석 기법을 사용하여 평가한다.

대표적인 방법으로는 단면 주사전자현미경(SEM)이나 투과전자현미경(TEM)을 이용한 이미징 기법이 있다. 고배율 이미지를 통해 마이크로미터에서 나노미터 수준까지 박막의 상태를 직접 관찰하여 품질을 평가할 수 있다.

X선 반사율 측정법(XRR)은 박막의 두께, 밀도, 표면 거칠기 등 물리적 특성을 정밀하게 측정하는 데 사용된다.[67] 분광 엘립소메트리(SE)는 빛을 이용하여 박막의 광학적 특성을 분석하는 방법이다. ALD 공정 중 각 층이 증착될 때마다 SE 측정을 수행하면 박막의 성장 속도와 재료의 특성 변화를 파악할 수 있다.[68]

특히, ALD 공정 중에 실시간으로 분광 엘립소메트리 측정을 수행하는 ''in situ'' 방식은 박막 성장 속도를 더욱 정밀하게 제어할 수 있게 해준다. 이는 공정이 끝난 후에 박막을 평가하는 SEM, TEM, XRR 방식과 달리 공정 중에 직접 품질 관리가 가능하다는 장점이 있다.

이 외에도 러더퍼드 후방 산란 분광법(RBS), X선 광전자 분광법(XPS), 오거 전자 분광법(AES), 4점 탐침법 등의 분석 기법들이 ALD 박막의 품질 관리 및 특성 분석에 활용된다.[68]

참조

[1]

논문

Conformality in atomic layer deposition: Current status overview of analysis and modelling

AIP Publishing

2019-04-04

[2]

논문

Surface chemistry of atomic layer deposition: A case study for the trimethylaluminum/water process

2005-06-15

[3]

웹사이트

ALD Database

https://atomiclimits[...]

Eindhoven University of Technology

[4]

논문

Crystallinity of inorganic films grown by atomic layer deposition: Overview and general trends

2013-01-14

[5]

논문

Surface chemistry of atomic layer deposition: A case study for the trimethylaluminum/water process

2005-06-15

[6]

논문

Status and prospects of plasma-assisted atomic layer deposition

https://research.tue[...]

2019-05-01

[7]

논문

Synthesis of Doped, Ternary, and Quaternary Materials by Atomic Layer Deposition: A Review

2018-12-10

[8]

논문

From V. B. Aleskovskii's "Framework" Hypothesis to the Method of Molecular Layering/Atomic Layer Deposition

2015

[9]

논문

[10]

논문

A Short History of Atomic Layer Deposition: Tuomo Suntola's Atomic Layer Epitaxy

https://zenodo.org/r[...]

2014

[11]

특허

Method for producing compound thin films

[12]

특허

Apparatus for performing growth of compound thin films

[13]

보도자료

2018 Millennium Technology Prize for Tuomo Suntola – Finnish physicist's innovation enables manufacture and development of information technology products

https://taf.fi/2018/[...]

Technology Academy Finland

2018-05-22

[14]

논문

Review Article: Recommended reading list of early publications on atomic layer deposition—Outcome of the "Virtual Project on the History of ALD"

2016

[15]

논문

Learnings from an Open Science Effort: Virtual Project on the History of ALD

https://ecsarxiv.org[...]

[16]

논문

History of atomic layer deposition and its relationship with the American VacuumSociety

https://research.tue[...]

2013

[17]

웹사이트

IEEE Andrew S. Grove Award Recipients

https://www.ieee.org[...]

Institute of Electrical and Electronics Engineers

[18]

웹사이트

Atomic layer doping apparatus and method

https://patents.goog[...]

2001-08-22

[19]

서적

2007 IEEE International Electron Devices Meeting

[20]

웹사이트

Virtual project on the history of ALD

http://www.vph-ald.c[...]

[21]

Youtube

How Atomic Layer Deposition Works

https://www.youtube.[...]

2011

[22]

서적

Physics and Chemistry of Interfaces

John Wiley & Sons

[23]

웹사이트

2.3 Adsorption Kinetics – The Rate of Adsorption

http://www.chem.qmul[...]

[24]

논문

Atomic Layer Deposition: An Overview

[25]

Doctoral thesis

Atomlagenabscheidung unterstützt Nanostrukturelle Transformationen

https://freidok.uni-[...]

University of Freiburg

[26]

논문

Precursors and chemistry for the atomic layer deposition of metallic first row transition metal films

2013-12-01

[27]

서적

CRC handbook of chemistry and physics : a ready-reference book of chemical and physical data

CRC Press

2011

[28]

논문

Trends in Copper Precursor Development for CVD and ALD Applications

2015

[29]

논문

Low Temperature Growth of High Purity, Low Resistivity Copper Films by Atomic Layer Deposition

2011-10-25

[30]

논문

Low-Temperature Atomic Layer Deposition of High Purity, Smooth, Low Resistivity Copper Films by Using Amidinate Precursor and Hydrogen Plasma

2015-09-08

[31]

논문

Atomic layer deposition of tungsten using sequential surface chemistry with a sacrificial stripping reaction

2000-02-01

[32]

논문

Molybdenum Atomic Layer Deposition Using MoF 6 and Si 2 H 6 as the Reactants

2011-04-12

[33]

논문

Gas phase reaction products during tungsten atomic layer deposition using WF[sub 6] and Si[sub 2]H[sub 6]

2004

[34]

논문

Quartz crystal microbalance study of tungsten atomic layer deposition using WF6 and Si2H6

2005-09-01

[35]

논문

Kinetics of the WF6 and Si2H6 surface reactions during tungsten atomic layer deposition

2001-05-01

[36]

논문

Volatile and Thermally Stable Mid to Late Transition Metal Complexes Containing α-Imino Alkoxide Ligands, a New Strongly Reducing Coreagent, and Thermal Atomic Layer Deposition of Ni, Co, Fe, and Cr Metal Films

2013-08-28

[37]

논문

Thermal Atomic Layer Deposition of Titanium Films Using Titanium Tetrachloride and 2-Methyl-1,4-bis(trimethylsilyl)-2,5-cyclohexadiene or 1,4-Bis(trimethylsilyl)-1,4-dihydropyrazine

2015-07-28

[38]

논문

Thermal atomic layer deposition of Sn metal using SnCl 4 and a vapor phase silyl dihydropyrazine reducing agent

2018-11-01

[39]

논문

Atomic Layer Deposition of Aluminum Metal Films Using a Thermally Stable Aluminum Hydride Reducing Agent

2018-03-27

[40]

논문

Surface Modification of Au/TiO2 Catalysts by SiO2 via Atomic Layer Deposition

[41]

논문

High-rate atomic layer deposition of Al{{sub|2}}O{{sub|3}} for the surface passivation of Si solar cells

[42]

논문

Atomic layer deposition of metal and nitride thin films: Current research efforts and applications for semiconductor device processing

[43]

논문

Room-Temperature Atomic Layer Deposition of Platinum

2013

[44]

웹사이트

Fundamental Vacuum Beam Studies of Radical Enhanced Atomic Layer Chemical Vapor Deposition (REAL-CVD) of TiN

https://web.archive.[...]

NCCAVS

[45]

논문

Energy-enhanced atomic layer deposition for more process and precursor versatility

2013-12-01

[46]

논문

Atomic Layer Deposition of Silicon Nitride from Bis(''tert''-butylamino)silane and N2 Plasma

https://pure.tue.nl/[...]

2015-09-09

[47]

논문

Synthesis and in situ characterization of low-resistivity TaNx films by remote plasma atomic layer deposition

https://research.tue[...]

2007-10-15

[48]

논문

Diffusion Barrier Deposition on a Copper Surface by Atomic Layer Deposition

[49]

논문

ALD-grown seed layers for electrochemical copper deposition integrated with different diffusion barrier systems

http://www.qucosa.de[...]

[50]

웹사이트

Magnetic Recording Theory

https://web.archive.[...]

stanford.edu

[51]

웹사이트

Industrial Applications of Atomic Layer Deposition (ALD)

http://www.miics.net[...]

10th MIICS Conference

[52]

서적

Memory, 1997: Complete Coverage of DRAM, Sram, EPROM, and Flash Memory IC's

Integrated Circuit Engineering Corp.

[53]

논문

Atomic Layer Deposition for Advanced DRAM Applications

http://www.future-fa[...]

[54]

논문

Atomic layer deposition for photovoltaics: applications and prospects for solar cell manufacturing

https://iopscience.i[...]

2012-07-11

[55]

논문

Surface passivation of high-efficiency silicon solar cells by atomic-layer-deposited Al 2 O 3

https://onlinelibrar[...]

2008-09-01

[56]

논문

Atomic layer deposition for efficient and stable perovskite solar cells

http://xlink.rsc.org[...]

2019

[57]

논문

Experiment and Theory of an Active Optical Filter

https://ieeexplore.i[...]

[58]

논문

Biocompatible Polymer Materials: Role of Protein-surface Interactions

[59]

논문

TiO{{sub|2}} ALD nanolayer as evanescent waveguide for biomedical sensor applications

[60]

논문

Recent Advances in Flexible Sensors for Wearable and Implantable Devices

[61]

논문

Nanoporous Materials for Biomedical Devices

[62]

논문

Plasma-Assisted ALD of an Al2O3 Permeation Barrier Layer on Plastic

2012-02-01

[63]

논문

Ultra thin film encapsulation of OLED on plastic substrate

2004-01-01

[64]

논문

Ultra Thin Film Encapsulation of OLED on Plastic Substrate

2005-10-14

[65]

논문

Atomic layer deposited aluminum oxide mitigates outgassing from fused filament fabrication–based 3-D printed components

https://aaltodoc.aal[...]

2020-03-01

[66]

논문

Barrier properties of plastic films coated with an Al2O3 layer by roll-to-toll atomic layer deposition

2014-01-01

[67]

논문

X-ray thin-film measurement techniques

https://www.rigaku.c[...]

[68]

논문

In situ spectroscopic ellipsometry as a versatile tool for studying atomic layer deposition

[69]

논문

Atomic layer deposition chemistry: Recent developments and future challenges

http://files.instrum[...]

[70]

웹사이트

Molecular Beam Epitaxy & Atomic Layer Deposition Systems

http://www.svta.com/

SVT Associates

[71]

논문

New Development of Atomic Layer Deposition: Processes, Methods, and Applications

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com