반도체 제조

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

반도체 제조는 전자 장치 제작에 사용되는 복잡한 공정으로, 1950년대에 시작되어 기술 발전을 거듭하며 세계적인 산업으로 성장했다. 이 공정은 웨이퍼 위에 회로를 형성하는 전공정(FEOL), 트랜지스터를 배선하는 후공정(BEOL), 그리고 패키징 및 테스트 단계를 포함한다. 주요 공정 단계는 증착, 제거, 패터닝, 전기적 특성 변경으로 나뉘며, 리소그래피, 이온 주입, 에칭, 화학 기상 증착 등이 핵심 기술로 사용된다. 웨이퍼는 순수한 실리콘으로 만들어지며, 클린룸 환경에서 오염 및 결함을 방지하기 위한 엄격한 관리가 이루어진다. 수율은 웨이퍼당 작동하는 칩의 비율을 나타내며, 공정 변동, 오염 물질, 결함 등이 수율에 영향을 미친다. 완성된 칩은 테스트를 거쳐 패키징되며, 유해 물질 사용에 대한 안전 관리도 중요하다.

더 읽어볼만한 페이지

- 반도체 제조 - 웨이퍼

웨이퍼는 단결정 실리콘 잉곳을 가공하여 만든 얇고 둥근 반도체 재료 조각으로, 반도체 산업의 핵심 재료이며, 다양한 결정 성장 방법과 가공 과정을 거쳐 생산되고, 현재는 300mm 웨이퍼가 주류이지만 450mm 웨이퍼 개발 경쟁이 진행 중이며, 실리콘 외 다양한 재료가 사용되고, 일본 기업들이 시장을 주도하고 한국 기업들도 경쟁력을 확보하고 있다. - 반도체 제조 - 이온 주입

이온 주입은 원하는 원소를 이온화하여 고체 표면에 주입하는 기술로, 반도체 도핑, 금속 표면 처리 등 다양한 분야에 활용되며, 결정학적 손상, 스퍼터링, 안전 문제 등의 문제점을 야기한다. - MOSFET - CMOS

CMOS는 상보적 금속 산화막 반도체의 약자로, 저전력 소비를 특징으로 하며, P형과 N형 MOSFET을 결합하여 논리 게이트를 구현하는 디지털 회로 설계 방식 및 공정 계열이다. - MOSFET - 전자 이동도

전자 이동도는 전기장 내에서 전자의 평균 이동 속도를 나타내는 물리량으로, 재료의 불순물 농도와 온도에 의존하며, 다양한 산란 메커니즘과 측정 방법을 통해 연구되고 반도체 소자 성능에 중요한 영향을 미친다.

| 반도체 제조 | |

|---|---|

| 개요 | |

| 설명 | 집적 회로를 만드는 데 사용되는 제조 공정 |

| 기술 | |

| 웨이퍼 | 실리콘 웨이퍼 |

| 관련 항목 | MOSFET 스케일링 (공정 노드) 하프 노드 집적도 CMOS 소자 (멀티 게이트) 무어의 법칙 트랜지스터 개수 반도체 산업 나노 전자 공학 |

2. 역사

반도체 제조 기술은 20세기 중반 트랜지스터의 발명 이후 눈부신 발전을 거듭해왔다. 초기 벨 연구소에서의 실리콘 표면 처리 기술 발견[24][25]과 페어차일드 반도체에서 개발된 평면 공정[31][32]은 현대 집적 회로(IC) 생산의 기반을 마련했다. 이후 MOSFET[33]과 CMOS[34][35] 기술의 개발 및 상용화는 디지털 시대의 개막을 이끌었다.

반도체 산업은 미국에서 시작되어 아시아, 유럽 등 전 세계로 확산되었으며, 생산 효율성을 높이기 위해 웨이퍼 크기는 지속적으로 증가해왔다.[40][41] 제조 공정 역시 초기 수동 방식에서 벗어나 자동화된 장비와 클러스터 도구의 도입[48], 화학 기상 증착(CVD)[49] 및 단일 웨이퍼 처리 방식[65][66] 등으로 발전하며 정밀도와 생산성을 높였다.

21세기에 들어서는 300mm 웨이퍼가 표준으로 자리 잡았고,[51][52] 무어의 법칙을 따라 미세 공정 경쟁이 더욱 치열해졌다. 10 nm 공정 이하의 미세화가 진행되면서 기존 평면 트랜지스터의 한계를 극복하기 위해 FinFET[85]과 같은 새로운 구조가 도입되었으며, 현재는 GAAFET 등 차세대 기술 개발이 활발히 이루어지고 있다.[91] 이러한 기술 경쟁 속에서 삼성전자, TSMC, 인텔 등 소수의 글로벌 기업들이 시장을 주도하고 있으며,[69] 한국 기업들은 메모리 반도체뿐만 아니라 파운드리 분야에서도 선도적인 위치를 확보하며 기술 혁신을 이끌고 있다.

한편, 공정 세대를 나타내는 '노드' 명칭은 실제 물리적 크기보다는 마케팅적인 의미가 강해지기도 했다.[76][77][78] 최근에는 코로나19 팬데믹 등으로 인한 전 세계적인 반도체 부족 사태[105]를 겪으며 반도체가 국가 경제와 안보에 미치는 영향력이 더욱 커지고 있으며,[107][108][109] 각국 정부의 반도체 산업 육성 및 공급망 확보 노력이 강화되는 추세이다.

2. 1. 20세기

1955년, 벨 연구소의 칼 프로쉬(Carl Frosch)와 링컨 데릭(Lincoln Derick)은 실리콘 웨이퍼 위에 이산화 규소(SiO₂) 층을 성장시키는 과정에서 우연히 표면 부동태화(surface passivation) 효과를 발견했다.[24][25] 이 발견은 반도체 기술 발전에 중요한 계기가 되었다. 1957년, 이들은 마스킹 및 사전 증착 기법을 활용하여 드레인과 소스가 동일 평면에 위치한 최초의 평면형 전계 효과 트랜지스터, 즉 실리콘 이산화물 트랜지스터를 제작하는 데 성공했다.[26] 벨 연구소는 이 연구의 중요성을 인식하고 공식 발표 전에 내부적으로 연구 결과를 공유했다. 쇼클리 반도체 연구소의 윌리엄 쇼클리 역시 1956년 12월, 장 호어니(Jean Hoerni)를 포함한 연구진에게 해당 논문의 사전 인쇄본을 배포했다.[27][28][29][30] 이후 장 호어니는 페어차일드 반도체로 옮겨 1959년에 현대 반도체 공정의 핵심 기술인 평면 공정(planar process)을 발명했다.[31][32]

한편, 1948년 존 바딘은 반전층(inversion layer)을 이용한 절연 게이트 트랜지스터(IGFET)에 대한 특허를 출원했는데, 이는 오늘날 MOSFET 기술의 이론적 기초를 마련한 것으로 평가받는다.[33] 이를 바탕으로 1963년 페어차일드 반도체의 사 자이탕(Chih-Tang Sah)과 프랭크 완라스(Frank Wanlass)는 기존 MOSFET 기술을 개선한 CMOS(Complementary Metal-Oxide-Semiconductor) 기술을 개발했다.[34][35] CMOS 기술은 낮은 소비 전력 특성 덕분에 빠르게 주목받았고, 1960년대 후반 RCA에 의해 상용화되었다.[34] RCA는 1968년 4000 시리즈 집적 회로에 CMOS 기술을 처음 적용했으며, 초기 20 μm 공정에서 시작하여 점차 10 μm 공정으로 미세화했다.[36] 이 시기 많은 초기 반도체 기업들은 이온 주입기(ion implanter)와 같은 제조 장비를 자체적으로 개발하고 제작하기도 했다.[37]

같은 시기, 새로운 소재와 공정 기술 연구도 활발히 진행되었다. 1963년 노스 아메리칸 항공(현 보잉) 오토네틱스 부서의 해럴드 M. 마나세비트(Harold M. Manasevit)는 사파이어 기판 위에 실리콘을 에피택셜 성장시키는 기술(실리콘 온 사파이어)을 처음으로 기록했으며,[38] 1964년 동료 윌리엄 심슨(William Simpson)과 함께 연구 결과를 발표했다.[38] 1965년에는 RCA 연구소의 C.W. 뮬러(Mueller)와 P.H. 로빈슨(Robinson)이 이 실리콘 온 사파이어(Silicon-on-Sapphire, SOS) 공정을 이용하여 MOSFET을 제작하는 데 성공했다.[39]

1960년대 미국의 텍사스와 캘리포니아에서 시작된 반도체 장치 제조 산업은 점차 아시아, 유럽, 중동 등 전 세계로 확산되었다. 산업의 성장과 함께 생산 효율성을 높이기 위한 웨이퍼 크기 증대 노력이 이어졌다.

| 연도 | 웨이퍼 직경 (mm) | 웨이퍼 직경 (inch) |

|---|---|---|

| 1960 | 25mm | 1인치 |

| 1969 | 50mm | 2인치 |

| 1976 | 100mm | 4인치 |

| 1981 | 125mm | 5인치 |

| 1983 | 150mm | 6인치 |

| 1992 | 200mm | 8인치 |

웨이퍼 크기가 커짐에 따라 취급 방식도 변화했다. 초기 50mm 웨이퍼 시대에는 핀셋으로 웨이퍼를 하나씩 수동으로 다루었으나, 오염 문제를 줄이기 위해 진공 완드(vacuum wand)로 대체되었다.[42] 여러 웨이퍼를 한 번에 담아 공정 단계 간 이동을 용이하게 하는 웨이퍼 캐리어(카세트)가 개발되었고, 습식 식각 및 세척 공정에서는 웨이퍼가 담긴 전체 카세트를 탱크에 담글 수 있는 내산성 캐리어가 사용되었다. 하지만 웨이퍼 크기가 100mm로 커지면서 카세트 전체를 균일하게 처리하기 어려워졌고, 품질 관리의 어려움이 발생했다. 150mm 웨이퍼 시대에는 카세트를 담그는 방식 대신 운반 및 보관 용도로만 사용하게 되었고, 로봇을 이용한 웨이퍼 핸들링이 보편화되었다. 200mm 웨이퍼는 카세트의 무게 증가로 인해 수동 취급이 더욱 위험해졌다.[43]

1970년대에는 많은 반도체 회사들이 기존의 바이폴라 접합 트랜지스터(BJT) 기술에서 MOSFET 기술로 전환하는 경향을 보였다. 이 시기부터 반도체 제조 장비의 가격이 급격히 상승하기 시작했으며, 1978년경에는 이미 고가의 장비로 인식되었다.[44]

1980년대에는 자동화 및 공정 기술의 발전이 두드러졌다. 1984년 KLA 코퍼레이션은 최초의 자동 레티클 및 포토마스크 검사 도구를 개발했고,[45] 1985년에는 기존의 수동 현미경 검사를 대체하는 자동 실리콘 웨이퍼 검사 도구를 선보였다.[46] 같은 해, SGS(현 ST마이크로일렉트로닉스)는 바이폴라, CMOS, DMOS 소자를 하나의 칩에 집적할 수 있는 BCDMOS 공정을 발명했다.[47] 또한 어플라이드 머티어리얼즈는 여러 공정 챔버를 하나로 묶어 웨이퍼 처리 효율을 높인 멀티 챔버(클러스터) 장비인 Precision 5000을 개발하며 웨이퍼 처리 방식에 혁신을 가져왔다.[48] 재료 증착 방식에서도 변화가 있었는데, 1980년대까지 주로 사용되던 물리적 기상 증착(PVD) 방식 외에 화학 기상 증착(CVD) 기술이 부상했다.[49] 진공 장비에서는 웨이퍼 오염 가능성이 있는 오일을 사용하는 확산 펌프 대신 터보분자 펌프가 점차 도입되었다.[50]

1990년에는 200mm 직경 웨이퍼가 처음 도입되어 2000년 300mm 웨이퍼가 등장하기 전까지 업계 표준으로 자리 잡았다.[51][52] 웨이퍼 크기 전환기에는 이전 세대와 새로운 세대의 웨이퍼를 모두 처리할 수 있는 브리지 도구(bridge tool)가 활용되었다.[53][54][55] 웨이퍼 크기 증가는 웨이퍼당 생산할 수 있는 칩의 수를 늘려 증가하는 반도체 수요에 대응하기 위한 산업계의 지속적인 노력이었다.[56] 1990년대 후반부터는 세척,[59] 이온 주입,[60][61] 식각,[62] 어닐링,[63] 산화[64] 등 일부 공정에서 기존의 배치(batch) 처리 방식 대신 웨이퍼를 하나씩 처리하는 단일 웨이퍼 처리(single-wafer processing) 방식이 채택되기 시작했다. 이는 공정 결과의 재현성을 향상시키기 위한 목적이었으며,[65][66] MEMS 제조 분야에서도 유사한 경향이 나타났다.[67] 1998년 어플라이드 머티어리얼즈는 웨이퍼 처리 챔버를 쌍으로 묶어 공유된 진공 및 공급 라인을 사용하면서도 각 챔버를 격리하여 품질 저하 없이 생산성을 높인 클러스터 도구 'Producer'를 출시하며 기술 발전을 이끌었다.[68][53]

2. 2. 21세기

오늘날 반도체 산업은 전 세계적인 규모로 운영되며, 주요 제조업체들은 세계 곳곳에 생산 시설을 두고 있다. 세계 최대 반도체 제조업체인 삼성전자는 한국과 미국에, 2위인 인텔은 미국을 비롯해 유럽과 아시아에 시설을 운영 중이다. 세계 최대의 순수 파운드리 기업인 TSMC는 대만, 중국, 싱가포르, 미국 등지에 생산 기지를 갖추고 있다. 퀄컴이나 브로드컴과 같은 주요 팹리스 기업들은 TSMC와 같은 파운드리에 생산을 위탁한다.[69] 반도체 소자의 사용이 늘면서 내구성이 중요해졌고, 특히 10 nm 노드 이후부터는 장치의 수명을 고려한 설계가 중요해졌다.[70][71]21세기 초반, 절연체 위의 실리콘 (SOI) 기술이 AMD에 의해 130 nm부터 32 nm 공정까지 다양한 프로세서에 적용되었다.[72] 2001년에는 웨이퍼 크기가 200mm에서 300mm로 전환되기 시작했으며, 당시 약 18개 회사가 최첨단 130 nm 공정 기술을 보유하고 있었다.[73][74] 2006년에는 450mm 웨이퍼가 2012년에, 675mm 웨이퍼가 2021년에 도입될 것이라는 예측도 있었으나[75], 2024년 현재까지 450mm 웨이퍼는 상용화되지 않았다.

2009년부터 공정 '노드' 명칭은 실제 게이트 길이나 피치와 직접적인 관련 없이, 새로운 기술 세대를 나타내는 마케팅 용어로 사용되기 시작했다.[76][77][78] 예를 들어, 글로벌파운드리의 7 nm 공정은 기술적으로 인텔의 10 nm 공정과 유사했으며,[79] TSMC와 삼성의 10 nm 공정 역시 트랜지스터 밀도 면에서 인텔의 14 nm 공정과 큰 차이가 없었다(예: 삼성 10 nm 공정의 핀 피치는 42nm로 인텔 14 nm 공정과 동일).[80][81] 이에 인텔은 자사의 10 nm 공정을 'Intel 7' 등으로 리브랜딩하기도 했다.[82] 트랜지스터 크기가 줄어들면서 자체 발열[83]이나 전자이동[84]과 같은 새로운 물리적 현상이 설계에 영향을 미치기 시작했다.

2011년, 인텔은 핀 필드 효과 트랜지스터 (FinFET) 기술을 선보였다. FinFET은 게이트가 채널을 3면에서 감싸는 구조로, 기존 평면 트랜지스터의 단채널 효과 문제를 해결하고 22 nm 노드에서 에너지 효율과 성능을 크게 향상시켰다.[85][86][87][88][89] 한편, SuVolta라는 스타트업은 Deeply Depleted Channel (DDC) 기술을 개발하여 65 nm 노드에서 FinFET에 도전하기도 했다.[90]

2018년을 전후하여 FinFET을 대체할 차세대 트랜지스터 구조 연구가 활발해졌다. 대부분 GAAFET (Gate-All-Around FET) 개념에 기반하며, 수평/수직 나노와이어, 나노시트 (삼성의 MBCFET, 인텔의 나노리본), 수직 FET (VFET), 상보형 FET (CFET), III-V족 화합물 반도체 기반 FinFET 등 다양한 형태가 제안되었다.[91][92][93][94][95][96][97][98][99] FD-SOI 역시 FinFET의 저비용 대안으로 고려되었다.[100]

2019년 기준으로 14 nm 및 10 nm 칩은 인텔, UMC, TSMC, 삼성, 마이크론, SK하이닉스, 도시바 메모리, 글로벌파운드리 등에서 대량 생산되었다. 7 nm 공정 칩은 TSMC와 삼성이 주도했으나, 이들의 7 nm는 인텔의 10 nm 공정과 유사한 수준으로 평가받는다. 5 nm 공정은 2018년 삼성이 생산을 시작했으며,[101] 2019년 당시 최고 트랜지스터 밀도는 TSMC의 5 nm N5 노드(mm²당 1억 7,130만 개)였다.[102][103] 삼성과 TSMC는 3 nm 노드 생산 계획도 발표했다. 반면, 글로벌파운드리는 재정적 부담을 이유로 12 nm 이하 미세 공정 개발을 중단했다.[104]

2020년부터 2023년까지 코로나19 팬데믹 등의 영향으로 전 세계적인 반도체 부족 사태가 발생했다.[105] 이 사태는 반도체가 국가 경제와 안보에 필수적임을 부각시켰고,[107][108][109] 각국 정부는 자국 내 반도체 생산 시설 유치를 위해 경쟁적으로 보조금을 지급했다. 위조 칩 문제도 심화되었다.[106] 또한, 미국과 중국 간의 기술 패권 경쟁이 심화되면서, 미국 정부는 TSMC에 화웨이로의 반도체 공급 중단을 요구하는 등[110][111][112] 지정학적 갈등이 반도체 산업에 직접적인 영향을 미치기 시작했다. 이러한 상황 속에서 NMOS와 PMOS 트랜지스터를 수직으로 쌓는 형태의 차세대 기술인 CFET 트랜지스터 연구도 계속되었다.[113]

3. 제조 공정

현대 전자 장치 제작 과정에는 다양한 공정 기술이 여러 차례 사용된다. 특정 공정 순서가 정해져 있거나 모든 기술이 반드시 사용되는 것은 아니며, 실제 공정 순서와 적용 기술은 파운드리의 공정 제공 방식이나 종합 반도체 제조사(IDM)의 자체 제품 설계에 따라 달라진다. 모든 반도체 장치가 모든 기술 단계를 거치는 것은 아니다. 이러한 공정을 수행하는 장비는 소수의 전문 기업에서 제조하며, 모든 장비는 반도체 제조 공장이 가동되기 전에 엄격한 테스트를 거쳐야 한다.[114] 제조 공정은 집적 회로 설계가 완료된 후에 시작된다. 반도체 공장은 연중무휴 24시간 가동되며,[115] 많은 공정, 특히 세척 단계에서 대량의 물을 사용한다.[116]

반도체 소자 제조 공정은 크게 네 가지 일반적인 범주로 나눌 수 있다.

- '''증착 (Deposition)''': 웨이퍼 위에 물질을 성장시키거나 코팅하는 모든 공정을 의미한다. 물리 기상 증착(PVD), 화학 기상 증착(CVD), 전기 도금(ECD), 분자선 에피택시(MBE), 원자층 증착(ALD) 등이 있으며, 산화막 형성이나 열 산화도 넓은 의미에서 증착에 포함될 수 있다.

- '''제거 (Removal)''': 웨이퍼에서 물질을 제거하는 공정이다. 식각 공정(습식 식각 또는 건식 식각)과 화학적 기계적 연마(CMP)가 대표적이다.

- '''패터닝 (Patterning)''': 증착된 물질의 모양을 만들거나 변경하는 과정으로, 주로 포토리소그래피 기술이 사용된다. 웨이퍼에 포토레지스트를 코팅하고, 노광 장비(스텝퍼 또는 스캐너)를 이용해 포토마스크의 패턴을 빛으로 투사한다. 노광된 영역(또는 노광되지 않은 영역)의 포토레지스트를 현상액으로 제거한 후, 남은 포토레지스트를 마스크 삼아 식각 등의 후속 공정을 진행한다. 이후 남은 포토레지스트는 플라즈마 애싱이나 화학 용매를 이용해 제거한다.[142] 과거에는 습식 식각이 널리 쓰였으나,[143][144] 미세 공정이 발전하면서 패턴 아래까지 파고드는 언더컷 현상[147][148][149] 때문에 10 마이크론에서 3 마이크론 노드부터는 건식 식각(플라즈마 에칭)이 주력 기술이 되었다.[145][146][150]

- '''전기적 특성 변경 (Modification of Electrical Properties)''': 주로 트랜지스터의 소스, 드레인 영역과 폴리실리콘 게이트에 도펀트를 주입하여 전기적 특성을 조절하는 공정이다. 초기에는 고온의 로(furnace)를 이용한 열 확산 방식이 사용되었으나,[151][152][153] 1970년대 이후로는 더 정밀하고 재현성이 높은 이온 주입 방식이 주류가 되었다.[155][37] 이온 주입 후에는 주입된 도펀트를 활성화하고 손상된 결정 구조를 복구하기 위해 로 어닐링[156][37] 또는 급속 열처리(RTA)와 같은 열처리 공정이 필수적이다. 최근에는 자외선(UV) 조사를 통해 저-κ 절연체의 유전율을 낮추는 공정도 이 범주에 포함된다. 또한, 산화 공정을 통해 실리콘 표면에 절연막을 형성하여 MOSFET과 같은 소자를 제작하는 것도 전기적 특성 변경의 일환으로 볼 수 있다.

최신 집적 회로는 이러한 네 가지 범주의 공정을 수백 번 이상 반복하며, 최대 11개 이상의 금속 배선 층을 쌓아 만들어진다. 각 공정 단계에서 웨이퍼가 처리될 조건 목록을 '레시피(recipe)'라고 부른다.[157] 반도체 공정에서는 웨이퍼 전체에 걸쳐 균일한 품질을 유지하는 것이 중요한 과제이며, 공정 변동성을 최소화하기 위한 노력이 계속되고 있다.[158]

반도체 제조 공정은 극도로 청정한 환경을 요구한다. 과거 소자 선폭이 10 마이크로미터 이상으로 컸을 때는 오염 관리가 지금처럼 중요하지 않았지만,[137] 소자가 고도로 집적되면서 미세한 입자 하나가 치명적인 결함으로 이어질 수 있게 되었다. 오늘날 반도체 공장은 클린룸 내부에 건설되며, 천장에 설치된 수많은 팬 필터 유닛(FFU)이 공기를 지속적으로 여과하고 순환시켜 청정도를 유지한다. 격자형 바닥 구조는 공기가 위에서 아래로 흐르는 층류를 만들어 입자가 바닥으로 빠르게 가라앉도록 돕는다. 작업자들은 신체에서 발생하는 입자로부터 웨이퍼를 보호하기 위해 머리부터 발끝까지 가리는 클린룸복을 착용한다.[139] 웨이퍼는 FOUP이나 SMIF 포드와 같은 밀폐 용기에 담겨 공정 장비 사이를 이동하며, 이를 통해 클린룸 공기로부터 웨이퍼를 격리하여 오염 가능성을 더욱 낮춘다.[10][7] 또한, 사람 자체가 주요 오염원이기 때문에[138][139][140] 클린룸 내 작업 인원을 최소화하고 자동화 설비를 적극적으로 활용한다.

전체 제조 공정은 크게 웨이퍼 위에 소자를 만드는 '''전공정(FEOL)''', 소자들을 금속 배선으로 연결하는 '''후공정(BEOL)''', 그리고 완성된 칩을 보호하고 외부와 연결하는 '''패키징 및 테스트''' 단계로 나눌 수 있다. 각 단계는 다시 여러 세부 공정으로 구성된다.

3. 1. 전공정 (Front-End-Of-Line, FEOL)

반도체 제조 공정은 크게 웨이퍼 위에 트랜지스터와 같은 개별 소자를 직접 만드는 전공정(FEOL, Front-End-Of-Line)과, 이렇게 만들어진 소자들을 금속 배선으로 연결하여 칩의 기능을 완성하는 후공정(BEOL, Back-End-Of-Line)으로 나뉜다.[117] 전공정은 실리콘 웨이퍼 상에 트랜지스터를 포함한 다양한 소자의 핵심 구조를 형성하는 복잡하고 정밀한 단계들의 연속이다.[159][160]전공정은 고순도의 단결정 실리콘 웨이퍼를 준비하는 것에서 시작한다. 때로는 소자 성능 향상을 위해 웨이퍼 표면에 에피택시 공법으로 초고순도 실리콘 층을 성장시키거나,[159][160] 실리콘-게르마늄(SiGe)과 같은 물질을 사용하여 결정 격자에 의도적인 변형(strain)을 주는 '스트레인 공학' 기술을 적용하기도 한다.[125] 또한, 실리콘 층 사이에 절연막을 삽입하는 절연체 위에 실리콘(SOI) 기술을 통해 소자의 기생 효과를 줄일 수도 있다.

본격적인 소자 형성은 다음과 같은 핵심 공정 단계를 반복하며 진행된다. 각 단계는 특정 목적을 가지고 있으며, 전체 공정은 수백 번 이상 반복될 수 있다.

- 세정: 웨이퍼 표면의 미세한 오염물이나 이전 단계의 잔류물을 제거하여 각 공정 단계의 품질을 확보한다.[118][120][121]

- 증착: 절연막, 전도막 등 필요한 물질을 웨이퍼 위에 얇은 막 형태로 입힌다. 화학 기상 증착(CVD), 물리 기상 증착(PVD), 원자층 증착(ALD), 에피택시 등 다양한 기술이 사용된다.[113][125] 하이-κ 유전체 증착 등이 이 단계에 포함된다.[162][164][165]

- 포토리소그래피: 빛을 이용하여 웨이퍼 위에 회로 패턴을 형성하는 과정이다. 포토레지스트 도포, 노광, 현상 단계를 거쳐 특정 패턴을 만든다.

- 식각 (Etching): 포토리소그래피로 형성된 패턴을 마스크 삼아 불필요한 부분을 선택적으로 제거한다. 건식 식각과 습식 식각이 있으며, 미세 패턴 구현을 위해 원자층 식각(ALE)과 같은 정밀 기술도 사용된다.[145][146][124]

- 이온 주입: 트랜지스터의 소스, 드레인 등 특정 영역의 전기적 특성을 조절하기 위해 도펀트 불순물 이온을 웨이퍼 내부에 주입한다.[2]

- 열처리 (Annealing): 이온 주입 등으로 손상된 웨이퍼의 결정 구조를 회복시키고, 주입된 도펀트를 활성화시켜 원하는 전기적 특성을 갖도록 한다.[156][37]

- 화학 기계적 연마(CMP): 공정 과정에서 발생하는 웨이퍼 표면의 단차를 제거하여 평탄하게 만드는 과정으로, 다음 층을 쌓기 위한 준비 단계이다.[203]

이러한 전공정 단계들을 통해 웨이퍼 위에는 수많은 트랜지스터와 커패시터 등의 개별 소자들이 정교하게 만들어진다. 전공정이 완료된 웨이퍼는 후공정 단계로 넘어가 금속 배선 연결을 통해 최종적인 집적 회로로 완성된다.

3. 1. 1. 게이트 산화막 및 임플란트

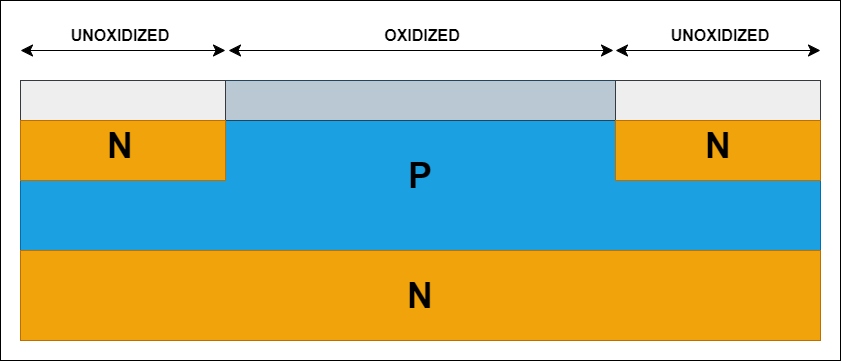

웨이퍼 공정의 전공정(FEOL, Front-End-of-Line) 단계에서는 트랜지스터가 실리콘 웨이퍼 위에 직접 형성된다.[159][160] 이 과정에서 트랜지스터의 핵심 요소인 게이트와 소스/드레인 영역이 만들어진다.전공정 표면 처리 후에는 먼저 게이트 절연체를 형성한다. 전통적으로는 이산화 규소(SiO2)가 널리 사용되었으나, 소자 크기가 작아지면서 누설 전류 문제가 심화되었다. 이를 해결하기 위해 2007년 45 nm 공정부터 인텔은 하이-κ 유전체(high-k dielectric)와 금속 게이트(metal gate) 기술(HKMG)을 도입했다.[162] 이는 1970년대 금속 게이트 (알루미늄 게이트)[163]를 대체했던 폴리실리콘 게이트를 다시 금속 기반 게이트로 바꾼 중요한 변화였다. 하프늄 산화물(HfO2)과 같은 하이-κ 물질은 기존의 질화 산화 규소(SiON)보다 유전율이 높아 게이트 절연막 두께를 물리적으로 늘리지 않고도 전기적 용량을 유지하면서 누설 전류를 크게 줄일 수 있다.[164][165] HKMG 공정은 하이-κ 물질 증착 후 금속 게이트를 형성하는 '게이트 퍼스트(gate-first)' 방식과, 일단 더미 게이트를 만들고 다른 공정을 진행한 뒤 마지막에 더미 게이트를 제거하고 금속 게이트를 채우는 '게이트 라스트(gate-last)' 방식으로 나뉜다.[168] 현재는 게이트 퍼스트 방식이 주로 사용되며,[169][170] 이 기술은 FinFET이나 나노시트 트랜지스터(GAA) 같은 차세대 트랜지스터 구조에도 계속 적용되고 있다.[171] DRAM 메모리에서는 2015년부터 이 기술이 채택되었다.[166]

게이트 구조가 형성된 후에는 소스 및 드레인 영역을 만든다. 이 영역에 특정 불순물을 주입하여 원하는 전기적 특성을 갖도록 만드는 과정을 반도체 도핑이라고 하며, 주로 이온 주입(ion implantation) 기술이 사용된다. 이온 주입은 도펀트 원소를 이온화하여 높은 에너지로 가속시킨 뒤 웨이퍼의 특정 깊이에 정확하게 주입하는 방식이다.[2] 고주파 구동 이온 소스나 집속 이온 빔(FIB) 등을 이용하여 정밀한 패턴과 깊이 조절이 가능하다. 이온 주입 후에는 불순물이 실리콘 격자 내에서 안정화되고 전기적으로 활성화되도록 열처리 공정(어닐링)을 거친다. 급속 열처리(RTA)나 레이저 어닐링 등의 방법이 사용된다. 동적 램(DRAM) 장치에서는 저장 커패시터도 이 시점에 제작되기도 한다.

이러한 게이트 형성 및 이온 주입 과정은 자기 정렬 게이트(self-aligned gate) 기술과 밀접하게 연관된다. 자기 정렬 방식은 게이트 전극 자체를 마스크로 사용하여 소스/드레인 영역의 이온 주입 위치를 정밀하게 제어함으로써, 게이트와 소스/드레인 간의 기생 전기 용량을 줄이고 소자 성능을 향상시키는 데 기여한다.

전체적으로 웨이퍼 표면에 회로를 형성하는 과정은 다음과 같은 단계를 반복적으로 거친다.

# 세정 및 건조: 웨이퍼 표면의 오염물을 제거한다.

# 포토레지스트 도포 및 포토리소그래피: 빛에 반응하는 감광액을 바르고 마스크를 이용해 원하는 회로 패턴을 형성한다.

# 식각(Etching): 패턴 외의 불필요한 부분을 제거한다. 드라이 에칭이나 습식 에칭 방식이 사용된다. 16nm/14nm 노드 이후로는 더 정밀한 원자층 식각(ALE) 기술의 사용이 증가하고 있다.[124]

# 박막 증착: 화학 기상 증착(CVD), 물리 기상 증착(PVD), 에피택셜 성장, 스퍼터링 등의 방법으로 필요한 물질(절연막, 전도막 등)을 얇게 쌓는다.

# 이온 주입: 소스/드레인 등 특정 영역에 불순물을 주입하여 전기적 특성을 조절한다.

# 열처리: 주입된 불순물을 활성화하고 결정 구조를 안정화시킨다.

# 화학 기계적 연마(CMP): 공정 중 울퉁불퉁해진 표면을 평탄하게 만든다.[203]

이러한 공정들은 회로의 복잡성에 따라 수백 번 이상 반복될 수 있다.

3. 2. 후공정 (Back-End-Of-Line, BEOL)

다양한 반도체 소자가 형성된 후, 원하는 전기 회로를 형성하기 위해 이들을 서로 연결하는 과정이 필요하다. 이 공정은 웨이퍼 공정 단계 중 후반부에 해당하며, 여러 단계를 통칭하여 '''후공정'''(Back-End-Of-Line, '''BEOL''')이라고 부른다. 이는 칩 제조의 최종 단계인 패키징 및 테스트를 의미하는 '백 엔드(Back-end)'와는 구분된다.BEOL 공정의 핵심은 유전체 층으로 절연된 금속 상호 연결 배선(상호연결)을 만드는 것이다. 절연 재료로는 전통적으로 이산화 규소(SiO2)나 규산염 유리가 사용되었지만, 신호 전달 속도를 높이기 위해 최근에는 저유전율 물질(low-k dielectric)이 사용되고 있다. 예를 들어 실리콘 옥시카바이드와 같은 물질은 SiO2(유전율 3.82)보다 낮은 약 2.7의 유전율을 제공하며, 2.2 수준의 더 낮은 유전율을 가진 재료도 칩 제조에 사용되고 있다.

BEoL 공정은 1995년경 350nm 및 250nm 공정 노드부터 본격적으로 도입되었으며, 이 시기부터 화학 기계적 연마(CMP) 기술도 함께 사용되기 시작했다. 당시에는 금속 배선 층을 2개 쌓는 것이 최첨단 기술이었다.[176][177]

최신 공정 기술이 발전하면서 BEOL 단계에도 변화가 생겼다. 22nm 노드부터 일부 제조업체는 트랜지스터와 BEOL의 상호 연결 부분을 잇는 중간 라인(Middle-Of-Line, MOL) 공정을 추가했다. MOL은 주로 텅스텐을 기반으로 하며, 트랜지스터 접합부와 상위 배선을 연결하는 역할을 한다.[178] 또한, 인텔은 10nm 노드에서 접점-활성-게이트(Contact-Over-Active-Gate, COAG) 기술을 도입하여 트랜지스터 게이트 바로 위에 접점을 형성함으로써 트랜지스터 밀도를 향상시켰다.[178]

3. 2. 1. 금속 배선

다양한 반도체 소자가 집적 회로 내에 만들어지면, 이들을 서로 연결하여 원하는 전기 회로를 구성해야 한다. 이 과정은 웨이퍼 공정 단계 중 후반부에 해당하며, 여러 단계를 통칭하여 BEOL(Back-End-Of-Line)이라고 부른다. 이는 칩 제조의 최종 단계인 패키징 및 테스트를 의미하는 '백 엔드(Back-end)'와는 구분된다. BEOL 공정의 핵심은 금속 배선(상호 연결 와이어)을 만들고 이를 유전체(절연체) 층으로 분리하는 것이다. 전통적으로 절연 재료로는 이산화 규소(SiO2)나 규산염 유리가 사용되었으나, 최근에는 신호 전달 속도를 높이기 위해 저유전율 물질이 도입되고 있다. 예를 들어 실리콘 옥시카바이드와 같은 물질은 유전율이 약 2.7 정도로 SiO2(유전율 3.82)보다 낮으며, 2.2 수준의 더 낮은 유전율을 가진 재료도 사용되고 있다.BEoL 공정은 1995년경 350nm 및 250nm 공정 노드(0.35 및 0.25 마이크론)부터 본격적으로 도입되었으며, 이 시기부터 화학 기계적 연마(CMP) 기술도 함께 사용되기 시작했다. 당시에는 금속 배선 층을 2개 쌓는 것이 최첨단 기술이었다.[176][177]

역사적으로 금속 배선은 주로 '''알루미늄'''(Al)으로 만들어졌다. '감산 알루미늄(Subtractive Aluminum)' 방식으로 불리는 이 공정은 웨이퍼 전체에 알루미늄 막을 입힌 후, 필요한 배선 모양만 남기고 나머지를 식각(에칭)하여 제거하는 방식이다. 이후 드러난 배선 위에 유전체 물질을 덮어 절연시킨다. 여러 층의 금속 배선을 연결하기 위해서는 유전체 층에 '비아(via)'라는 구멍을 뚫고, 화학 기상 증착법(CVD)을 이용해 그 안에 텅스텐(W)을 채워 넣는다. 이 방식은 비교적 적은 수의 배선 층(4개 이하)으로도 충분한 동적 임의 접근 메모리(DRAM) 같은 메모리 반도체 제조에 여전히 사용되고 있다. 알루미늄은 내부 결정 구조가 변하는 재결정을 막기 위해 구리(Cu)와 합금하여 사용하기도 했으며, 초기 칩에서는 금(Au)이 배선 재료로 사용되기도 했다.[179]

하지만 현대 마이크로프로세서와 같이 수많은 트랜지스터를 집적하는 경우, 배선 층의 수가 크게 늘어나면서 알루미늄 배선의 신호 전달 지연(타이밍 지연) 문제가 심각해졌다. 이를 해결하기 위해 배선 재료는 알루미늄에서 전기 전도성이 더 좋은 '''구리'''(Cu)로 바뀌었고,[180] 절연 재료 역시 기존의 이산화 규소에서 저유전율 물질로 대체되었다.[181][182] 구리 배선 공정에는 주로 다마신 공정이 사용되는데, 이는 유전체 층에 먼저 배선과 비아 모양의 홈을 파고 그 안에 구리를 채워 넣은 뒤, 불필요한 부분을 화학 기계적 연마(CMP)로 제거하는 방식이다. 이 방식은 기존 감산 방식보다 공정 단계를 줄여 비용 절감 효과도 가져온다. 배선 층이 여러 개 쌓이면서 각 층을 평탄하게 만드는 CMP 공정의 중요성이 더욱 커졌다. 표면이 평탄하지 않으면 다음 층의 리소그래피 공정 시 초점이 맞지 않아 패턴 형성이 어려워지기 때문이다. 다만, 배선 층 수가 3개 이하인 경우에는 건식 식각(dry etch back) 방식이 사용되기도 한다. 구리는 주변 물질로 쉽게 확산되어 소자 특성을 저하시킬 수 있기 때문에, 확산을 막는 장벽층(barrier layer)이 필수적이며, 주로 질화 탄탈(TaN) 등이 사용된다.[183][178] 구리 배선 기술은 1997년 IBM에 의해 처음 상용화되었다.[184]

최신 공정에서는 트랜지스터와 첫 번째 금속 배선 층을 연결하는 중간 단계인 MOL(Middle-Of-Line) 공정이 추가되기도 한다. 22nm 노드부터 일부 도입된 MOL은 주로 텅스텐을 기반으로 하며, 하부 층은 트랜지스터의 접합부(소스/드레인)를 연결하고 상부 층은 텅스텐 플러그를 통해 상위 배선과 연결하는 역할을 한다. 인텔은 10nm 노드에서 COAG(Contact-Over-Active-Gate) 기술을 도입했는데, 이는 트랜지스터 게이트 바로 위에 접점(Contact)을 형성하여 트랜지스터 밀도를 더욱 높이는 기술이다.[178]

또한, 2014년에는 어플라이드 머티어리얼즈(Applied Materials)사가 22nm 노드에서 구리 배선을 코발트(Co)로 감싸는 기술을 제안했다. 이는 구리 원자의 이동(전자 이동 현상)을 막고 기존의 질화 탄탈 장벽층보다 더 얇게 형성할 수 있어 배선 저항을 낮추는 데 유리하다.[178][185]

3. 2. 2. 상호 연결

'''상호 연결'''(Interconnect)은 집적 회로(IC) 내부에 있는 수많은 트랜지스터와 다른 전자 소자들을 서로 연결하는 미세한 전선 배선 구조를 말한다. 이 배선은 칩이 제대로 작동하고 원하는 속도를 내는 데 매우 중요한 역할을 하며, 반도체 제조 기술이 발전함에 따라 상호 연결 기술도 함께 발전해 왔다.

초기 반도체 칩에서는 주로 '''알루미늄'''(Al)을 배선 재료로 사용했다. '감산(subtractive) 알루미늄 공정'이라는 방식을 썼는데, 이는 웨이퍼 위에 알루미늄 막을 전체적으로 얇게 입힌 다음, 포토 리소그래피 기술로 배선 모양을 그리고 필요 없는 부분을 식각(etching)하여 깎아내는 방식이다. 만들어진 알루미늄 배선 위에는 전기가 통하지 않는 절연 물질을 덮고, 서로 다른 층에 있는 배선을 연결해야 할 때는 절연막에 '비아(via)'라는 작은 구멍을 뚫는다. 그리고 이 구멍 안에 텅스텐(W) 금속을 CVD 방법으로 채워 넣어 위아래층의 배선을 전기적으로 연결했다. 이 알루미늄 배선 방식은 공정이 비교적 간단해서, DRAM처럼 배선 층수가 많지 않은(보통 4개 층 이하) 메모리 반도체를 만들 때 지금도 종종 사용된다. 알루미늄은 내부 구조가 변형되는 재결정을 막기 위해 약간의 구리를 섞어 합금 형태로 사용하기도 했고, 아주 초기 칩에서는 금(Au)을 배선 재료로 쓰기도 했다.[179]

하지만 마이크로프로세서처럼 복잡하고 빠른 연산이 필요한 칩에는 트랜지스터가 훨씬 더 많이 들어가고, 이를 연결하는 배선 구조도 매우 복잡해진다. 알루미늄 배선은 전기 저항이 상대적으로 높아 신호가 전달되는 데 시간이 걸리는 '신호 지연'(timing delay) 문제가 점점 심각해졌다.[180] 이 문제를 해결하기 위해 1997년 IBM에서 처음으로 '''구리'''(Cu)를 배선 재료로 사용하는 기술을 개발했다.[184] 구리는 알루미늄보다 전기 저항이 훨씬 낮아 전기가 더 잘 통하므로, 신호 지연을 크게 줄여 칩의 작동 속도를 높일 수 있다. 또한, 구리 배선은 '다마신(Damascene) 공정'이라는 새로운 방식으로 만드는데, 이는 제조 공정을 단순화하고 생산 비용을 낮추는 데도 도움이 되었다. 다마신 공정은 먼저 절연막에 배선이 들어갈 길(trench)과 비아 구멍을 미리 파놓고, 그 위에 구리를 채워 넣은 다음, CMP(Chemical Mechanical Polishing)라는 연마 기술로 표면의 불필요한 구리를 갈아내어 배선만 남기는 방식이다.

상호 연결 기술의 발전은 배선 재료뿐 아니라 배선 사이를 채우는 절연 물질에도 변화를 가져왔다. 기존에 사용하던 이산화 규소(SiO₂) 대신 'low-κ 유전체'(low-k dielectric)라는 새로운 절연 물질을 사용하기 시작했다. 이 물질은 유전율(k) 값이 낮아 배선들 사이에 발생하는 전기적 간섭(정전 용량)을 줄여주기 때문에, 신호가 더 빠르고 정확하게 전달될 수 있도록 돕는다.[181][182] 또한, 칩에 배선 층이 여러 겹으로 쌓이면서 각 층의 표면을 반듯하게 만드는 CMP 기술의 중요성이 더욱 커졌다. 각 층이 평평하지 않으면 다음 층에 배선 패턴을 그리는 포토 리소그래피 공정에서 초점이 맞지 않아 정밀한 회로를 만들기 어렵기 때문이다. 한편, 구리는 주변 물질로 쉽게 확산되어 칩의 성능을 저하시킬 수 있기 때문에, 구리 배선 주위에는 질화 탄탈럼(TaN)과 같은 얇은 보호막(장벽층, barrier layer)을 입혀 구리가 퍼져나가는 것을 막는다.[183][178]

최근에는 22nm 이하의 더 미세한 공정 기술이 도입되면서, 구리 배선 자체의 한계를 극복하기 위한 연구도 진행 중이다. 미세한 배선에서 전자가 이동하며 배선 모양을 변형시키는 '전자 이동'(electromigration) 현상을 줄이고, 더 얇은 장벽층을 만들기 위해 코발트(Co)를 구리 배선을 감싸거나 대체하는 재료로 사용하는 방안이 제안되었다.[178][185]

트랜지스터 제작 후 이들을 서로 연결하는 전체 공정을 배선 공정(Back End of Line, BEOL)이라고 부르며, 주요 배선 기술은 다음과 같이 분류할 수 있다.

| 배선 종류 | 설명 |

|---|---|

| 알루미늄 배선 | 초기 및 일부 메모리 반도체에 사용되는 전통적인 배선 방식. |

| 구리 배선 | 고성능 로직 반도체에 주로 사용되는 저저항 배선 방식. 다마신 공정으로 제작됨. |

| 다층 배선 | 여러 층의 금속 배선을 절연막을 사이에 두고 쌓아 올려 복잡한 회로를 구성하는 기술. |

3. 3. 후공정 (패키징 및 테스트)

테스트가 완료된 웨이퍼는 두께를 줄이는 공정을 거치는데, 이를 "백랩"(backlap),[191] "백피니시"(backfinish), "웨이퍼 백그라인드"(wafer backgrind) 또는 "웨이퍼 씬닝"(wafer thinning)[192]이라고 한다. 이후 웨이퍼에 홈을 내어 개별 다이(die)로 분리하는 웨이퍼 다이싱 공정을 진행한다. 이 과정을 통해 양품으로 판정된 칩만 다음 단계인 패키징 공정으로 넘어간다.집적 회로 패키징은 기능 테스트와 분류를 마친 다이를 외부 환경으로부터 보호하고 전기적 연결을 용이하게 만드는 과정이다. 일반적으로 플라스틱이나 세라믹 패키지를 사용하며, 다이를 패키지 기판에 부착하고(다이 본딩), 다이의 본드 패드와 패키지의 핀(pin)을 연결한 뒤(와이어 본딩), 다이 전체를 밀봉(몰딩)하는 순서로 진행된다. 본드 패드와 핀을 연결할 때는 주로 작은 본드 와이어가 사용된다. 1970년대에는 사람이 직접 손으로 와이어를 연결했지만, 현재는 자동화된 특수 기계가 이 작업을 수행한다. 전통적으로는 금(Gold) 와이어를 사용했고, 납 프레임(lead frame)은 솔더(solder)로 도금된 구리로 제작되었다. 하지만 납의 유해성 문제로 인해 현재는 RoHS 규정에 따라 납이 포함되지 않은 무연(lead-free) 납 프레임 사용이 의무화되었다. 본드 패드는 전통적으로 다이의 가장자리에 배치되었으나, 플립 칩(flip-chip) 기술을 사용하면 다이 표면 전체에 본드 패드를 배치할 수 있다.

칩 스케일 패키지(CSP)는 또 다른 패키징 기술이다. 일반적인 플라스틱 듀얼 인라인 패키지(DIP)는 실제 다이 크기보다 몇 배 더 크지만, CSP는 패키지 크기가 다이 크기와 거의 동일하다는 특징이 있다. CSP는 웨이퍼를 개별 칩으로 자르기 ''전''에 각 다이 단위로 패키징을 구성할 수도 있다.

패키징이 완료된 칩은 다시 테스트(패키지 테스트)를 거친다. 이 테스트는 패키징 과정 중 칩이 손상되지 않았는지, 다이와 외부 핀 간의 전기적 연결이 올바르게 이루어졌는지 등을 최종적으로 확인하기 위한 과정이다. 테스트를 통과한 칩은 레이저를 이용하여 패키지 표면에 칩의 이름과 번호 등을 새기는 마킹(marking) 작업을 거쳐 완제품이 된다.

이처럼 다이 테스트, 패키징, 최종 테스트까지의 공정을 통틀어 후공정(back-end process),[193] 포스트 팹(post-fab),[194] ATMP(Assembly, Test, Mark, and Package),[195] 또는 ATP(Assembly, Test, and Packaging)라고 부른다. 이러한 후공정은 반도체 설계 및 웨이퍼 제조를 담당하는 파운드리(Foundry)와 별개로, OSAT(Outsourced Semiconductor Assembly and Test, 외주 반도체 패키지 테스트)라고 불리는 후공정 전문 업체에서 수행되기도 한다. 파운드리는 주로 포토리소그래피, 식각 등 웨이퍼 위에 회로를 만드는 전공정(front-end process)을 담당한다.[196][197]

후공정은 크게 다음과 같은 주요 단계로 구성된다.

- 백그라인딩: 웨이퍼 뒷면을 갈아 얇게 만드는 공정

- 다이싱: 웨이퍼를 개별 칩으로 자르는 공정

- 다이 본딩: 칩(다이)을 패키지 기판이나 리드 프레임에 부착하는 공정

- 와이어 본딩: 칩의 본드 패드와 패키지의 리드를 금속선으로 연결하는 공정

- * 초음파 열압착(UNTC, Ultrasonic Thermocompression Bonding) 등의 방식이 사용된다.

- 몰딩(Molding): 칩과 와이어 등을 보호하기 위해 에폭시 등의 수지로 감싸는 공정

- 패키지 테스트: 완성된 패키지 칩의 전기적 특성 및 기능을 검사하는 공정

4. 웨이퍼

전형적인 웨이퍼는 매우 순수한 실리콘으로 만들어진다. 이는 결정 성장을 통해 단결정 원통형 잉곳 (boule)으로 초크랄스키 공정을 사용하여 성장시킨다. 이 잉곳을 약 0.75mm 두께의 웨이퍼로 잘라낸 다음, 매우 균일하고 평평한 표면을 얻기 위해 연마 과정을 거친다.

웨이퍼 크기는 시간이 지남에 따라 점차 커졌다. 초기 반도체 산업부터 현재까지 주요 웨이퍼 직경 변화는 다음과 같다.[40][41][51][52]

| 연도 | 직경 (mm) | 직경 (인치) |

|---|---|---|

| 1960 | 25mm | 1 |

| 1969 | 50mm | 2 |

| 1976 | 100mm | 4 |

| 1981 | 125mm | 5 |

| 1983 | 150mm | 6 |

| 1990 | 200mm | 8 |

| 2000 | 300mm | 12 |

웨이퍼 크기가 커짐에 따라 취급 방식도 변화했다. 초기 50mm (2인치) 웨이퍼 시대에는 핀셋을 사용하여 수동으로 다루었으나, 오염 문제를 줄이기 위해 진공 완드로 대체되었다.[42] 이후 여러 웨이퍼를 한 번에 담아 공정 단계 간에 운반할 수 있는 웨이퍼 캐리어 또는 카세트가 개발되었다. 초기에는 웨이퍼가 담긴 카세트 전체를 습식 에칭 및 세척 탱크에 담그는 방식도 사용되었으나, 100mm 웨이퍼부터는 균일한 처리가 어려워졌다. 150mm 웨이퍼가 도입될 무렵에는 카세트는 주로 운반 및 보관용으로 사용되었고, 로봇이 웨이퍼 취급에 널리 사용되기 시작했다. 200mm 웨이퍼는 카세트 무게 증가로 수동 취급이 위험해지면서 자동화가 더욱 가속화되었다.[43]

생산 과정에서 웨이퍼는 종종 로트(lot) 단위로 그룹화되어 웨이퍼 캐리어인 FOUP, SMIF 또는 웨이퍼 카세트에 담겨 관리된다. FOUP와 SMIF는 자동화된 AMHS(Automated Material Handling System)를 통해 팹(fab) 내의 공정 장비 사이를 자동으로 운송될 수 있다.[57] 웨이퍼 카세트는 추가적으로 웨이퍼 박스나 운반 상자에 넣어 보관 및 이동하기도 한다.[141]

웨이퍼 처리 방식에도 변화가 있었다. 세척[59], 이온 주입[60][61], 에칭[62], 어닐링[63], 산화[64]와 같은 일부 공정에서는 결과의 재현성을 높이기 위해 여러 웨이퍼를 한 번에 처리하는 배치(batch) 방식 대신 단일 웨이퍼 처리 방식을 채택하기 시작했다.[65][66] MEMS 제조에서도 유사한 경향이 나타났다.[67] 또한, 웨이퍼 처리 효율을 높이기 위해 여러 공정 챔버를 하나로 묶은 클러스터 도구(cluster tool)가 개발되었다. 예를 들어, 어플라이드 머티어리얼즈의 Precision 5000[48]이나 Producer[68][53]는 공유된 진공 및 공급 라인을 사용하면서도 각 챔버를 격리하여 품질 저하 없이 높은 생산성을 제공했다.

반도체 산업은 칩 수요 증가에 대응하여 더 큰 웨이퍼를 채택해 왔으며[56], 300mm 웨이퍼로의 전환과 함께 FOUP 사용이 보편화되었다.[57] 그러나 아날로그 IC, RF 칩, 전력 IC, BCDMOS, MEMS 소자와 같이 최첨단 공정이 필요하지 않은 많은 제품은 여전히 200mm 웨이퍼로 생산되고 있다.[58] 150mm에서 200mm로[53], 그리고 200mm에서 300mm로[54][55] 전환하는 과정에서는 기존 장비와 호환성을 유지하며 전환을 돕는 브리지 도구(bridge tool)가 사용되기도 했다.

5. 공정 단계 목록

다음은 현대 전자 장치 제작 과정에서 여러 번 사용되는 공정 기술 목록이다. 이 목록이 특정 순서를 의미하거나, 모든 기술이 제조 과정에서 사용됨을 나타내는 것은 아니다. 실제 공정 순서와 적용 기술은 파운드리의 공정 제공이나 자체 제품을 위한 종합 반도체 제조사(IDM)에 따라 다르며, 모든 반도체 장치가 모든 기술을 필요로 하지는 않는다. 이러한 공정을 수행하는 장비는 소수의 기업에서 제조하며, 모든 장비는 반도체 제조 공장이 시작되기 전에 테스트를 거쳐야 한다.[114] 이러한 공정은 집적 회로 설계 이후에 수행된다. 반도체 공장은 연중무휴로 운영되며,[115] 많은 공장에서 주로 칩 세척을 위해 대량의 물을 사용한다.[116]

- 웨이퍼 공정 (프론트 엔드라고도 함)[117]

- * 습식 세정

- ** 아세톤, 트리클로로에틸렌 또는 초순수와 같은 용매로 세정, 때로는 웨이퍼를 회전시키면서 세정

- ** 피라냐 용액

- ** RCA 세정

- ** 웨이퍼 스크러빙

- ** 스핀 세정[118]

- ** 제트 분사 세정[118]

- ** 저온 에어로졸[119]

- ** 메가소닉 세정[120]

- ** 침지 배치 세정[121]

- * 표면 패시베이션

- * 포토 리소그래피

- ** 감광액 코팅 (전체 웨이퍼에 액체 형태로 적용되는 경우가 많음)

- ** 감광액 베이킹 (오븐에서 고형화)

- ** 엣지 비드 제거[122][123]

- ** 노광 (포토 리소그래피 스텝퍼, 스캐너 또는 마스크 정렬기에서)

- ** 노광 후 베이킹 (PEB)은 감광액의 내구성을 향상시킴

- ** 현상 (액체 현상액을 사용하여 레지스터의 일부를 제거하여 이온 주입, 층 증착, 에칭 등을 위해 웨이퍼의 일부만 노출시킴)

- * 이온 주입 (도펀트를 웨이퍼에 삽입하여 전도성이 증가하거나 감소하는 영역을 생성)

- * 에칭

- ** 건식 에칭 (플라즈마 에칭)

반응성 이온 에칭 (RIE)

* 심층 반응성 이온 에칭 (DRIE)

* 원자층 에칭 (ALE)

** 플라즈마 ALE[124]

** 열 ALE[124]

- ** 습식 에칭

완충 산화물 에칭

- * 화학 기상 증착 (CVD)

- ** 유기 금속 화학 기상 증착 (MOCVD), LED에 사용

- * 원자층 증착 (ALD)

- * 물리 기상 증착 (PVD)

- ** 스퍼터링

- ** 증발

- * 에피택시[113][125]

- ** 분자선 에피택시 (MBE)[126]

- * 이온 빔 증착[127]

- * 플라즈마 애싱 (완전한 감광액 제거/감광액 스트리핑, 건식 스트립이라고도 함,[128] 과거에는 레지스트 스트리퍼라는 화학 용매로 수행,[129][130] 웨이퍼가 포토 리소그래피를 다시 거치도록 허용)

- * 열처리

- ** 급속 열처리 (RTP), 급속 열 어닐링

- ** 밀리초 열처리, 밀리초 어닐링, 밀리초 공정, 플래시 램프 어닐링 (FLA)

- ** 레이저 어닐링

- ** 로 어닐링

- ** 열 산화

LOCOS

- * 레이저 리프트 오프 (LED 생산용[131])

- * 전기화학적 증착 (ECD). 전기 도금 참조.

- * 화학적 기계적 연마 (CMP)

- * 웨이퍼 테스트 (자동 테스트 장비를 사용하여 전기적 성능을 확인, 이 단계에서 레이저 트리밍도 수행 가능)

- 다이 준비

- * 실리콘 관통 비아 제조 (3차원 집적 회로의 경우)

- * 웨이퍼 마운팅 (웨이퍼는 다이싱 테이프를 사용하여 금속 프레임에 장착)

- * 웨이퍼 백그라인딩 및 연마[132] (스마트카드 또는 PCMCIA 카드와 같은 얇은 장치 또는 웨이퍼 본딩 및 적층을 위해 웨이퍼의 두께를 줄임, 이는 Dice Before Grind 또는 DBG라고 하는 공정에서 웨이퍼 다이싱 중에 발생할 수도 있음[133][134])

- * 웨이퍼 본딩 및 적층 (3차원 집적 회로 및 MEMS의 경우)

- * 재분배층 제조 (WLCSP 패키지의 경우)

- * 웨이퍼 범핑 (플립 칩 BGA (볼 그리드 어레이) 및 WLCSP 패키지의 경우)

- * 다이 절단 또는 웨이퍼 다이싱

- IC 패키징

- * 다이 부착 (다이는 전도성 페이스트 또는 다이 부착 필름을 사용하여 리드 프레임에 부착됨[135][136])

- * IC 본딩: 와이어 본딩, 열음파 본딩, 플립 칩 또는 테이프 자동 본딩 (TAB)

- * IC 캡슐화 또는 집적 열 분산기 (IHS) 설치

- ** 몰딩 (열팽창을 제어하기 위해 유리 가루를 충전재로 포함할 수 있는 특수 플라스틱 몰딩 컴파운드 사용)

- ** 베이킹

- ** 전기 도금 (주석으로 구리 리드를 리드 프레임에 도금하여 납땜을 더 쉽게 만듦)

- ** 레이저 마킹 또는 실크 스크린 인쇄

- ** 트리밍 및 성형 (리드 프레임을 서로 분리하고 리드 프레임의 핀을 구부려 인쇄 회로 기판에 장착할 수 있도록 함)

- IC 테스트

또한 라이트 에칭과 같은 단계가 수행될 수 있다.

6. 오염 및 결함 방지

과거 소자 선폭이 약 10μm보다 훨씬 컸을 때는 반도체 순도가 오늘날의 소자 제조만큼 중요한 문제가 아니었다. 1960년대에는 작업자들이 평상복을 입고 반도체 소자를 다룰 수 있었다.[137] 그러나 소자가 더욱 고도로 집적됨에 따라, 아주 작은 입자 하나라도 결함의 원인이 될 수 있어 클린룸의 중요성이 커졌다.

오늘날 반도체 제조 공장(팹)은 웨이퍼 위에 미세한 입자가 내려앉아 결함을 유발하는 것을 막기 위해 고도로 정화된 환경을 유지한다. 클린룸 내부는 외부보다 높은 압력으로 유지되며(가압), 천장에는 일정한 간격으로 팬 필터 유닛(FFU)이 설치되어 공기를 지속적으로 순환시키고 여과한다. 반도체 장비 자체에도 FFU가 장착되어 FOUP(Front Opening Unified Pod) 같은 웨이퍼 보관 용기 내부 환경까지 청정하게 관리한다. FFU와 격자형 바닥 구조는 공기가 위에서 아래로 흐르는 층류를 만들어 입자가 바닥으로 즉시 가라앉고 공중에 떠다니지 않도록 돕는다.[139]

작업자 역시 오염의 주요 원인이 될 수 있으므로, 반도체 제조 시설의 작업자는 클린룸복을 착용하여 인체에서 발생하는 입자로부터 소자를 보호해야 한다.[139] 또한, 클린룸 내 인원을 최소화하는 것도 중요한데, 이는 사람이 움직일 때 많은 입자를 발생시키기 때문이다.[138][139][140]

웨이퍼 취급 방식도 오염과 결함을 줄이는 방향으로 발전했다. 초창기 2인치 웨이퍼 시대에는 핀셋을 사용했지만, 이는 오염을 유발할 수 있어 입자를 덜 발생시키는 진공 완드로 대체되었다.[42] 웨이퍼를 담는 캐리어(카세트)가 개발되었고, 초기에는 웨이퍼가 담긴 채로 습식 공정에 투입되기도 했으나, 웨이퍼 크기가 커지면서 균일한 처리가 어려워졌다. 150mm 웨이퍼 시대부터는 로봇이 웨이퍼 취급에 널리 사용되기 시작했다.[43] 300mm 웨이퍼가 도입되면서는 웨이퍼를 외부 공기로부터 격리하는 FOUP나 SMIF 포드가 표준화되어, 웨이퍼가 이동 및 보관되는 동안 먼지 입자에 노출되는 것을 최소화했다. 이를 통해 수율을 크게 향상시킬 수 있었다.[10][7][57] FOUP와 장비 내부는 ISO 클래스 1 수준의 초정밀 청정 환경(미니 환경, 마이크로 환경)으로 관리된다.[10][7]

결함을 감지하고 제어하는 기술도 발전했다. 1984년 KLA 코퍼레이션은 최초의 자동 레티클 및 포토마스크 검사 장비를 개발했고,[45] 1985년에는 기존의 수동 현미경 검사를 대체하는 자동 웨이퍼 검사 장비를 선보였다.[46]

진공 장비 역시 오염 방지를 위해 개선되었다. 과거 확산 펌프는 오일을 사용해 웨이퍼를 오염시킬 수 있었으나, 오일을 사용하지 않는 터보분자 펌프로 대체되었다.[50]

7. 수율

반도체 웨이퍼 공정은 여러 단계를 순차적으로 거치므로, 각 단계 사이의 계측이 매우 중요하다. 예를 들어, 엘립소미터나 반사율 측정법을 이용한 박막 계측은 게이트 산화막, 포토레지스트 등 다양한 코팅의 두께와 굴절률 및 소멸 계수를 정밀하게 제어하는 데 사용된다.[186] 웨이퍼 계측 및 검사 장비는 웨이퍼가 이전 공정 단계에서 손상되지 않았는지 확인하여 불량품 발생을 미리 방지하는 역할을 한다. 만약 한 웨이퍼에서 불량 다이가 기준치 이상으로 발견되면, 추가 공정 비용을 절감하기 위해 해당 웨이퍼 전체를 폐기하기도 한다. 최근에는 물리적인 측정 없이 통계적 방법을 통해 웨이퍼의 특성을 예측하는 가상 계측 기술도 활용되고 있다.[187]

수율(Yield)은 한 웨이퍼에서 생산된 전체 다이 중 정상적으로 작동하는 다이의 비율을 백분율로 나타낸 것이다. 웨이퍼당 생산 가능한 다이의 수(DPW, Die per wafer)는 다이의 크기와 웨이퍼의 직경에 따라 달라지므로, 수율은 생산 효율성을 판단하는 핵심 지표가 된다. 수율 저하는 생산 비용 증가로 직결되기 때문에 반도체 제조에서 매우 중요한 관리 요소이다. 과거에는 주로 미세 먼지 입자가 수율 저하의 주된 원인이었으나, 1990년대 이후 기술 발전과 함께 공정 자체의 변동성, 사용되는 장비 등이 주요 원인으로 부상했다. 물론 먼지 입자는 여전히 많은 구형 생산 시설(팹)에서 문제로 남아 있으며, 특히 공정 미세화로 회로의 선폭이 줄어들면서 더 작은 먼지 입자도 수율에 치명적인 영향을 미칠 수 있게 되었다. 이러한 문제를 해결하기 위해 생산 라인 자동화, 장비 내부의 청정 환경(미니 인바이런먼트) 유지, 웨이퍼 이송 용기인 FOUP 및 SMIF 사용 등을 통해 먼지로 인한 결함을 줄이고 있다. 높은 수율을 유지하는 것은 정상 작동하는 칩의 판매 가격 경쟁력을 확보하고, 불량 칩으로 인한 손실을 만회하며, 전체 웨이퍼 처리 비용을 절감하는 데 필수적이다. 수율은 생산 공정뿐만 아니라 팹의 설계와 운영 방식에도 영향을 받는다.

수율을 높이기 위해서는 오염 물질과 생산 공정 전반에 대한 엄격한 관리가 필요하다. 오염 물질은 화학적 불순물과 물리적인 먼지 입자로 나눌 수 있다. 특히 킬러 결함(killer defect)은 트랜지스터와 같은 소자의 완전한 고장을 유발하는 먼지 입자로 인해 발생하며, 때로는 무해한 결함도 존재한다. 일반적으로 킬러 결함을 유발하는 입자의 크기는 해당 공정에서 형성되는 회로 패턴(특징) 크기의 약 1/5 수준이다. 예를 들어, 100nm 공정에서는 20nm 크기의 입자만으로도 킬러 결함이 발생할 수 있다. 정전기 역시 수율에 부정적인 영향을 줄 수 있다. 화학적 오염 물질 또는 불순물에는 철, 구리, 니켈, 아연, 크롬, 금, 수은, 은과 같은 중금속, 나트륨, 칼륨, 리튬과 같은 알칼리 금속, 그리고 알루미늄, 마그네슘, 칼슘, 염소, 황, 탄소, 불소 등이 포함된다. 이러한 원소들이 실리콘 웨이퍼와 접촉하면 수율이 크게 저하될 수 있으므로, 접촉을 최대한 방지하는 것이 중요하다. 특정 화학 혼합물을 사용하여 실리콘 웨이퍼에서 이러한 불순물을 제거할 수 있으며, 제거 대상 원소에 따라 효과적인 혼합물이 다르다.

수율을 예측하고 관리하기 위해 여러 통계적 모델이 사용된다. 대표적인 모델로는 머피(Murphy) 모델, 푸아송(Poisson) 모델, 이항(Binomial) 모델, 무어(Moore) 모델, 시즈(Seeds) 모델 등이 있다. 어떤 단일 모델이 모든 경우에 완벽하게 들어맞는 것은 아니며, 실제 웨이퍼 상에서 불량 다이가 발생하는 분포 패턴(예: 웨이퍼 가장자리에 집중되는지, 전체적으로 균일하게 분포하는지, 특정 영역에 군집하는지 등)을 고려하여 가장 적합한 모델을 선택해야 한다. 예를 들어, 머피 모델은 불량 다이가 웨이퍼 가장자리에서 더 많이 발생한다고 가정하는 반면, 푸아송 모델은 불량 다이가 웨이퍼 전체에 비교적 균등하게 퍼져 있다고 가정하고, 시즈 모델은 불량 다이가 특정 영역에 모여 발생하는 경향(클러스터링)을 가정한다.[190]

일반적으로 다이의 크기가 작을수록 생산 비용이 절감된다. 이는 동일한 크기의 웨이퍼에 더 많은 수의 다이를 집적할 수 있기 때문이다. 웨이퍼는 전체 단위로 가공되고 가격이 책정되므로, 웨이퍼당 생산되는 다이 수가 많을수록 개별 다이의 원가는 낮아진다. 또한, 다이 크기가 작으면 웨이퍼 표면에서 결함이 발생할 수 있는 면적이 줄어들어 잠재적으로 더 높은 수율을 달성하는 데 유리할 수 있다. 하지만 작은 다이로 더 큰 다이와 동일하거나 더 우수한 성능을 구현하려면 내부 회로 패턴의 크기(특징 크기)를 더욱 미세하게 만들어야 한다. 이는 공정 변동을 더욱 엄격하게 제어하고, 오염 수준을 낮추는 등 생산 환경의 청정도를 높여야만 높은 수율을 유지할 수 있다는 것을 의미한다. 계측 도구는 생산 공정 중 웨이퍼를 지속적으로 검사하여 수율을 예측하는 데 사용되며, 이를 통해 결함이 지나치게 많을 것으로 예상되는 웨이퍼는 조기에 폐기하여 불필요한 추가 공정 비용 발생을 막을 수 있다.[188]

8. 장치 테스트

전공정이 완료된 후에는 반도체 소자 또는 칩이 제대로 작동하는지 확인하기 위해 다양한 전기적 테스트를 거친다. 웨이퍼에서 제대로 작동하는 소자의 비율을 '''수율'''이라고 부른다. 제조업체는 일반적으로 수율을 외부에 공개하지 않지만,[188] 때로는 30% 정도로 낮을 수도 있다. 이는 웨이퍼에 있는 칩 중 30%만이 의도한 대로 작동한다는 의미이다. 공정 변동은 낮은 수율을 유발하는 여러 원인 중 하나이다. 이러한 테스트는 불량 칩이 상대적으로 비싼 패키지로 조립되는 것을 막기 위해 필수적이다.

수율은 종종 다이(칩) 크기와 관련이 있지만 항상 그런 것은 아니다. 예를 들어, 2019년 12월 TSMC는 다이 크기가 17.92mm2인 5nm 테스트 칩의 평균 수율이 약 80%이며, 웨이퍼당 최대 수율은 90% 이상이라고 발표했다. 반면, 다이 크기가 100mm2로 증가하자 수율은 32%로 감소했다.[189] 다이 크기와 관계없이 웨이퍼에서 칩을 사용할 수 없게 만드는 결함의 수는 웨이퍼의 결함 밀도(D0)로 나타낼 수 있으며, 보통 cm2 단위로 표현된다.

팹(제조 공장)은 전자 테스터를 사용하여 웨이퍼 상의 칩을 테스트한다. 이 테스터는 칩의 접점에 작은 프로브를 접촉시켜 전기 신호를 주고받는다. 과거에는 불량 칩에 염료를 떨어뜨려 표시했지만, 현재는 웨이퍼 테스트 데이터를 중앙 컴퓨터 데이터베이스에 기록하고, 칩이 미리 정해진 테스트 기준(예: 최대 작동 주파수, 칩당 작동하는 코어 수 등)에 따라 분류되는 전자적인 방식이 주로 사용된다. 이 분류 과정을 빈닝(binning)이라고 하며, 그 결과는 웨이퍼 맵에 기록되어 제조 결함을 추적하거나 불량 칩을 식별하는 데 사용된다. 이 맵은 이후 웨이퍼 조립 및 패키징 공정에서도 활용된다. 빈닝을 통해, 원래는 폐기될 칩이라도 성능 기준을 낮춘 하위 제품으로 재활용하여 전체적인 장치 수율을 높일 수 있다. 이는 특히 모든 코어가 완벽하게 작동하는 칩을 만들기 어려운 GPU나 CPU에서 유용하다. eFUSE 기술은 빈닝 과정에서 의도대로 작동하지 않는 코어를 비활성화하거나, 시장 요구에 맞춰 동일한 칩을 성능별(저가형, 중가형, 고가형)로 나누는 데 사용될 수 있다. 또한 칩 설계 시 일부 부품이 고장 나더라도 정상 작동할 수 있도록 예비 부품을 포함하는 경우도 있다.

칩은 패키징 공정을 거친 후에도 다시 테스트를 받는다. 이는 패키징 과정에서 본드 와이어가 누락되거나 칩의 아날로그 성능이 변할 수 있기 때문이다. 이 단계를 "최종 테스트"라고 부른다. 경우에 따라 X선을 사용하여 칩 내부를 검사하기도 한다.

일반적으로 팹은 테스트 시간에 따라 비용을 청구하며, 가격은 초당 센트 단위로 책정된다. 테스트 시간은 수 밀리초에서 수 초까지 다양하며, 테스트 비용을 줄이기 위해 테스트 소프트웨어를 최적화한다. 또한 많은 테스터는 여러 칩을 동시에 병렬로 테스트할 수 있는 기능(멀티 사이트 테스트)을 갖추고 있어 효율성을 높인다.

칩 설계 단계에서부터 테스트 효율을 높이고 비용을 절감하기 위한 기능들이 포함되기도 한다. 대표적인 예로 스캔 체인이나 내장 자가 테스트(BIST, Built-In Self-Test)가 있다. 특수한 아날로그 공정을 사용하는 설계의 경우, 설계 명세에 맞는 정밀한 저항 값을 얻기 위해 테스트 중에 웨이퍼에 레이저를 조사하여 미세 조정(레이저 트리밍)하기도 한다.

좋은 설계는 공정 코너(높은 작동 온도나 팹 공정 단계의 극한 조건에서 발생하는 실리콘 동작의 극단적인 경우)를 고려하여 테스트하고 통계적으로 관리한다. 대부분의 설계는 최소 64개의 공정 코너를 처리하도록 만들어진다.

9. 유해 물질

반도체 제조 공정에는 많은 유해 물질이 사용된다.[198] 주요 유해 물질은 다음과 같다.

- 비소, 안티몬, 인과 같은 유독성 원소 도펀트.

- 이온 주입 도핑에 사용되는 아르신 및 포스핀, 트랜지스터 상호 연결에서 텅스텐의 화학 기상 증착 증착에 사용되는 육불화 텅스텐, 폴리실리콘 증착에 사용되는 실란과 같은 유독성 화합물.[199]

- 에칭 및 세정에 사용되는 과산화 수소, 발연 질산, 황산, 불산과 같은 고반응성 액체.

이러한 위험 물질에 작업자가 직접 노출되지 않도록 하는 것이 매우 중요하다. 집적 회로 (IC) 제조 산업에서 흔히 볼 수 있는 높은 수준의 자동화는 노출 위험을 줄이는 데 도움이 된다. 대부분의 제조 시설에서는 작업자와 환경에 대한 위험을 관리하기 위해 습식 스크러버, 연소기, 가열 흡수 카트리지 등[200][201][202]의 배기 관리 시스템을 사용한다.

10. 상용 MOSFET 노드 타임라인

반도체 제조 공정에서 '''피처 사이즈'''는 패턴화할 수 있는 가장 작은 선의 너비(선폭)를 의미하며,[11][12] 이는 주로 포토 리소그래피 기술로 결정된다.[13] 특정 '''반도체 공정'''은 칩의 각 층에 형성되는 피처의 최소 크기와 간격에 대한 규칙을 가지며,[15] 새로운 공정 세대는 일반적으로 더 작은 피처 크기와 더 좁은 간격을 특징으로 한다. 이를 통해 기존 칩 설계를 축소하여 비용을 절감하고 성능을 개선하며, 단위 면적당 트랜지스터 밀도를 높일 수 있다.[15]

초기 반도체 공정은 HMOS나 CHMOS처럼 세대별로 임의의 이름을 사용했다. 이후 각 새로운 공정 세대는 기술 노드[16] 또는 공정 노드[17][18]로 불리게 되었으며, 공정의 최소 피처 사이즈를 나노미터(nm) 또는 역사적으로 마이크로미터(μm) 단위로 표시했다. 예를 들어 "90 nm 공정"과 같이 공정의 트랜지스터 게이트 길이를 나타내는 것으로 여겨졌다.

그러나 1994년 이후, 공정 노드를 나타내는 나노미터 숫자는 실제 게이트 길이나 트랜지스터 밀도와 직접적인 관련이 없는 마케팅 용어로 변질되었다.[19][20] 예를 들어, 인텔의 10 nm 공정은 실제 피처 크기나 트랜지스터 밀도 면에서 TSMC의 7 nm 공정과 유사하며,[21][22][20] 글로벌파운드리의 12 nm와 14 nm 공정도 비슷한 피처 사이즈를 가진다.[21] 이는 공정 노드 명칭이 실제 기술 수준을 반영하기보다는 마케팅 전략의 일환으로 사용되고 있음을 보여준다.[76][77][78]

상용 MOSFET 기술 노드의 주요 발전 과정은 다음과 같다.

- 1960년대: CMOS 기술이 1963년 페어차일드 반도체에서 개발되었고,[34][35] 1968년 RCA가 4000 시리즈 집적 회로를 통해 상용화했다. 초기 공정은 20 마이크로미터에서 시작하여 점차 10 마이크로미터 공정으로 축소되었다.[36] 또한 사파이어 위에 실리콘(SOS) 기술 연구가 시작되었다.[38][39]

- 1980년대: 바이폴라, CMOS, DMOS 소자를 통합한 BCDMOS 공정이 1985년 SGS(현 ST마이크로일렉트로닉스)에 의해 발명되었다.[47]

- 2001년 이후: AMD는 SOI 기술을 130 nm부터 32 nm 공정까지의 프로세서에 적극적으로 활용했다.[72]

- 2011년: 인텔은 22 nm 노드에서 FinFET(핀 필드 효과 트랜지스터) 기술을 선도적으로 도입했다. 이는 기존 평면 트랜지스터의 누설 전류 문제를 해결하고 성능과 에너지 효율을 크게 개선한 중요한 기술 전환이었다.[85][86][87][88][89]

- 2018년 이후: FinFET의 뒤를 이을 차세대 트랜지스터 구조로 GAAFET(Gate-All-Around FET) 기반 기술들이 활발히 연구 및 개발되었다. 여기에는 나노와이어, 나노시트(삼성전자의 MBCFET, 인텔의 나노리본), 수직 FET(VFET), 상보형 FET(CFET) 등이 포함된다.[91][92][93][94][95][96][97][98][99]

- 2019년: 14 nm 및 10 nm 칩이 인텔, UMC, TSMC, 삼성, 마이크론, SK하이닉스, 키옥시아(구 도시바 메모리), 글로벌파운드리 등 여러 기업에서 대량 생산되었다. 7 nm 칩은 TSMC와 삼성이 대량 생산을 주도했으며, 5 nm 공정은 삼성이 생산을 시작했다.[101] 당시 TSMC의 5 nm N5 노드가 가장 높은 트랜지스터 밀도를 기록했다.[102][103] 삼성과 TSMC는 3 nm 노드 생산 계획을 발표하며 미세 공정 경쟁을 이어갔다. 반면, 글로벌파운드리는 막대한 투자 비용 부담으로 인해 12 nm 이하 첨단 노드 개발을 중단하기로 결정했다.[104]

- 2022년: 삼성전자는 세계 최초로 GAAFET 구조(MBCFET)를 적용한 3 nm 공정 양산을 시작하며 차세대 트랜지스터 기술 경쟁에서 중요한 이정표를 세운 것으로 평가된다.

참조

[1]

웹사이트

8 Things You Should Know About Water & Semiconductors

https://www.chinawat[...]

2013-07-11

[2]

서적

Handbook of Semiconductor Manufacturing Technology

CRC Press

[3]

논문

Die singulation technologies for advanced packaging: A critical review

https://doi.org/10.1[...]

2012-04-06

[4]

학회발표

Advanced FOUP purge using diffusers for FOUP door-off application

https://ieeexplore.i[...]

2014

[5]

학회발표

450mm FOUP/LPU system in advanced semiconductor manufacturing processes: A study on the minimization of oxygen content inside FOUP when the door is opened

https://ieeexplore.i[...]

[6]

논문

Moisture Prevention in a Pre-Purged Front-Opening Unified Pod (FOUP) During Door Opening in a Mini-Environment

https://ieeexplore.i[...]

2018

[7]

논문

Clean-room Technologies for the Mini-environment Age

https://www.hitachi.[...]

2021-11-01

[8]

학회발표

FOUP purge performance improvement using EFEM flow converter

https://ieeexplore.i[...]

2016

[9]

논문

A Numerical Study on the Effects of Purge and Air Curtain Flow Rates on Humidity Invasion Into a Front Opening Unified Pod (FOUP)

https://ieeexplore.i[...]

2022

[10]

논문

Performance of Different Front-Opening Unified Pod (FOUP) Moisture Removal Techniques With Local Exhaust Ventilation System

https://ieeexplore.i[...]

2020

[11]

서적

Handbook of Semiconductor Manufacturing Technology

https://books.google[...]

CRC Press

2017-12-19

[12]

서적

Fundamental Principles of Optical Lithography: The Science of Microfabrication

https://books.google[...]

John Wiley & Sons

2008-03-11

[13]

서적

Extending Moore's Law through Advanced Semiconductor Design and Processing Techniques

https://books.google[...]

CRC Press

2018-09-13

[14]

서적

Semiconductor Memory Devices and Circuits

https://books.google[...]

CRC Press

2022-04-19

[15]

웹사이트

Die shrink: How Intel scaled-down the 8086 processor

https://www.righto.c[...]

2020-06

[16]

웹사이트

Overall Roadmap Technology Characteristics

https://www.semicond[...]

Semiconductor Industry Association

[17]

웹사이트

A Brief History of Process Node Evolution

https://www.design-r[...]

[18]

웹사이트

Technology Node - WikiChip

https://en.wikichip.[...]

[19]

웹사이트

A Better Way To Measure Progress in Semiconductors

https://spectrum.iee[...]

2020-07-21

[20]

웹사이트

Intel 10nm isn't bigger than AMD 7nm, you're just measuring wrong

https://www.pcgamer.[...]

2020-04-29

[21]

웹사이트

Intel's 10nm Cannon Lake and Core i3-8121U Deep Dive Review

https://www.anandtec[...]

[22]

웹사이트

VLSI 2018: GlobalFoundries 12nm Leading-Performance, 12LP

https://fuse.wikichi[...]

2018-07-22

[23]

논문

Surface Protection and Selective Masking during Diffusion in Silicon

https://iopscience.i[...]

1957

[24]

논문

Frosch and Derick: Fifty Years Later (Foreword)

https://iopscience.i[...]

2007-09-01

[25]

특허

Oxidation of semiconductive surfaces for controlled diffusion

https://patents.goog[...]

[26]

논문

Surface Protection and Selective Masking during Diffusion in Silicon

https://iopscience.i[...]

1957

[27]

서적

Advanced Materials Innovation: Managing Global Technology in the 21st century

https://books.google[...]

John Wiley & Sons

2016

[28]

서적

Makers of the Microchip: A Documentary History of Fairchild Semiconductor

https://books.google[...]

MIT Press

2010

[29]

서적

ULSI Process Integration III: Proceedings of the International Symposium

https://books.google[...]

The Electrochemical Society

2003

[30]

서적

History of Semiconductor Engineering

Springer Science & Business Media

2007

[31]

특허

Method of Manufacturing Semiconductor Devices

1959-05-01

[32]

특허

Semiconductor device

1960-05-15

[33]

학회발표

John Bardeen and transistor physics

2001

[34]

웹사이트

1963: Complementary MOS Circuit Configuration is Invented

https://www.computer[...]

[35]

학회발표

Nanowatt logic using field-effect metal-oxide semiconductor triodes

1963-02

[36]

서적

History of Semiconductor Engineering

https://books.google[...]

Springer Science & Business Media

2019-07-21

[37]

학술지

Ion Implantation in Silicon Technology

https://www.axcelis.[...]

American Institute of Physics

2003-06-00

[38]

학술지

Single-Crystal Silicon on a Sapphire Substrate

[39]

학술지

Grown-film silicon transistors on sapphire

1964-12-00

[40]

서적

Extending Moore's Law through Advanced Semiconductor Design and Processing Techniques

https://books.google[...]

CRC Press

2018-09-13

[41]

웹사이트

Evolution of the Silicon Wafer Infographic

https://f450c.org/in[...]

[42]

서적

How Transistor Area Shrank by 1 Million Fold

https://books.google[...]

Springer

2020-07-15

[43]

서적

Wafer Fabrication: Factory Performance and Analysis

https://books.google[...]

Springer

1995-11-30

[44]

웹사이트

Wafer fab costs skyrocketing out of control

https://www.chiphist[...]

[45]

웹사이트

Kla 200 Series

https://www.chiphist[...]

[46]

웹사이트

KLA 2020 - the tool that sparked the yield management revolution

https://www.chiphist[...]

[47]

웹사이트

Three Chips in One: The History of the BCD Integrated Circuit - IEEE Spectrum

https://spectrum.iee[...]

[48]

웹사이트

Applied Materials Precision 5000 CVD System

https://www.chiphist[...]

[49]

웹사이트

Series 900 In-Line Sputtering System by MRC

https://www.chiphist[...]

[50]

서적

Vacuum Deposition onto Webs, Films and Foils

https://books.google[...]

William Andrew

2011-06-21

[51]

컨퍼런스

The world's first 300 mm fab at Infineon - challenges and success

https://ieeexplore.i[...]

[52]

웹사이트

The 300mm Era Begins

https://www.edn.com/[...]

2000-07-10

[53]

웹사이트

Applied Materials Producer

https://www.chiphist[...]

[54]

웹사이트

300mm Semiconductor Wafers get a reprieve

http://www.chiphisto[...]

[55]

웹사이트

Novellus offers 300-mm CVD tool that's smaller than 200-mm, lower costs

https://www.eetimes.[...]

2000-07-10

[56]

컨퍼런스

Model-based silicon wafer criteria for optimal integrated circuit performance

https://pubs.aip.org[...]

1998-11-24

[57]

서적

Wafer Fabrication: Automatic Material Handling System

https://books.google[...]

Walter de Gruyter GmbH & Co KG

2018-09-24

[58]

웹사이트

200mm Fab Crunch

https://semiengineer[...]

2018-05-21

[59]

웹사이트

The future of batch and single-wafer processing in wafer cleaning

https://www.eetimes.[...]

2003-03-24

[60]

컨퍼런스

Manufacturing advantages of single wafer high current ion implantation

https://ieeexplore.i[...]

[61]

학술지

Approaches to single wafer high current ion implantation

https://doi.org/10.1[...]

2005-00-00

[62]

서적

Dry Etching for VLSI

https://books.google[...]

Springer

2013-06-29

[63]

학술지

Understanding the Impact of Batch vs. Single Wafer in Thermal Processing Using Cost of Ownership Analysis

https://link.springe[...]

1997-00-00

[64]

학술지

Contrasting single-wafer and batch processing for memory devices

https://ieeexplore.i[...]

2003-00-00

[65]

서적

Introduction to Microfabrication

https://books.google[...]

John Wiley & Sons

2005-01-28

[66]

컨퍼런스

Trends in single-wafer processing

https://ieeexplore.i[...]

[67]

웹사이트

Single Wafer vs Batch Wafer Processing in MEMS Manufacturing

https://www.cmmmagaz[...]

2024-02-18

[68]

웹사이트

Applied Materials Producer - a new revolution is upon us

http://www.chiphisto[...]

[69]

뉴스

Top 10 Worldwide Semiconductor Sales Leaders - Q1 2017 - AnySilicon

http://anysilicon.co[...]

2017-11-19

[70]

웹사이트

Transistor Aging Intensifies At 10/7nm And Below

https://semiengineer[...]

2017-07-13

[71]

웹사이트

Chip Aging Accelerates

https://semiengineer[...]

2018-02-14

[72]

웹사이트

Chip Architect: Intel and Motorola/AMD's 130 nm processes to be revealed.

http://chip-architec[...]

[73]

웹사이트

'Bridge tools' appear to be taking over 300-mm movement

https://www.edn.com/[...]

2001-04-26

[74]

웹사이트

Foundry Wars Begin

https://semiengineer[...]

2021-04-19

[75]

웹사이트

Get ready for 675-mm fabs in 2021

https://www.eetimes.[...]

2006-11-14

[76]

웹사이트

A Brief History of Process Node Evolution

https://www.design-r[...]

2019-07-09

[77]

뉴스

14nm, 7nm, 5nm: How low can CMOS go? It depends if you ask the engineers or the economists…

https://www.extremet[...]

2014-06-23

[78]

웹사이트

Exclusive: Is Intel Really Starting To Lose Its Process Lead? 7nm Node Slated For Release in 2022

https://wccftech.com[...]

2016-09-10

[79]

웹사이트

Life at 10nm. (Or is it 7nm?) And 3nm - Views on Advanced Silicon Platforms

https://www.eejourna[...]

2018-03-12

[80]

웹사이트

10 nm lithography process - WikiChip

https://en.wikichip.[...]

[81]

웹사이트

14 nm lithography process - WikiChip

https://en.wikichip.[...]

[82]

웹사이트

Intel's Process Roadmap to 2025: With 4nm, 3nm, 20A and 18A?!

https://www.anandtec[...]

[83]

웹사이트

Chip Aging Becomes Design Problem

https://semiengineer[...]

2018-08-09

[84]

웹사이트

Will Self-Heating Stop FinFETs

https://semiengineer[...]

2017-04-20

[85]

웹사이트

FinFET

https://semiengineer[...]

[86]

웹사이트

Foundries Rush 3-D Transistors - IEEE Spectrum

https://spectrum.iee[...]

[87]

웹사이트

Intel's Revolutionary 22 nm Transistor Technology

http://download.inte[...]

2011-05

[88]

뉴스

Intel's Tri-Gate transistors: everything you need to know

https://www.techrada[...]

2011-05-06

[89]

논문

CMOS Scaling Trends and Beyond

[90]

웹사이트

Start-up Seeks New Life for Planar Transistors - IEEE Spectrum

https://spectrum.iee[...]

[91]

웹사이트

The Increasingly Uneven Race to 3nm/2nm

https://semiengineer[...]

2021-05-24

[92]

웹사이트

What's Different About Next-Gen Transistors

https://semiengineer[...]

2022-10-20

[93]

웹사이트

Intel's Stacked Nanosheet Transistors Could be the Next Step in Moore's Law

https://spectrum.iee[...]

[94]

웹사이트

Nanowire Transistors Could Keep Moore's Law Alive

https://spectrum.iee[...]

[95]

웹사이트

Nanowires give vertical transistors a boost

https://physicsworld[...]

2012-08-02

[96]

웹사이트

Transistors will stop shrinking in 2021, but Moore's law will live on

https://arstechnica.[...]

2016-07-25

[97]

웹사이트

7nm, 5nm, 3nm: The new materials and transistors that will take us to the limits of Moore's law | Extremetech

https://www.extremet[...]

2013-07-26

[98]

웹사이트

What's After FinFETs?

https://semiengineer[...]

2017-07-24

[99]

웹사이트

Transistor Options Beyond 3nm

https://semiengineer[...]

2018-02-15

[100]

웹사이트

Samsung, GF Ramp FD-SOI

https://www.eetimes.[...]

2018-04-27

[101]

웹사이트

Samsung Completes Development of 5nm EUV Process Technology

https://www.anandtec[...]

[102]

웹사이트

Moore's Law is not Dead

https://www.tsmc.com[...]

TSMC

2019-08-14

[103]

웹사이트

TSMC Starts 5-Nanometer Risk Production

https://fuse.wikichi[...]

2019-04-06

[104]

웹사이트

GlobalFoundries Stops All 7nm Development: Opts To Focus on Specialized Processes

https://www.anandtec[...]

[105]

뉴스

Taiwan chipmakers keep workers 'imprisoned' in factories to keep up with global pandemic demand

https://www.telegrap[...]

2021-07

[106]

웹사이트

Chip shortages lead to more counterfeit chips and devices

https://arstechnica.[...]

2021-06-14

[107]

인터뷰

What are semiconductors, and why are they vital to the global economy?

https://www.weforum.[...]

[108]

뉴스

Countries lavish subsidies and perks on semiconductor manufacturers as a global chip war heats up

https://www.washingt[...]

2021-06-14

[109]

뉴스

China import concerns spur US to launch semiconductor supply chain review

https://www.reuters.[...]

2023-12-21

[110]

뉴스

US urges Taiwan to curb chip exports to China

https://www.ft.com/c[...]

2019-11-03

[111]

웹사이트

The True Impact of Allied Export Controls on the U.S. and Chinese Semiconductor Manufacturing Equipment Industries

https://www.csis.org[...]

2024-11-26

[112]

웹사이트

Understanding the Biden Administration’s Updated Export Controls

https://www.csis.org[...]

2024-12-11

[113]

웹사이트

VLSI Symposium - TSMC and Imec on Advanced Process and Devices Technology Toward 2nm

https://semiwiki.com[...]

2024-02-25

[114]

뉴스

Power outage partially halts Toshiba Memory's chip plant

https://www.reuters.[...]

2019-12-16

[115]

서적

Occupational Outlook Handbook

https://books.google[...]

JIST Publishing

2000-02-19

[116]

웹사이트

Water Scarcity and the Semiconductor Industry

http://large.stanfor[...]

[117]

PDF

https://www.st.com/r[...]

2024-08-00

[118]

서적

Handbook of Silicon Wafer Cleaning Technology

https://books.google[...]

William Andrew

2024-01-08

[119]

학술지

A Theoretical Analysis of Wafer Cleaning Using a Cryogenic Aerosol

https://iopscience.i[...]

2024-01-08

[120]

웹사이트

Wafer Cleaning Becomes Key Challenge In Manufacturing 3D Structures

https://semiengineer[...]

2022-10-20

[121]

서적

Cleaning and Surface Conditioning Technology in Semiconductor Device Manufacturing 11

https://books.google[...]

The Electrochemical Society

2009-09-30

[122]

서적

Handbook of Integrated Circuit Industry

https://books.google[...]

Springer

2023-11-27

[123]

학술지

An Investigation of Edge Bead Removal Width Variability, Effects and Process Control in Photolithographic Manufacturing

https://ieeexplore.i[...]

2022-02-00

[124]

웹사이트

What's Next For Atomic Layer Etch?

https://semiengineer[...]

2017-11-16

[125]

웹사이트

Epitaxy

https://semiengineer[...]

[126]

웹사이트

Unlocking the Potential of Molecular Beam Epitaxy

https://www.eetimes.[...]

AspenCore

2024-01-08

[127]

웹사이트

Ion beam deposition goes 300mm with Aviza's new tool

https://sst.semicond[...]

Gold Flag Media

2024-01-08

[128]

서적

2017 28th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC)

https://ieeexplore.i[...]

2017-00-00

[129]

서적

Plasma Processing for VLSI

https://books.google[...]

Academic Press

2014-12-01

[130]

서적

Aqueous Single Pass Single Wafer AI/Via Cleaning

https://books.google[...]

Electrochemical Society

2024-01-08

[131]

웹사이트

Laser Lift-Off(LLO) Ideal for high brightness vertical LED manufacturing - Press Release - DISCO Corporation

https://www.disco.co[...]

2019-05-26

[132]

웹사이트

Product Information | Polishers - DISCO Corporation

https://www.disco.co[...]

2019-05-26

[133]

웹사이트

Product Information | DBG / Package Singulation - DISCO Corporation

https://www.disco.co[...]

2019-05-26

[134]

웹사이트

Plasma Dicing (Dice Before Grind) | Orbotech

https://www.orbotech[...]

2022-01-00

[135]

웹사이트

Electro Conductive Die Attach Film(Under Development) | Nitto

https://www.nitto.co[...]

2019-05-26

[136]

웹사이트

Die Attach Film Adhesives

https://www.henkel-a[...]

2019-05-26

[137]

웹사이트

From a Slice of Crystal to an IC Wafer - CHM Revolution

https://www.computer[...]

[138]

웹사이트

The ASYST SMIF system - Integrated with the Tencor Surfscan 7200

https://www.chiphist[...]

2020-10-14

[139]

웹사이트

Study into human particle shedding

https://www.cleanroo[...]

2020-10-14

[140]

웹사이트

How a Chip Gets Made: Visiting GlobalFoundries

https://www.pcmag.co[...]

2023-11-23

[141]

서적

Microlithography: Science and Technology, Second Edition

https://books.google[...]

CRC Press

2018-10-03

[142]

웹사이트

Wafer Cleaning Procedures; Photoresist or Resist Stripping; Removal of Films and Particulates

https://www.eesemi.c[...]

2020-10-14

[143]

서적

Plasma Etching: Fundamentals and Applications

https://books.google[...]

OUP Oxford

1998-05-28

[144]

서적

Dry Etching Technology for Semiconductors

https://books.google[...]

Springer

2014-10-25

[145]

서적

Plasma Etching: Fundamentals and Applications

https://books.google[...]

OUP Oxford

1998-05-28

[146]

서적

III-Nitrides Light Emitting Diodes: Technology and Applications

https://books.google[...]

Springer Nature

2020-08-31

[147]

서적

Dry Etching for Microelectronics

https://books.google[...]

Elsevier

2012-12-02

[148]

서적

Fundamentals of Layout Design for Electronic Circuits

https://books.google[...]

Springer Nature

2020-03-19

[149]

서적

Etching in Microsystem Technology

https://books.google[...]

John Wiley & Sons

2008-07-11

[150]

뉴스

Highly Selective Etch Rolls Out For Next-Gen Chips

https://semiengineer[...]

2022-03-21

[151]

서적

Introduction to Microfabrication

https://books.google[...]

John Wiley & Sons

2005-01-28

[152]

웹사이트

1954: Diffusion Process Developed for Transistors | the Silicon Engine | Computer History Museum

https://www.computer[...]

[153]

서적

Semiconductor Microchips and Fabrication: A Practical Guide to Theory and Manufacturing

https://books.google[...]

John Wiley & Sons

2022-10-10

[154]

학회

Review of Major Innovations in Beam Line Design

https://www.axcelis.[...]

[155]

저널

History of Some Early Developments in Ion-Implantation Technology Leading to Silicon Transistor Manufacturing

http://www.eelab.usy[...]

2024-02-26

[156]

서적

Ion Implantation and Synthesis of Materials

Springer

2006

[157]

학회

Virtual Metrology Technique for Semiconductor Manufacturing

https://ieeexplore.i[...]

[158]

웹사이트

The Threat of Semiconductor Variability - IEEE Spectrum

https://spectrum.iee[...]

[159]

서적

Handbook of Semiconductor Manufacturing Technology

https://books.google[...]

CRC Press

2017-12-19

[160]

서적

Microelectronic Materials

https://books.google[...]

Routledge

2017-10-05

[161]

서적

Semiconductor Manufacturing Technology

https://books.google[...]

World Scientific Publishing Company

2008-03-03

[162]

서적

75th Anniversary of the Transistor

https://books.google[...]

John Wiley & Sons

2023-08-01

[163]

학회

High-k/metal gates in leading edge silicon devices

https://ieeexplore.i[...]

[164]

저널

High-K materials and metal gates for CMOS applications

2015

[165]

학회

High-k / metal gate innovations enabling continued CMOS scaling

2011

[166]

학회

Gate-first high-k/metal gate DRAM technology for low power and high performance products

https://ieeexplore.i[...]

[167]

웹사이트

Integrating high-k /metal gates: gate-first or gate-last? | Semiconductor Digest

https://sst.semicond[...]

[168]

웹사이트

IEDM 2009: HKMG gate-first vs gate-last options | Semiconductor Digest

https://sst.semicond[...]

[169]

뉴스

Tracing Samsung's Road to 14nm

https://www.eetimes.[...]

2015-05-12

[170]

서적

Complementary Metal Oxide Semiconductor

https://books.google[...]

BoD – Books on Demand

2018-08-01

[171]

뉴스

What's After FinFETs?

https://semiengineer[...]

2017-07-24

[172]

학회

2006 International Electron Devices Meeting

2006

[173]

학회

2007 International Workshop on Physics of Semiconductor Devices

2007

[174]

웹사이트

The High-k Solution - IEEE Spectrum

https://spectrum.iee[...]

[175]

학회

2007 IEEE Custom Integrated Circuits Conference

2007

[176]

서적

Technology of Integrated Circuits

https://books.google[...]

Springer

2013-03-09

[177]

웹사이트

BEOL Wiring Process for CMOS Logic

https://www.chiphist[...]

[178]

웹사이트

The Race To 10/7nm

https://semiengineer[...]

2017-05-22

[179]

서적

Chemical-Mechanical Planarization of Semiconductor Materials

https://books.google[...]

Springer

2004-01-26

[180]

서적

Copper Interconnect Technology

https://books.google[...]

Springer

2010-01-22

[181]

웹사이트

Introduction to Copper / Low-K Interconnects & Electromigration Fundamentals

https://www.research[...]

[182]

서적

Low- k Materials: Recent Advances

https://onlinelibrar[...]

Wiley

2012-02-24

[183]

학술지

Recent Advances in Barrier Layer of Cu Interconnects

https://doi.org/10.3[...]

2020

[184]

웹사이트

Ibm's Development of Copper Interconnect for Integrated Circuit

https://www.chiphist[...]

[185]

웹사이트

Cobalt Encapsulation Extends Copper to 10nm

https://www.eetimes.[...]

2014-05-13

[186]

학술지

Complex Refractive Index Spectra of CH3NH3PbI3 Perovskite Thin Films Determined by Spectroscopic Ellipsometry and Spectrophotometry

https://doi.org/10.1[...]

2021-11-16

[187]

학술지

Regression Methods for Virtual Metrology of Layer Thickness in Chemical Vapor Deposition

https://ieeexplore.i[...]

2015-11-09

[188]

서적

Cost Effective Integrated Circuit Manufacturing

https://smithsonianc[...]

Integrated Circuit Engineering Corporation

2023-01-22

[189]

웹사이트

Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020

https://www.anandtec[...]

2020-04-12

[190]

웹사이트

Advanced MOSFETs and Novel Devices

https://dokumente.un[...]

2020-10-23

[191]

웹사이트

Introduction to Semiconductor Technology

https://www.st.com/c[...]

2018-09-25

[192]

웹사이트

Wafer Backgrind

https://eesemi.com/b[...]

2020-12-18

[193]

웹사이트

Introduction to Semiconductor Technology

https://www.st.com/r[...]

2024-08-01

[194]

웹사이트

The post-fab process debate for 3D ICs: Foundry or OSATS

https://www.3dincite[...]

2009-04-30

[195]

웹사이트

ATMPs: The Founding Stone of India's Semiconductor Era

https://www.electron[...]

2022-01-19

[196]

웹사이트

U.S. Semiconductor Ecosystem Map

https://www.semicond[...]

2023-03-20

[197]

웹사이트

Mapping the Semiconductor Supply Chain: The Critical Role of the Indo-Pacific Region

https://www.csis.org[...]

2023-05-30

[198]

웹사이트

Why tech pollution's going global

https://www.cnet.com[...]

2024-02-17

[199]

서적

Epitaxial Silicon Technology

https://books.google[...]

Elsevier

2012-12-02

[200]

웹사이트

Abating Potentially Dangerous Particles 2.5 µm and Smaller

https://www.semicond[...]

2020-02-03

[201]

웹사이트

https://19january201[...]

[202]

웹사이트

Hi-tech without costing the Earth

https://cleanroomtec[...]

[203]

서적

半導体平坦化CMP技術―超LSI製造のキープロセス

工業調査会

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com